NBS SPECIAL PUBLICATION 400-]

Library, E-01 Admin. Bldg.

OCT 1 1981

191025

# Semiconductor Measurement Technology

**Quarterly Report**

July 1 to September 30, 1973

0 7 60-1 4 U.S. TMENT OF MERCE National Bureau of andards

#### NATIONAL BURFAU OF STANDARDS

The National Bureau of Standards' was established by an act of Congress March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau consists of the Institute for Basic Standards, the Institute for Materials Research, the Institute for Applied Technology, the Institute for Computer Sciences and Technology, and the Office for Information Programs.

THE INSTITUTE FOR BASIC STANDARDS provides the central basis within the United States of a complete and consistent system of physical measurement; coordinates that system with measurement systems of other nations; and furnishes essential services leading to accurate and uniform physical measurements throughout the Nation's scientific community, industry, and commerce. The Institute consists of a Center for Radiation Research, an Office of Measurement Services and the following divisions:

Applied Mathematics — Electricity — Mechanics — Heat — Optical Physics — Nuclear Sciences <sup>2</sup> — Applied Radiation <sup>2</sup> — Quantum Electronics <sup>3</sup> — Electromagnetics <sup>3</sup> — Time and Frequency <sup>3</sup> — Laboratory Astrophysics <sup>3</sup> — Cryogenics <sup>3</sup>.

THE INSTITUTE FOR MATERIALS RESEARCH conducts materials research leading to improved methods of measurement, standards, and data on the properties of well-characterized materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; and develops, produces, and distributes standard reference materials. The Institute consists of the Office of Standard Reference Materials and the following divisions:

Analytical Chemistry — Polymers — Metallurgy — Inorganic Materials — Reactor Radiation — Physical Chemistry.

THE INSTITUTE FOR APPLIED TECHNOLOGY provides technical services to promote the use of available technology and to facilitate technological innovation in industry and Government; cooperates with public and private organizations leading to the development of technological standards (including mandatory safety standards), codes and methods of test; and provides technical advice and services to Government agencies upon request. The Institute consists of a Center for Building Technology and the following divisions and offices:

Engineering and Product Standards — Weights and Measures — Invention and Innovation — Product Evaluation Technology — Electronic Technology — Technical Analysis — Measurement Engineering — Structures, Materials, and Life Safety — Building Environment — Technical Evaluation and Application — Fire Technology.

THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY conducts research and provides technical services designed to aid Government agencies in improving cost effectiveness in the conduct of their programs through the selection, acquisition, and effective utilization of automatic data processing equipment; and serves as the principal focus within the executive branch for the development of Federal standards for automatic data processing equipment, techniques, and computer languages. The Institute consists of the following divisions:

Computer Services — Systems and Software — Computer Systems Engineering — Information Technology.

THE OFFICE FOR INFORMATION PROGRAMS promotes optimum dissemination and accessibility of scientific information generated within NBS and other agencies of the Federal Government; promotes the development of the National Standard Reference Data System and a system of information analysis centers dealing with the broader aspects of the National Measurement System; provides appropriate services to ensure that the NBS staff has optimum accessibility to the scientific information of the world. The Office consists of the following organizational units:

Office of Standard Reference Data — Office of Information Activities — Office of Technical Publications — Library — Office of International Relations.

<sup>&</sup>lt;sup>1</sup>Headquarters and Laboratories at Gaithersburg, Maryland, unless otherwise noted; mailing address Washington, D.C. 20234.

<sup>&</sup>lt;sup>2</sup> Part of the Center for Radiation Research.

Located at Boulder, Colorado 80302.

<sup>4</sup> Part of the Center for Building Technology.

# Semiconductor Measurement Technology

Quarterly Report, July 1 to September 30, 1973

400-1

National Bureau of Standards MAY 6 1974

W. Murray Bullis, Editor

Electronic Technology Division Institute for Applied Technology National Bureau of Standards Washington, D.C. 20234 C. 2

Jointly Supported by: The National Bureau of Standards, The Defense Nuclear Agency, and The Defense Advanced Research Projects Agency

U.S. DEPARTMENT OF COMMERCE, Frederick B. Dent, Secretary NATIONAL BUREAU OF STANDARDS, Richard W. Roberts, Director

Issued March 1974

Library of Congress Catalog Number: 74-600040

National Bureau of Standards Special Publication 400-1

Nat. Bur. Stand. (U.S.), Spec. Publ. 400-1, 68 pages (Mar. 1974)

CODEN: XNBSAV

U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1974

# TABLE OF CONTENTS

## SEMICONDUCTOR MEASUREMENT TECHNOLOGY

| I                                                              | PAGE |

|----------------------------------------------------------------|------|

| Preface                                                        | viii |

| 1. Introduction                                                | 1    |

| 2. Highlights                                                  | 3    |

| 3. Resistivity; Dopant Profiles                                | 6    |

| 3.1. Spreading Resistance Methods                              | 6    |

| 3.2. Junction Capacitance-Voltage Method                       | 6    |

| 3.3. Mathematical Models of Doping Profiles                    | 9    |

| 3.4. Diffused Layer Sheet Resistance                           | 11   |

| 3.5. Silicon Resistivity Standards                             | 12   |

| 4. Crystal Defects and Contaminants                            | 16   |

| 4.1. Thermally Stimulated Current and Capacitance Measurements | 16   |

| 4.2. Energy Level Model for Gold-Doped Silicon                 | 19   |

| 5. Insulator Films                                             | 20   |

| 6. Test Patterns                                               | 22   |

| 6.1. Process Development                                       | 22   |

| 6.2. Metal-To-Base Contact Resistor Study                      | 22   |

| 7. Photolithography                                            | 26   |

| 7.1. Introduction                                              | 26   |

| 7.2. Mask Inspection                                           | 26   |

| 7.3. Photoresist Materials                                     | 26   |

| 8. Metallization                                               | 28   |

| 9. Wafer Inspection and Test                                   | 31   |

| O. Die Attachment                                              | 32   |

| 0.1. Heat Flow Analysis                                        | 32   |

| 0.2. Void Detection in Transistor Die Attachment               | 32   |

| 0.3. Summary                                                   | 33   |

| 1. Interconnection Bonding                                     | 35   |

| 1.1. Metallurgical Systems for Ultrasonic Bonding              | 35   |

| 1.2. Burn-out Characteristics of Fine Bonding Wire             | 35   |

| 1.3. Dissemination Activities                                  | 39   |

| 2. Hermeticity                                                 | 40   |

| 3. Thermal Properties of Devices                               | 41   |

| 3.1. Thermal Resistance Methods                                | 41   |

|                                                                |      |

## TABLE OF CONTENTS

|                                     |                   |          |            |          |     | PA |

|-------------------------------------|-------------------|----------|------------|----------|-----|----|

| 13.2. Analysis                      |                   |          |            | <br>     |     | 41 |

| 13.3. Standardization Activi        | ies               |          |            | <br>     | • • | 4: |

| 14. Microwave Diodes                |                   |          |            | <br>     |     | 4. |

| 14.1. Repeatability Studies         |                   |          |            | <br>     |     | 40 |

| 14.2. Radiation Hardness Stud       | ly                |          |            | <br>     |     | 41 |

| 15. High-Frequency Measuremen       | nts               |          |            | <br>     |     | 4. |

| 16. References                      |                   |          |            | <br>     |     | 49 |

| Appendix A. Semiconductor Technolog | y Program Staff   |          |            | <br>•. • |     | 51 |

| Appendix B. Semiconductor Technolog | y Program Publica | ations . |            | <br>     |     | 5. |

| Appendix C. Workshop and Symposium  | Schedule          |          | • • • • \• | <br>     |     | 5: |

| Appendix D. Standards Committee Act | ivities           |          |            | <br>     |     | 5€ |

| Appendix E. Solid-State Technology  | & Fabrication Ser | rvices . |            | <br>     |     | 5{ |

# LIST OF FIGURES

|           |                                                                                                                                                                                                                                                                                                                                           | PAG. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

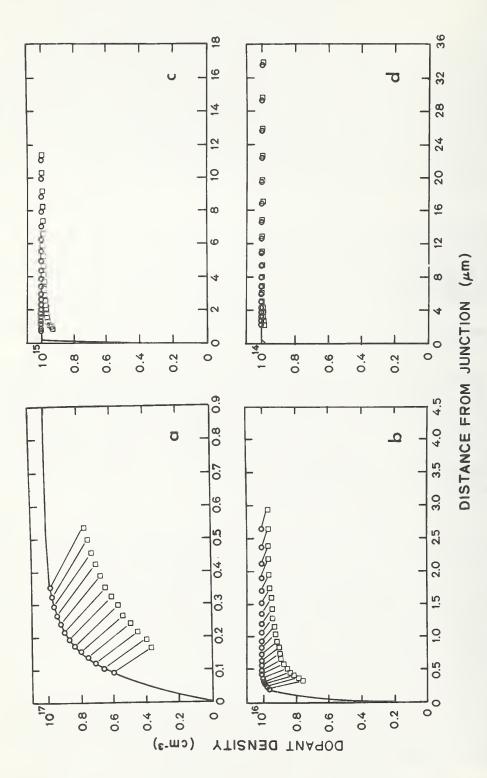

| l.        | Dopant density profiles on the heavily- and lightly-doped sides of a $p$ - $n$ junction as determined from idealized C-V data modified to simulate a random, normally distributed error with standard deviation of 0.05 percent in the measurement of C and V                                                                             | 7    |

| 2.        | Dopant density profiles on the lightly-doped side of a $p-n$ junction as determined from idealized C-V data corrected and not corrected to take account of the penetration of the space charge layer on the heavily-doped side                                                                                                            | 8    |

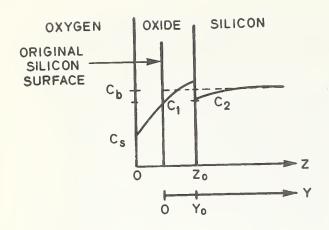

| 3.        | Schematic diagram of dopant distribution in silicon-oxide structure showing both laboratory coordinate, y, and moving coordinate, z                                                                                                                                                                                                       | 10   |

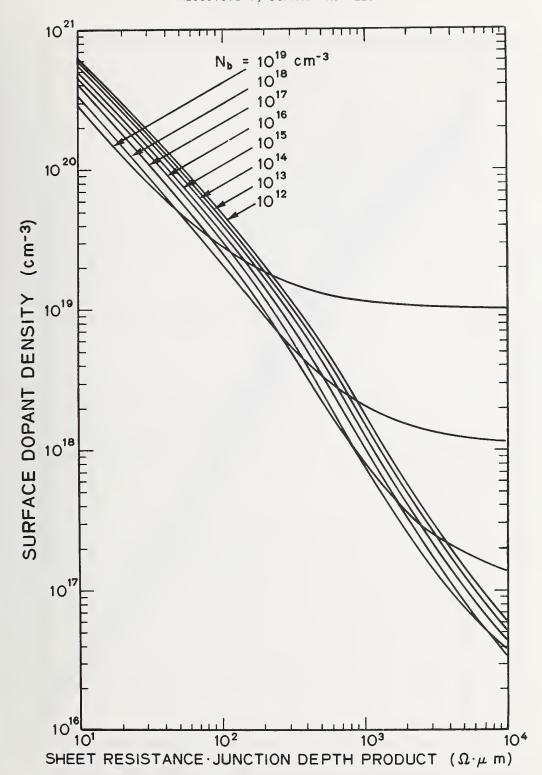

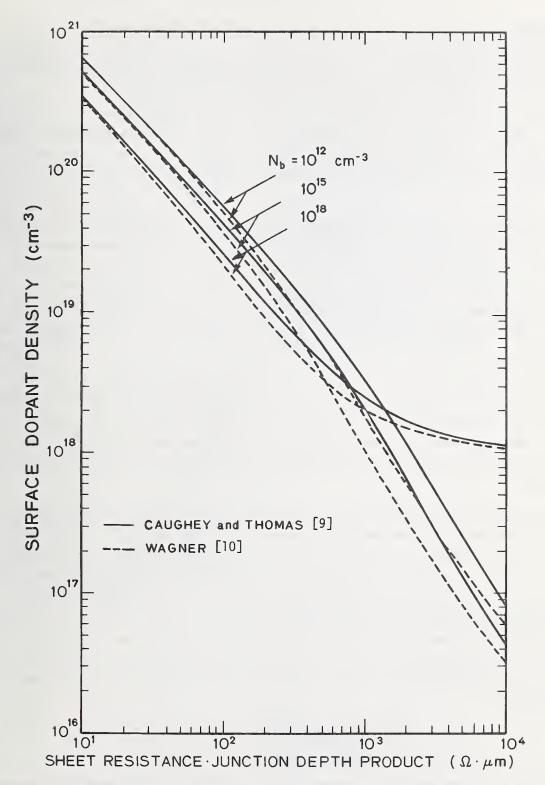

| ١.        | Surface dopant density of a $p$ -type Gaussian diffused layer in uniformly doped $n$ -type silicon as a function of the product of sheet resistance and junction depth for various background dopant densities, $\mathbb{N}_{b}$                                                                                                          | 13   |

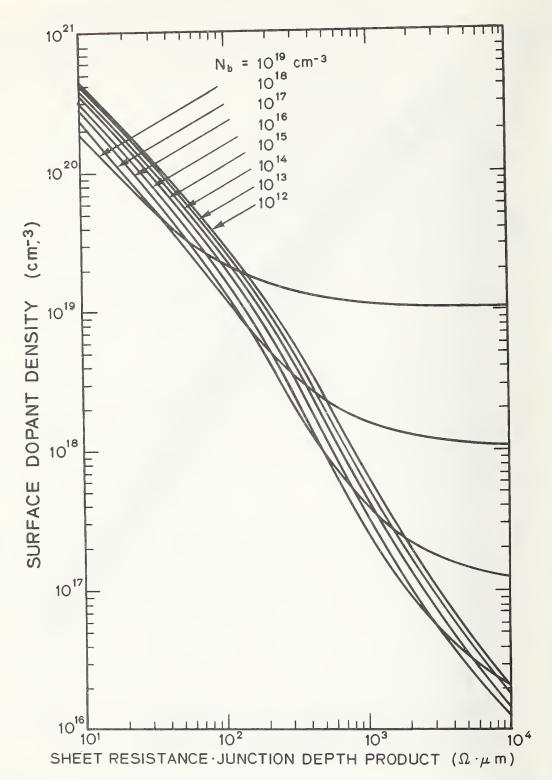

| 5.        | Surface dopant density of an $n$ -type Gaussian diffused layer in uniformly doped $p$ -type silicon as a function of the product of sheet resistance and junction depth for various background dopant densities, $N_{\rm b}$                                                                                                              | 14   |

| <b>5.</b> | Surface dopant density of a $p$ -type Gaussian diffused layer in uniformly doped $n$ -type silicon as a function of the product of sheet resistance and junction depth for various background dopant densities, $N_b$ , showing the effect of using different relationships between hole mobility and impurity density in the calculation | 15   |

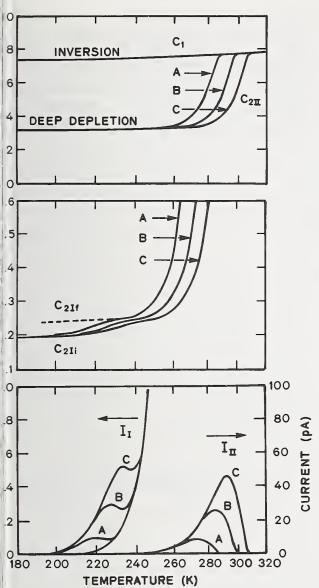

| 7.        | Dynathermal response of a gold-doped silicon <i>n</i> -MOS capacitor showing features due to the gold acceptor                                                                                                                                                                                                                            | 17   |

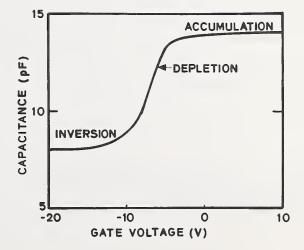

| 3.        | Isothermal, equilibrium, high-frequency capacitance response of a gold-doped silicon $n$ -MOS capacitor measured at room temperature                                                                                                                                                                                                      | 17   |

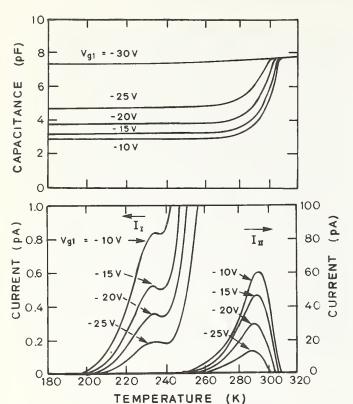

|           | Dynathermal response of a gold-doped silicon $n$ -MOS capacitor showing phase I current and phase II current and capacitance response of the gold acceptor as a function of initial gate voltage, $V_{g1}$ , for a heating rate of 9.3 K/s and final gate voltage of -30 V                                                                | 18   |

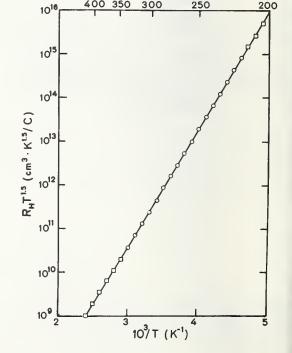

|           | Hall effect activation energy plot for the gold acceptor in $n$ -type silicon                                                                                                                                                                                                                                                             | 18   |

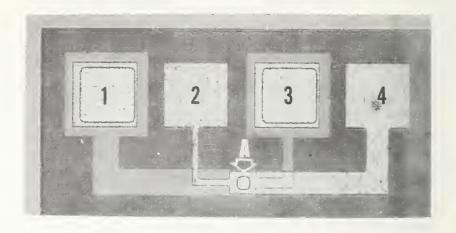

| •         | Photomicrograph of the metal-to-base contact resistor, test structure  No. 16 of test pattern NBS-2                                                                                                                                                                                                                                       | 24   |

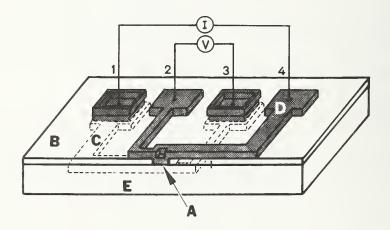

| •         | Schematic view of a section through the contact window of the metal-to-base contact resistor test structure pictured in figure 11                                                                                                                                                                                                         | 24   |

## LIST OF FIGURES

|     |                                                                         | 111 |

|-----|-------------------------------------------------------------------------|-----|

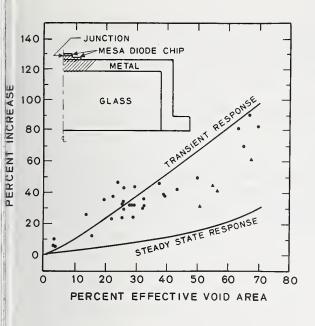

| 13. | Percent increase in junction-to-case temperature difference of diodes   |     |

|     | with voids over that of their respective controls measured under steady |     |

|     | state and transient conditions as a function of percent effective void  |     |

|     | area in the diode die attachment                                        | 33  |

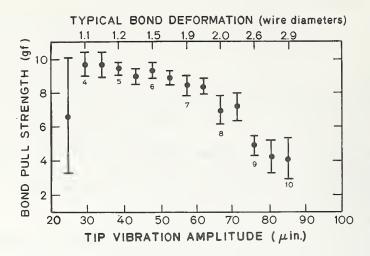

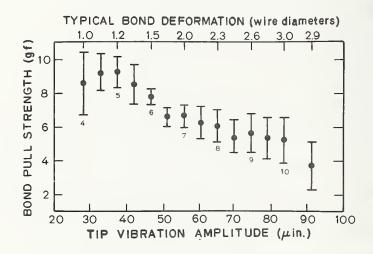

| 14. | Bond pull strength of ultrasonically bonded, 1-mil diameter aluminum    |     |

|     | wire, single-level, double bonds as a function of the peak-to-peak      |     |

|     | vibration amplitude of the bonding tool tip                             | 36  |

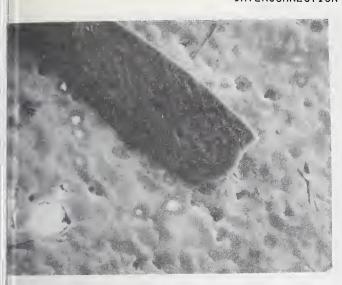

| 15. | Scanning electron micrograph of the surface of the thick-film gold      |     |

|     | metallization used in these ultrasonic bonding experiments              | 37  |

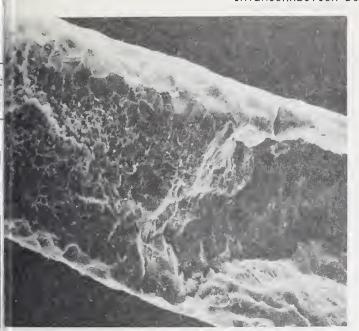

| 16. | Scanning electron micrograph of a 5-mil diameter aluminum wire after    |     |

|     | burn out on heating to about 1100°C for 3 min showing the oxide         |     |

|     | surface coating                                                         | 30  |

# LIST OF TABLES

|    |                                                                         | PAGE |

|----|-------------------------------------------------------------------------|------|

| 1. | Mobility Equation Constants                                             | 12   |

| 2. | Measurements on Test Pattern NBS-2; Run No. 2.3                         | 23   |

| 3. | Burn-Out Current for 10-mm Length of Gold Wire                          | 37   |

| 4. | Burn-Out Current for 10-mm Length of Aluminum Wire                      | 38   |

| 5. | Comparison of Infrared and Electrical Thermal Resistance Measurements   | 43   |

| 6. | Comparison of Infrared and Electrical Thermal Resistance Measurements   |      |

|    | for the Round-Robin Test Devices                                        | 43   |

| 7. | Change in Conversion Loss on Repetitive Measurements of 1N23-Equivalent |      |

|    | Schottky-Barrier Diodes                                                 | 45   |

| 8. | Change in Conversion Loss on Repetitive Measurements of 1N23-Equivalent |      |

|    | Schottky-Barrier Diodes Selected for Radiation Hardness Study           | 45   |

| 9. | Variability of Typical S-Parameter Measurements                         | 48   |

The Semiconductor Technology Program serves to focus NBS efforts to enhance the performance, interchangeability, and reliability of discrete semiconductor devices and integrated circuits through improvements in measurement technology for use in controlling device fabrication processes and in specifying materials and devices in national and international commerce. Its major thrusts are the development of carefully evaluated and well documented test procedures and associated technology, for use on production lines and in the exchange of devices and materials, and the dissemination of such information to the electronics community. Application of the output by industry is expected to contribute to higher yields, lower cost, and higher reliability of semiconductor devices. In addition, the improvements in measurement technology will lead to greater economy in government procurement and will provide a basis for controlled improvements in fabrication processes and in essential device characteristics.

The Program receives direct financial support principally from three major sponsors: the Defense Advanced Research Projects Agency (ARPA), the Defense Nuclear Agency (DNA), and the National Bureau of Standards (NBS). The ARPA-supported portion of the Program, Advancement of Reliability, Processing, and Automation for Integrated Circuits with the National Bureau of Standards (ARPA/IC/NBS), addresses critical Defense Department problems in the yield, reliability, and availability of integrated circuits. The DNA-supported portion of the Program emphasizes aspects of the work which relate to radiation response of electron devices for use in military systems. There is considerable overlap between the interests of DNA and ARPA and both interests parallel the measurement-oriented mission of NBS.

Cooperation with industrial users and suppliers of semiconductor devices is achieved through NBS participation in standardizing organizations; through direct consultations with device and material suppliers, government agencies, and other users; and through periodicall scheduled symposia and workshops. In addition, progress reports, such as this one, are regularly prepared for issuance in the NBS Special Publication 400 sub-series. More detaile reports such as state-of-the-art reviews, literature compilations, and summaries of technica efforts conducted within the Program are issued as these activities are completed. Reports of this type which are published by NBS also appear in the Special Publication 400 sub-serie Announcements of availability of all publications in this sub-series are sent by the Government Printing Office to those who have requested this service. A request form for this purpose may be found at the end of this report.

Through ARPA Order 2397, Program Code 4D10 (NBS Cost Center 4259555).

Through Inter-Agency Cost Reimbursement Order 74-811 (NBS Cost Center 4259522).

Through Scientific and Technical Research Services Cost Centers 4251126, 4252128, and 4254115.

# QUARTERLY REPORT JULY 1 TO SEPTEMBER 30, 1973

Abstract: This quarterly progress report, twenty-first of a series, describes NBS activities directed toward the development of methods of measurement for semiconductor materials, process control, and devices. Principal accomplishments during this reporting period include (1) extension of the technique for measuring thermally stimulated current and capacitance to include measurements on MOS capacitors, (2) completion of the development of the thermal response method for evaluation of transistor die attachment, (3) analysis of the interlaboratory comparison of transistor scattering parameter measurements, (4) preliminary review of measurement problems in the photolithographic aspects of semiconductor device processing, of problems associated with certain hermeticity testing procedures, and of methods for evaluating metallization step coverage, and (5) initiation of new activity on characterization of oxide films in MOS structures and analysis of diffusion profiles. Results are also reported on spreading resistance, capacitance-voltage, and sheet resistance measurements; the activation energy of the gold acceptor in silicon; evaluation of the base-to-metal contact resistor test structure; metallurgical systems for ultrasonic bonding; burn-out characteristics of fine gold and aluminum bonding wire; transistor thermal resistance measurements; and microwave diode conversion loss measurements. Supplementary data concerning staff, publications, workshops and symposia, standards committee activities, and technical services are also included as appendices.

Key Words: Contact resistance; die attachment; dopant profiles; electrical properties; electronics; gold-doped silicon; hermeticity; metallization; methods of measurement; microelectronics; microwave diodes; mobility; MOS devices; oxide films; photomasks; photoresist; resistivity; resistivity standards; scanning electron microscopy; semiconductor devices; semiconductor materials; semiconductor process control; sheet resistance; silicon; S-parameters; spreading resistance; test patterns; thermal resistance; thermally stimulated capacitance; thermally stimulated current; wire bonds.

## 1. INTRODUCTION

This is the twenty-first quarterly report to the sponsors of the Semiconductor Technol-Program. It summarizes work on a wide variety of measurement methods for semiconductor terials, process control, and devices that are being studied at the National Bureau of andards. The Program is a continuing one, and the results and conclusions reported here subject to modification and refinement.

The work of the Program is divided into a number of tasks, each directed toward the dy of a particular material or device property or measurement technique. This report is divided according to these tasks. Highlights of activity during the quarter are given in tion 2. Subsequent sections deal with each specific task area. References cited are ted in the final section of the report.

#### INTRODUCTION

The report of each task includes a narrative description of progress made during this reporting period. Additional information concerning the material reported may be obtained directly from individual staff members identified with the task in the report. The organization of the Program staff and telephone numbers are listed in Appendix A.

Background material on the Program and individual tasks may be found in earlier quarterly reports as listed in Appendix B. From time to time, publications are prepared which describe some aspect of the program in greater detail. Current publications of this type are also listed in Appendix B. Reprints or copies of such publications are usually available on request to the author.

Communication with the electronics community is a critical aspect both for receiving guidance in planning future program activities and for disseminating results of the work to potential users. Formal channels for such communication occur in the form of workshops and symposia sponsored or co-sponsored by NBS. Currently scheduled seminars and workshops are listed in Appendix C. In addition, the availability of proceedings from past workshops and seminars is indicated in the appendix.

An important part of the work that frequently goes beyond the task structure is participation in the activities of various technical standardizing committees. The list of personnel involved with this work given in Appendix D suggests the extent of this participation In many cases, details of standardization efforts are reported in connection with the work of a particular task. Current standardization activities, including those not associated with a particular task, are summarized at the end of section 2.

Technical services in areas of competence are provided to other NBS activities and other government agencies as they are requested. Usually these are short-term, specialized services that cannot be obtained through normal commercial channels. To indicate the kinds of technology available to the program such services provided during the period covered by this report are listed in Appendix E.

## 2. HIGHLIGHTS

Considerable expansion in the scope of the program occurred during this reporting period h the inclusion of a new effort on Advancement of Reliability, Processing, and Automation Integrated Circuits with the National Bureau of Standards (ARPA/IC/NBS) funded by the ense Advanced Research Projects Agency. New tasks were established in the areas of insuor films, photolithography, and hermeticity.

Significant technical accomplishments during this reporting period included:

- extension of the technique for measuring thermally stimulated current and capacitance to include measurements on metal-oxide-semiconductor (MOS) capacitors,

- completion of the development of the thermal response method for evaluation of transistor die attachment,

- analysis of the interlaboratory comparison of transistor scattering parameter measurements, and

- 4. preliminary review of measurement problems in the photolithographic aspects of semiconductor device processing, of problems associated with certain hermeticity testing procedures, and of methods for evaluating metallization step coverage.

In addition, the first of a series of workshops to aid in communication with the elecnics community was held. This workshop, on measurement needs for controlling integrated

cuit processing and assembly, had the dual objectives of formally announcing the

'A/IC/NBS program to the semiconductor industry and of giving the industry a forum to prole additional input for use in program definition and planning. The results of the workp are reported in detail elsewhere [1].

Following are highlights of other activities during this quarter.

Resistivity, Dopant Characterization — Development of calibration curves for the NBS reading resistance system continued with generation of the curve for n-type silicon in the tige 0.1 to 100  $\Omega$ ·cm. Theoretical study of the application of the junction capacitance—tage method for measuring diffusion profiles continued with evaluation of the effect of adom errors in the measured values of capacitance and voltage on the derived net dopant issity on either side of the junction. Mathematical analysis of the boron redistribution oblem began with formulation of the problem for both uniform and nonuniform initial distributions. The effect of uncertainty in mobility value on diffusion profiles derived from a remental sheet resistance measurements was studied by comparing results obtained with the softwo different relationships for hole mobility as a function of impurity density in type silicon. A multipass round-robin experiment between NBS and six experienced laboraties was designed to test the stability and multilaboratory precision to be expected from the silicon resistivity standard reference materials now available.

<u>Crystal Defects and Contaminants</u> — The dynathermal current and capacitance responses a gold-doped n-MOS capacitor were found to display two distinct features: one, which is

similar to the feature in the junction response, is characteristic of electron emission from the gold acceptor, and a second at higher temperature, which is not found in the junction response, is characteristic of hole emission from the gold acceptor. Additional Hall effect measurements on a specimen of n-type silicon with a phosphorus density about  $10^{15}$  cm<sup>-3</sup> and a gold density about three times greater yielded an activation energy within less than 1 meV of that obtained earlier on a less heavily doped specimen.

<u>Insulator Films</u> — Studies of silicon oxide films by ion microprobe mass analysis, electron spectroscopy for chemical analysis, and Auger spectroscopy are being initiated. Apparatus is being designed and constructed for use in studying the bias-temperature stress test for characterizing oxide stability. At the request of one of the major sponsors, a program has been initiated to document procedures and tests necessary to achieve radiation-hardened MOS integrated circuits.

<u>Test Patterns</u> — Several modifications were made in the processing procedure as part of a continuing task to demonstrate the application of test patterns in improving and controlling fabrication processes. Although some improvements were made, further iterations are needed to achieve desired values for various characteristics. Study of the metal-to-base contact resistor test structure showed that although the normalization of the measured contact resistance is uncertain, this structure is suitable for identifying deviations from nominal values of contact resistance which might occur in a production run.

<u>Wafer Inspection and Test</u> — Construction was begun of an optical flying-spot scanner for use in evaluating damage to device structures during inspection or test with a scanning electron microscope.

<u>Interconnection Bonding</u> — Characterization of metallurgical systems for ultrasonic bonding continued with confirmation of the previously reported high bond strength for gold wire on aluminum pads, tentative establishment of suitable bonding conditions for gold wire on gold thick-film metallization, and determination of compatible schedules for bonding aluminum wire both to aluminum thin-film bonding pads on silicon dioxide over silicon and to gold thick-film metallization on alumina substrates. A brief study was carried out on the burn out of fine gold and aluminum wire as a result of Joule heating. In addition to the technical effort, dissemination of the methods and technology developed for controlling and testing ultrasonic wire bonding continued at a high level throughout this period.

Thermal Properties of Devices — Repeatability tests of the emitter-base voltage, emitter-only switching technique for measuring thermal resistance of transistors were completed. Additional calculations with a somewhat more complex model were carried out to establish an appropriate extrapolation procedure for use in analyzing thermal resistance measurements; as in the simpler case, a plot of the logarithm of surface temperature as a function of time results in the most nearly straight lines over the appropriate range of delay times.

Microwave Diodes — Additional repeatability studies of the conversion loss measurement stem were made using Schottky-barrier mixer diodes. Groups of diodes were selected for a study of the effect of gamma and neutron irradiation on the noise characteristics these diodes.

<u>Standardization Activities</u> — Fifteen staff members participated in the fall meetings ASTM Committee F-1 on Electronics, held in Palo Alto, California, on September 5-7. Most so assisted with the first ARPA/NBS Workshop, held on the final day of the Committee etings.

Editorial work was carried out on five ASTM Committee F-1 draft documents and was itiated on an EIA-JEDEC document. Two documents were reviewed technically for other andards groups. Work continued on two round-robin experiments being conducted by ASTM mmittee F-1.

<u>Dissemination Activities</u> — Organizational activities were undertaken for a workshop on diation Effects in MOS Technology. This workshop, cosponsored by the IEEE Nuclear and asma Sciences Society, the IEEE Electron Devices Group, and NBS, is scheduled for December and 7, 1973, at Washington, D. C. No proceedings of this Workshop are to be printed.

Planning activity also continued for the Spreading Resistance Symposium, scheduled for ne 13-14, 1974, at Gaithersburg, Maryland (NBS Tech. Note 788, p. 64). This symposium is sponsored by ASTM Committee F-1 and NBS. It will immediately follow the June meeting of e committee.

Hermeticity was selected as the subject of the second ARPA/NBS Workshop, which is heduled to be held on March 29, 1974, at Gaithersburg, Maryland. Topic areas to be dissed include failure due to leaks (correlation of leak rate and failure, failure mechanisms, ntamination analysis, and nature of leaks) and evaluation and intercomparison of leak rate asurement procedures (helium mass spectrograph, radioisotope, and new methods).

The third ARPA/NBS Workshop was tentatively scheduled for September 5 and 6 in Scottsle, Arizona. The subject of this Workshop is design, evaluation, and use of test patterns. is designed to follow and supplement an informal mini-symposium on test patterns planned r the January meeting of ASTM Committee F-1 in New Orleans.

## 3. RESISTIVITY; DOPANT PROFILES

## 3.1. Spreading Resistance Methods

In preparation for constructing a calibration curve for phosphorus-doped silicon, a series of wafers was screened for radial uniformity using the spreading resistance instrument. Each wafer was freshly chem-mechanically polished on the surface to be probed by spreading resistance and lapped on the opposite side. Four-probe resistivity measurements were made on the lapped surface of 13 wafers which showed less than 10 percent variation in spreading resistance within the central half-radius region. These had room temperature resistivity in the range from about 0.1 to  $100~\Omega \cdot \text{cm}$ . There was a linear relationship between spreading resistance and resistivity as measured by the four-probe method, but there were discrepancies of as much as 30 percent from the line of regression. No further work will be undertaken until a more complete set of specimens of n-type material is available to fill out the calibration curve.

Discrepancies of 50 to 80 percent in the calibration of spreading resistance for high resistivity boron-doped wafers, previously reported, have not yet been explained. A set of wafers adjacent to those which yielded some of the most discrepant points previously observed in this p-type material was prepared by the same chem-mechanical polishing treatment as before but measurement of these wafers has not yet been completed.

(J. R. Ehrstein and D. R. Ricks)

## 3.2. Junction Capacitance-Voltage Method

Theoretical investigation continued into the feasibility of using capacitance-voltage (C-V) measurements to profile a layer diffused into homogeneous background material. Previously, it was shown that this method requires the background dopant density,  $N_{

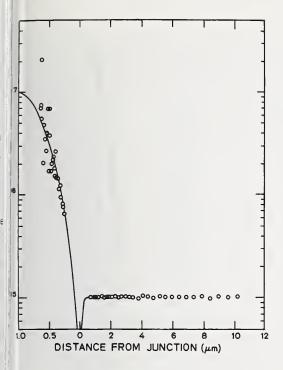

m h}$ , to be known to 1 percent or better in order to obtain a reasonably accurate diffused-layer profile (NBS Tech. Note 806, pp. 10-12). In the present phase, effects of variation in measurement of capacitance and voltage on the profile were studied. As an illustration, idealized C-V data corresponding to junction voltage between 0.3 V forward bias and 100 V reverse bias were generated for the case of a Gaussian diffusion in which the surface dopant density,  $N_0$ , was  $10^{17}~\rm cm^{-3}$ , the junction depth,  $X_i$ , was 1.0  $\mu m$ , and  $N_b$  was  $10^{15}~\rm cm^{-3}$ . relative capacitance interval,  $\Delta C/C$ , was taken to be 10 percent around zero bias, decreasing to 6 percent at large reverse bias. These ideal data were permuted using random numbers to simulate a measurement error of 0.1 percent (two standard deviations) in both C and V. No systematic error was assumed. These permuted data were then processed to compute dopant profiles on both the lightly-doped (homogeneous) and the heavily-doped (diffused-layer) sides of the p-n junction. A composite of these profiles is shown in figure 1. It can be seen that the scatter in the diffused-layer profile significantly exceeds that of the profile on the homogeneous side. Larger and more commonly encountered errors in C would increase the scatter of both profiles but would have a more pronounced effect on the diffusedlayer profile. For the conditions considered here the practical range over which one can profile a diffused layer is limited to dopant densities between 6 and 30 times the

Figure 1. Dopant density profiles on the heavily- and lightly-doped sides of a p-n junction as determined from idealized C-V data modified to simulate a random, normally distributed error with standard deviation of 0.05 percent in the measurement of C and V. (The doping density profile on the heavily-doped side was assumed to be Gaussian with surface doping density of  $10^{17}$  cm<sup>-3</sup> and junction depth of 1.0  $\mu$ m as shown by the solid curve to the left of the origin. One point on the heavily-doped side of the junction, 2.28  $\times$   $10^{18}$  cm<sup>-3</sup> at 0.6  $\mu$ m, fell outside the range of the plot. The doping density on the lightly-doped side was taken as  $10^{15}$  cm<sup>-3</sup>.)

kground dopant density. In this range the measured value of the diffused-layer dopant sity is within a factor of two of the true value.

In addition to errors introduced by measurement error in the capacitance and the relae capacitance ratio, which have been considered by Amron [2], the error in the computed fused-layer profile is increased by the interaction of these two effects with the differe of large numbers called for in the data reduction algorithm. The net dopant density, ), on the heavily-doped side of the junction at the edge of the space-charge region which penetrated a distance A from the junction is [3]

$$N(A)^{-1} = N(W)^{-1} - N(B)^{-1}$$

(1)

re the total space-charge width W = A + B and N(B) is the net dopant density on the htly-doped side of the junction at the edge of the space-charge region which has penetrated istance B from the junction. The quantities derived from capacitance-voltage values are ) and W. When N(A) becomes large compared to N(B), as in the case of an abruptly diffused ction, N(B) and B approach N(W) and W, respectively. In the data reduction algorithm, ) and B are estimated. As N(B) and B approach N(W) and W, respectively, the calculated ues of N(A) and A become much less reliable.

A theoretical study was also made of the error found in the profile of the lightlyived side of various diffused junctions when the diffused-layer correction [3] is not apived. Such information is useful in quantifying these errors and in providing guidelines

if developing diffusion schedules which will minimize the need for these corrections.

The diffused-layer correction accounts for the fact that the space-charge layer penetites not only the lightly-doped side of the junction but also the heavily-doped diffused

side. (The dopant density profile on the heavily-doped side was assumed to be Gaussian with surface dopant density of  $10^{19}$  cm<sup>-3</sup> and junction depth of 1.0  $\mu$ m. The dopant density on the lightly doped side was taken as  $10^{17}$  cm<sup>-3</sup> (a),  $10^{15}$  cm<sup>-3</sup> (b),  $10^{15}$  cm<sup>-3</sup> (c), and  $10^{14}$  cm<sup>-3</sup> (d).) corrected (O) and not corrected (O) to take account of the penetration of the space charge layer on the heavily-doped Dopant density profiles on the lightly-doped side of a p-n junction as determined from idealized C-V data Figure 2.

yer. As above, the junctions were assumed to be formed by a Gaussian diffusion into iformly-doped background material. The junction depth,  $X_j$ , was taken as 1.0  $\mu$ m and the rface dopant density,  $N_0$ , was taken as  $10^{19}$  cm<sup>-3</sup>. Corrected and uncorrected profiles were lculated from idealized C-V data for which the voltage ranged from 0.3 V forward bias to eakdown or 100 V (whichever is smaller) and for which the capacitance was decremented apoximately 10 percent for each successive C-V data pair. Profiles calculated for backound dopant densities,  $N_b$ , of  $10^{14}$ ,  $10^{15}$ ,  $10^{16}$  and  $10^{17}$  cm<sup>-3</sup> are shown in figure 2.

The uncorrected profiles, N(W) vs. W, are represented by squares, and the corrected ofiles, N(B) vs. B, are represented by circles. Connecting lines join data points obined from the same C-V data pair. Note that the uncorrected profiles give erroneously low lues of dopant density which gradually approach the correct N<sub>b</sub> value at large distances om the junction. Note also that the uncorrected profiles give erroneously large values r the distance from the junction. This is important when profiling epitaxial layers, for causes the epitaxial-substrate interface to appear farther from the junction than it tually is. Also illustrated is the fact that the errors increase as N<sub>b</sub> approaches N<sub>O</sub>.

The profiles of figure 2 are valid for both  $p^{\dagger}n$  or  $n^{\dagger}p$  junctions. Peripheral effects ve been neglected and dopant impurities were assumed to be fully ionized. When calculating the capacitance and voltage, the dielectric constant of silicon was assumed constant that value  $1.036 \times 10^{-12}$  F/cm and the built-in voltage was taken as 0.7 V. For materials that different dielectric constant, the respective loci of the N(W) vs. W and N(B) vs. B rives would be unchanged, but a particular point on a locus would correspond to a different pacitance-voltage pair.

(R. L. Mattis and M. G. Buehler)

### 3. Mathematical Models of Doping Profiles

To couple laboratory efforts on production and measurement of doping profiles in silin, a mathematical study of the diffusion and oxidation processes was begun. The initial ase is directed toward solution of the problem of redistribution of impurities during the idation of silicon considering both uniform and nonuniform initial impurity distributions the silicon.

When a silicon wafer is thermally oxidized, silicon comes from the wafer to form the licon dioxide. This means that during the oxidation, the silicon surface moves with reect to its original position. As oxidation proceeds, dopant atoms in the silicon are in sence either rejected from the oxide or incorporated into the oxide. This effect causes pant atoms to be redistributed within the silicon.

A mathematical description of the physical processes involved in this redistribution oblem has been given elsewhere [4-7]. These authors consider the dopant impurities to be sentially uniformly distributed in the silicon prior to oxidation. It is the purpose of e present study to use numerical methods to solve for the final dopant profiles where sitially the dopants are either uniformly or nonuniformly distributed within the silicon.

Figure 3. Schematic diagram of dopant distribution in silicon-oxide structure showing both laboratory coordinate, y, and moving coordinate, z.

As in previous work [4-7], the silicon is treated mathematically as a semi-infinite slab with its surface exposed to heated oxygen. As shown in figure 3, the y-axis of the laboratory frame extends into the slab perpendicularly to the surface. In this analysis, the oxide thickness,  $z_0(t)$ , is assumed to increase parabolically with time according to

$$z_0(t) = At^{1/2}$$

(2)

where A is a proportionality constant. The position of the oxide-silicon interface at time t with respect to the initial silicon surface is given by

$$y_0(t) = \alpha z_0(t) \tag{3}$$

where  $\alpha$  is some constant fraction.

The kinetics of the oxide-layer growth [6] are such that all the increase in volume undergone by a thin layer of silicon when it is oxidized takes place at the oxide-silicon interface. Away from this growth front the oxide is being uniformly convected to the left with a speed  $(1-\alpha)dz_0(t)/dt$  relative to the laboratory frame. Consequently, there is both diffusive and convective transport of the impurity in the oxide. It is convenient to introduce a moving coordinate system,  $z = y + (1-\alpha)z_0(t)$ , in the oxide layer with its origin at the oxide surface. Then the impurity concentration in the oxide,  $C_1(z,t)$ , obeys, in the moving frame, the simple diffusion equation

$$\partial C_1(z,t)/\partial t = D_1 \partial^2 C_1/\partial z^2$$

(4)

for  $0 < z < z_0(t)$ . In the silicon there is only diffusion; therefore, in the laboratory frame

$$\partial C_2(y,t)/\partial t = D_2 \partial^2 C_2/\partial y^2$$

(5)

for  $y > y_0(t)$  where  $C_2(y,t)$  is the impurity concentration in the silicon.

At the oxide-silicon interface,  $C_1$  and  $C_2$  are coupled for t > 0 by the equilibrium condition

$$C_2[y_0(t),t] = mC_1[z_0(t),t]$$

(6)

ere m is the specified segregation (or distribution) coefficient. Another condition, plicable to the oxide-silicon interface, follows from the conservation of mass:

$$C_2(y_0,t)(\alpha - m^{-1})dz_0/dt = D_1\partial C_1/\partial z|_{z=z_0} - D_2\partial C_2/\partial y|_{y=y_0}.$$

(7)

e boundary condition at the oxide-oxygen interface is assumed to be

$$C_1(0,t) = C_S \tag{8}$$

ere  $C_s$  is a specified constant. This assumption is somewhat arbitrary; an alternative ndition which could be assumed at this interface is  $\partial C_1/\partial z = 0$  [6].

Equations (4) through (8) and the uniform initial condition,  $C_2(y,0) = C_b$ , where  $C_b$  is constant background concentration, specify the uniform redistribution problem. It has alytic solutions given elsewhere [5,6] for specific cases. This class of problem is apicable to MOS devices. Equations (4) through (8) and the nonuniform initial condition for  $y_0$ ,  $C_2(y,0) = C(y)$ , where C(y) is a nonuniform dopant concentration, specify the nonuniral redistribution problem. This class of problem is applicable to diffused and implanted yers in bipolar silicon devices.

With these formulations of the redistribution problem, it is possible to develop numeral solutions for a variety of cases including the oxidation of silicon slices both unimply doped and diffused with boron.

(S. R. Kraft and M. G. Buehler)

## 4. Diffused Layer Sheet Resistance

In the fabrication of semiconductor devices it is common practice to obtain the surface pant density,  $N_0$ , of a diffused layer from the measurement of the diffused-layer sheet restance,  $R_s$ ; the junction depth,  $X_j$ ; the background dopant density,  $N_b$ ; and an assumed functional form for the diffused layer. Irvin [8] has expressed these relations graphically by ing his well-known curves which relate resistivity, and hence carrier mobility,  $\mu$ , to pant density,  $N_I$ , by means of straight-line approximations. Recently, empirical expressons [9] have appeared which relate the carrier mobility data of Irvin to dopant density. The recently, Wagner [10] has published a modified hole mobility expression based on his rk on boron-implanted silicon. These expressions have the form

$$\mu = \mu_{\min} + (\mu_{\max} - \mu_{\min}) / [1 + N_{I} / N_{ref})^{\alpha}]$$

(9)

ere the constants,  $\mu_{\text{max}},~\mu_{\text{min}},~N_{\text{ref}},$  and  $\alpha,$  are listed in table 1.

The expression for the sheet resistance  $R_{_{\rm S}}$  of a diffused layer with a Gaussian profile

$$R_{s}^{-1} = q \int_{0}^{X_{j}} \mu(N - N_{b}) dx$$

(10)

ere q is the electronic charge,  $\mu$  is given by eq (9) with  $N_{I} = N + N_{b}$ ,  $N = N_{0} \exp(-x^{2}/L^{2})$ ,

NBS Applied Mathematics Division

## RESISTIVITY; DOPANT PROFILES

Table 1 — Mobility Equation Constants

| Туре | μ <sub>max</sub> , cm <sup>2</sup> /V·s | μ <sub>min</sub> , cm <sup>2</sup> /V·s | α    | N <sub>ref</sub> , cm <sup>-3</sup> | Reference |

|------|-----------------------------------------|-----------------------------------------|------|-------------------------------------|-----------|

| n    | 1330                                    | 65                                      | 0.72 | 8.5 × 10 <sup>16</sup>              | [9]       |

| р    | 495                                     | 47.7                                    | 0.76 | $6.3 \times 10^{16}$                | [9]       |

| p    | 495                                     | 47.7                                    | 0.76 | $1.9 \times 10^{17}$                | [10]      |

and L =  $X_j$  [ln(N<sub>0</sub>/N<sub>b</sub>)]<sup>1/2</sup>. Surface dopant density is plotted as a function of the product of R<sub>s</sub> and X<sub>j</sub> in figure 4 for a p-type layer diffused into uniformly doped n-type silicon and in figure 5 for an n-type layer diffused into uniformly doped p-type silicon. This form of presentation is more convenient for direct use by a process engineer than the form employed by Irvin [8]. Since curves in figure 5 are based on Caughey and Thomas' fit to Irvin's data, the curves are similar to those which appear in Irvin [8], but differences occur for N<sub>0</sub> >  $10^{20}$  cm<sup>-3</sup> where the expression of Caughey and Thomas fails to fit Irvin's data. The curves in figure 4 are based on Wagner's mobility expression.

The importance of the value of hole mobility assumed in computing the sheet resistance is illustrated in figure 6. For example, there is a difference of a factor of two between values for the surface dopant density for  $N_b = 10^{15}$  cm<sup>-3</sup> and  $R_s X_j = 1000~\Omega \cdot \mu m$  calculated using the two expressions. As indicated previously (NBS Tech. Note 806, pp. 21-23), the hole mobility at  $N_I = 10^{17}$  cm<sup>-3</sup> is about 240 cm<sup>2</sup>/V·s from Caughey and Thomas [9], whereas from Wagner [10] it is about 340 cm<sup>2</sup>/V·s. Similar differences occur throughout much of the impurity density range of interest. (T. E. Griffin and M. G. Buehler)

## 3.5. Silicon Resistivity Standards

A simple multipass round-robin experiment has been designed to test both the stability and the multilaboratory precision which can be expected from the silicon resistivity standard reference materials now available from NBS (NBS Tech. Note 806, pp. 8, 66). This experiment is to involve NBS and six other laboratories who have previously collaborated with ASTM Committee F-1 on Electronics in the measurement of bulk silicon resistivity. In the experiment itself each laboratory is expected to measure two sets of standard reference material wafers to be circulated among the laboratories specifically for this test in addition to submitting data taken at specified intervals on the standard silicon wafers which it owns. The experiment is expected to begin soon after the participating laboratories obtain their sets of standards and to run for 12 to 18 months. (J. R. Ehrstein and F. H. Brewer)

Figure 4. Surface dopant density of a p-type Gaussian diffused layer in uniformly doped n-type silicon as a function of the product of sheet resistance (300 K) and junction depth for various background dopant densities,  $N_{\rm h}$ .

Figure 5. Surface dopant density of an n-type Gaussian diffused layer in uniformly doped p-type silicon as a function of the product of sheet resistance (300 K) and junction depth for various background dopant densities,  $\mathbb{N}_{b}$ .

Figure 6. Surface dopant density of a p-type Gaussian diffused layer in uniformly doped n-type silicon as a function of the product of sheet resistance (300 K) and junction depth for various background dopant densities,  $N_b$ , showing the effect of using different relationships between hole mobility and impurity density in the calculation.

## 4. CRYSTAL DEFECTS AND CONTAMINANTS

## 4.1. Thermally Stimulated Current and Capacitance Measurements

The dynathermal current and capacitance response of the gold acceptor were measured in a gold-doped n-MOS capacitor. The capacitor was fabricated on the same gold-doped die as the previously studied gold-doped  $p^{\dagger}n$  junction (NBS Tech. Note 806, p. 13). The MOS capacitor had a 20-mil (0.5-mm) diameter gate on a 0.5- $\mu$ m thick oxide which was thermally grown on a  $10-\Omega \cdot \text{cm} n$ -type silicon epitaxial layer. The capacitor was mounted on a TO-5 header along with a temperature sensing diode. This configuration and an inexpensive cryostat used for the measurements have been described previously (NBS Tech. Note 806, pp. 13-16).

The dynathermal current and capacitance response of the gold-doped n-MOS capacitor is shown for various heating rates in figure 7. The gold defect centers were charged by increasing the gate bias to  $V_{g2} = -30$  V from a value  $V_{g1} = -15$  V which was applied at room temperature and held on the capacitor as it was cooled to liquid nitrogen temperature. The value of  $V_{g1}$  was such that an inversion layer of holes is formed at the oxide-silicon interface. This layer prevents the fast surface states from acting as hole and electron generation centers. An isothermal C-V plot, shown in figure 8, illustrates the gate voltage for which inversion is achieved.

The dynathermal response of figure 7 indicates the presence of two distinct phenomena. The first occurs at about 225 K when electrons are released from the gold acceptor; this is termed the majority carrier, phase I response. The second occurs at about 280 K where holes govern the generation rate of the gold acceptor; this is termed the minority carrier, phase II response.

The heating rate dependence of the current and capacitance response, as illustrated in the figure, indicates that the peak in the current  $I_{\rm I}$  during the majority carrier, phase I response occurs at emission temperatures which shift from 218 to 235 K. This is in good agreement with values obtained for the gold doped  $p^{\dagger}n$  junction reported previously. The peak in the current during the minority carrier, phase II response occurs at emission temperatures which shift from 273 to 292 K depending upon the heating rate. The capacitance step also shifts with heating rate and for the majority carrier, phase I response, the shift is similar to that observed in the  $p^{\dagger}n$  junction. From the capacitance values  $C_{\rm 2II}$  and  $C_{\rm 2If}$ , the gold density  $N_{\rm t}$  can be found from the expression originally derived for the case of a  $p^{\dagger}n$  junction [11]

$$N_{t} = \frac{2(V_{g2} - V_{g1}) C_{1}^{4} (C_{2If}^{2} - C_{2Ii}^{2}) (e_{n} + e_{p})}{q \epsilon A^{2} (C_{1}^{2} - C_{2If}^{2}) (C_{1}^{2} - C_{2Ii}^{2}) e_{n}}$$

(11)

where  $e_n$  and  $e_p$  are the electron and hole emission rates [12], q is the electronic charge,  $\epsilon$  is the dielectric constant of silicon, and A is the area of the MOS capacitor. For this MOS capacitor it was found that  $N_t$  = 2.2  $\times$  10<sup>13</sup> cm<sup>-3</sup>. It is interesting to note that when

Figure 7. Dynathermal response of a golddoped silicon n-MOS capacitor showing features due to the gold acceptor. (Heating rate: 1.6 K/s, curves A; 4.8 K/s, curves B; and 9.3 K/s, curves C; Device 2107.7. left hand current scale refers to the curves labeled IT and the right hand current scale to the curves labeled III. scale of the lower capacitance curves is expanded to show the Phase I capacitance transition which cannot be distinguished on the upper curves. The deep depletion condition, as indicated by the label on the upper capacitance curves, occurs when the potential is changed in a time short compared with the emission time constant at the temperature of the change, in this case ∿77 K. The capacitance curves labeled  $C_{2\text{Ii}}$ ,  $C_{2\text{If}}$ , and  $C_{2\text{II}}$  were measured at a gate voltage of  $V_{g2} = -30 \text{ V}$ . The topmost capacitance curve,  $C_1$ , was measured at  $V_{g1}$  =  $V_{g2} = -30 \text{ V}$ , but would have been the same if measured at  $V_{g1} = V_{g2} = -15 \text{ V.}$ )

gure 8. Isothermal, equilibrium, highequency capacitance response of a goldped silicon n-MOS capacitor measured at om temperature. (Device No. 2107.7.)

Figure 9. Dynathermal response of a gold-doped silicon n-MOS capacitor showing phase I current and phase II current and capacitance response of the gold acceptor as a function of initial gate voltage,  $V_{g1}$ , for a heating rate of 9.3 K/s and final gate voltage of -30 V. (Device No. 2107.7. The curves for  $V_{g1} = -15$  V, correspond to curves C in figure 7.)

Figure 10. Hall effect activation energy plot for the gold acceptor in n-type silicon. (Specimen 5N950-144.)

## CRYSTAL DEFECTS AND CONTAMINANTS

he capacitance pulls out of deep depletion and reaches its inversion value, the current brough the MOS capacitor shuts off.

The bias dependence of the current and capacitance dynathermal response is shown in igure 9 for a heating rate of 9.3 K/s and  $V_{\rm g2}$  = -30 V. Since  $V_{\rm g1}$  =  $V_{\rm g2}$  for the topmost apacitance curve, there is no charging of the space-charge layer. In the figure it is sen that the peak in the majority carrier phase I current,  $I_{\rm II}$ , is independent of bias and ccurs at 235 K. The peak in the minority carrier phase II current,  $I_{\rm II}$ , is somewhat bias ependent, for this peak depends on the space-charge width which, as seen in the capacitance esponse, is bias dependent. If  $V_{\rm g1}$  is more positive than -10 V, hole inversion does not ccur at the oxide-silicon interface and the generation centers there cause excess leakage arrents which greatly distort the current response. (W. E. Phillips and M. G. Buehler)

## 2. Energy Level Model for Gold-Doped Silicon

The activation energy of the gold acceptor in silicon was determined from measurements f the Hall coefficient as a function of temperature on a phosphorus-doped specimen with an nitial room temperature resistivity of 5.3  $\Omega$ ·cm. Gold was evaporated on both sides of the ilicon wafer and diffused at 950°C for 144 h; then both wafer faces were lapped to a depth f 125  $\mu$ m to remove excess surface gold before ultrasonically cutting a Hall bar for the lectrical measurements. The room temperature resistivity after gold diffusion was  $.9 \times 10^4 \ \Omega$ ·cm. A gold density of  $3.3 \times 10^{15} \ cm^{-3}$  was determined by neutron activation nalysis on a specimen from the same wafer as the Hall bar.

The activation energy of the gold acceptor was computed from the data shown in figure 0 by means of a least squares analysis [13] for the slope. The data points included in the nalysis are shown by circles; the points excluded because of their deviation from linearity re shown as squares. The calculated energy of 0.5381 ± 0.0004 eV represents the value at ero kelvin of the energy difference between the conduction band edge and the gold acceptor evel with the assumption that this difference is a linear function of temperature. The ncertainty in the energy is the square root of the estimated variance of the slope and does ot take into account systematic errors which might be present [14]. The energy difference btained from this specimen is in good agreement with the value of 0.5373 eV measured pre-iously on another specimen (NBS Tech. Note 773, pp. 13-14).

(W. R. Thurber and M. G. Buehler)

## 5. INSULATOR FILMS

Characterization of silicon dioxide and other insulator films in metal-insulator-semiconductor (MIS) device structures is an essential aspect of obtaining the stable insulator characteristics needed for the reliable operation of MIS integrated circuits. One particularly critical class of problems relates to the radiation sensitivity of thermally grown silicon dioxide in MOS devices.

The observed instability of silicon which is induced by ionizing radiation and is manifested by the build up of positive charge is believed to be due to hole trapping [15]. Optical absorption measurements and electron parametric resonance data indicate that the density of hole traps in silicon dioxide tends to increase with increased sodium concentration. Non-bridging oxygen atoms are known to behave as hole traps and to be enhanced by the presence of alkali impurities [16]. Consequently, the increased density of non-bridging oxygen atoms arising from the presence of sodium contamination seems to be to blame for the observed oxide behavior.

Large concentrations of sodium are located at both the metal and silicon interfaces of dry, thermally grown silicon dioxide [17, 18]. Just how the sodium distribution relates to the radiation sensitivity of an MOS structure needs to be explored. Ion microprobe mass analysis (IMMA) is a highly sensitive technique with which the sodium profile can be examined. There is, however, some concern about perturbing the impurity atom profile during ion sputtering. To assess the nature of this and other problems associated with this application of IMMA, detailed study of this technique is being started in cooperation with the NBS Analytical Chemistry Division. Initially, measurements are being made of several silicon dioxide-silicon structures, one of which was implanted with 80 keV sodium ions to a density  $10^{15} \ \mathrm{cm}^{-2}$ . This study will employ the ion microprobe mass analyzer at NBS.

Another technique, electron spectroscopy for chemical analysis (ESCA), can lead to a basic understanding of the perturbing effects of sodium on silicon-oxygen bonding and hole trapping. With this technique only a very shallow surface layer is explored. A study of growth characteristics of silicon dioxide in the presence of impurities, such as sodium, is being planned in cooperation with the NBS Physical Chemistry Division.

(D. C. Lewis and A. G. Lieberman)

The vacuum capability of the apparatus to be used for this study has been improved by two orders of magnitude by replacing the elastomer 0-rings by machined gold rings. As a consequence, the sensitivity level is now 5 percent of a monolayer or an impurity surface density of about  $10^{13}$  cm<sup>-2</sup>. Although sodium ion densities 100 times less than this can cause electrically observable effects in MOS devices, it is assumed that data obtained at detectable impurity densities can be extrapolated to situations of lesser density.

<sup>\*</sup> These specimens consisting of a 0.3-μm thick film of silicon dioxide, grown at 1000°C followed by a 20 min anneal in nitrogen, on a <100> surface of 7 to 13 Ω·cm, p-type silicon were supplied by H. L. Hughes of the Naval Research Laboratory.

#### INSULATOR FILMS

An Auger electron gun is available which can be added to this ESCA spectrometer to btain resolutions as small as 0.7 eV, five times better than the resolution of commercially vailable Auger apparatus.

(N. E. Erickson and J. T. Yates)

Oxide stability is most often characterized electrically by means of the biasemperature stress test [19] in which shifts in flat-band voltage of an MOS capacitor are

bserved after stressing with an applied voltage at some elevated temperature. In preparaion for detailed study of this test, a hot-cold stage with appropriate electrical feedhroughs is being designed and constructed. (M. G. Buehler and A. W. Stallings)

A substantial research effort to develop radiation hardened MOS integrated circuits has een supported by various government agencies for the past several years. The results of his work are reported in scattered locations and in a number of different formats. Consevently, it is difficult to obtain a complete picture of the process technologies proposed or producing such circuits and to ascertain their relative merits. At the request of one f the sponsors of the Program, an effort has been initiated to document process technology and test procedures which have been developed under government contract.

(A. G. Lieberman and D. C. Lewis)

NBS Physical Chemistry Division

## 6. TEST PATTERNS

## 6.1. Process Development

Several modifications were made in the processing procedure as part of a continuing task to demonstrate the application of test patterns in improving and controlling fabrication processes. Run No. 2.3 was made on four  $3-\Omega \cdot \mathrm{cm}$ , n-type bulk silicon slices and four  $10-\Omega \cdot \mathrm{cm}$ ,  $n/n^+$  epitaxial silicon slices; two slices of each type were doped with gold to a density of about  $10^{13}$  cm<sup>-3</sup>. The emitter-base junction depth was nominally 0.5  $\mu \mathrm{m}$  and the base-collector junction depth was nominally 1.7  $\mu \mathrm{m}$ . Representative electrical data from both bulk and epitaxial slices without gold doping are summarized in table 2.

Process changes were made to reduce the base and emitter sheet resistance, the metal-to-emitter contact resistance, the back-side contact resistance, and the fixed oxide charge density, each of which was previously higher than the respective target value (NBS Tech. Note 806, pp. 39-41). In most cases, further iterations appear to be required in order to achieve the target values.

It was found that use of a 0.6 percent antimony-doped gold layer evaporated onto the back side of the slice after etching in CP-6 and alloyed for 30 min at 500°C in a nitrogen atmosphere substantially reduced the back-side contact resistance. However, the value achieved on bulk slices remained higher than desired.

Elimination of the staining of the boron-diffused regions prior to phosphorous deposition failed to reduce the metal-to-emitter contact resistance to an acceptable value. The fixed oxide charge density remains at a higher level than desired on most slices. This is due to the poor quality of the deionized water ( $\rho \leq 7.5~\text{M}\Omega \cdot \text{cm}$ ) used in the clean-up and oxidation steps. Improved water treatment is expected to cure this problem.

(R. L. Mattis, M. G. Buehler, T. F. Leedy, and J. Krawczyk)

## 6.2. Metal-To-Base Contact Resistor Study

As part of a continuing study of the structures on test pattern NBS-2 (NBS Tech. Note 788, pp. 16-17), a series of measurements was made on the metal-to-base contact resistor, structure number 16 on the test pattern. This structure can be understood with the help of the photograph of figure 11 and the schematic cross-section of figure 12. A current, I, is passed through contact pads 1 and 4 and the voltage, V, is measured between contact pads 2 and 3. The substrate is allowed to float electrically during the measurement, and the current is reversed to check for linearity. The current path is indicated in figure 12. The metallization, as seen in the figure, lies on top of the oxide everywhere except in the contact window and in contact pads 1 and 3. Similarly, the  $p^{\dagger}$  diffused region is under oxide everywhere except for the contact window and the contact pads 1 and 3. The measurement is therefore a Kelvin resistance measurement; the voltage-current ratio (V/I) when multiplied by 6.45 yields the metal-to-base contact resistance in units of microohm·square centimetres for a square contact window 1.00 mil (25.4  $\mu$ m) on a side.

## TEST PATTERNS

Table 2 — Measurements on Test Pattern NBS-2; Run No. 2.3

| Test                  |                                                               | Measur                 | Measured Value         |                              |  |

|-----------------------|---------------------------------------------------------------|------------------------|------------------------|------------------------------|--|

| tructure <sup>a</sup> | Quantity Measured                                             | Bulk                   | Epitaxial              | Target<br>Value              |  |

| 14                    | Base Sheet Resistance, $\Omega/\sigma$                        | 73                     | 87                     | 100±20                       |  |

| 15                    | Emitter Sheet Resistance, $\Omega/\Box$                       | 1.6                    | 0.2                    | 10±5                         |  |

| 16                    | Metal-to-Base Contact Resistance, $(\mu\Omega \cdot cm^2)$    | 10.9                   | 11.4                   | <50                          |  |

| 17                    | Metal-to-Emitter Contact Resistance, $(\mu\Omega \cdot cm^2)$ | 38.4                   | 43.8                   | <5                           |  |

| 18                    | Back-side Contact Resistance, $\boldsymbol{\Omega}$           | 9.0                    | 0.25                   | <1                           |  |

| 12                    | Fixed Oxide Charge Den-<br>sity, cm <sup>-2</sup>             | 5.5 × 10 <sup>11</sup> | 2.5 × 10 <sup>11</sup> | $(2.5\pm0.5) \times 10^{11}$ |  |

| 12                    | Collector Oxide Thick-<br>ness, nm                            | 520                    | 500                    | 500±50                       |  |

| 12                    | MOS C-V Collector Doping Density, cm <sup>-3</sup>            | $1.7 \times 10^{15}$   | $5.5 \times 10^{14}$   |                              |  |

| 6                     | Junction C-V Collector<br>Doping Density, cm <sup>-3</sup>    | $1.7 \times 10^{15}$   | $7.5 \times 10^{14}$   |                              |  |

| 6                     | Junction Bulk Leakage<br>@ 5 V, nA/cm <sup>2</sup>            | 29                     | 17                     | <5                           |  |

| _                     | Base-Collector Junction<br>Depth (μm)                         | 1.71                   | 1.92                   |                              |  |

|                       |                                                               |                        |                        |                              |  |

See table 1 and figure 6, NBS Tech. Note 788, pp. 16-17 for identification of test structures.

Figure 11. Photomicrograph of the metal-to-base contact resistor, test structure No. 16 of test pattern NBS-2. (The contact window (A) is nominally 1 mil (25  $\mu m)$  on a side. The center-to-center spacing between adjacent bonding pads (1, 2, 3, 4) is 11 mils (0.28 mm).)

Figure 12. Schematic view of a section through the contact window of the metal-to-base contact resistor test structure pictured in figure 11. (The current path is through pad 4, the metallization stripe (D), the contact window (A), the  $p^+$  diffused layer (C), and contact pad 1. To measure the potential difference, V, contact is made to the metal side of the contact window through the narrow metallization stripe leading to pad 2 and to the diffused-layer side by the narrow diffused region leading to pad 3. The metallization is isolated from the diffused layer and the n-type silicon substrate (E) everywhere except at pads 1 and 3 and the contact window (A) by an oxide layer (B).)

#### TEST PATTERNS

Several experiments were carried out on this test structure. In one experiment, the etal-to-base contact resistance was mapped over a specimen surface in a manner similar to he map of base sheet resistivity reported previously (NBS Tech. Note 806, pp. 41-43). alues of metal-to-base contact resistance were  $22.4 \pm 2.5 \, \mu\Omega \cdot \text{cm}^2$  for a base sheet resisance of  $182 \pm 6 \, \Omega/\Box$ . This value for contact resistance and the values listed in table 2 re roughly 10 to 20 times larger than ideal values quoted in the literature [20,21] for luminum on boron-doped silicon. This difference can be attributed, at least in part, to he geometry of the contact structure. Because the current path on either side of the conact is parallel with the plane of the contact interface, only a fraction of the contact rea carries a significant current. Hence, the area used to normalize the volt-current ratio o contact resistance is actually substantially less than the window area which was used to btain the values reported. Because of overetching, the contact windows may be somewhat arger than the nominal size. This also affects the normalization because the actual curent carrying area is proportional to the length of the side of the contact area.

In a second experiment it was established that the *n*-type substrate of the test strucure must be left floating with no electrical connections in order to confine the return urrent to the diffused layer.

A third experiment verified the linearity of  $\Delta V$  as a function of I over the range from 1.1 to 20 mA. This suggests that although it is nonuniform, the current distribution across the contact window area does not change over a considerable range. Consequently, the test tructure appears to be suitable as a process monitor which can identify deviations from the nominal contact resistance even though it may not yield absolute values for normalized contact resistance.

(F. R. Kelly, R. L. Mattis, and M. G. Buehler)

The range of values quoted is for two sample standard deviations on Slice No. 3, Run No. 2.2. The base is a diffused boron layer, nominally 1.7  $\mu m$  deep.

## 7. PHOTOLITHOGRAPHY

## 7.1. Introduction

Failures in the photolithographic processing of semiconductor devices can cause both low production yields and poor device reliability. Most of these failures can be related either to faulty masks or failures of the photoresist to perform as desired. To establish the extent and nature of problems associated with the photolithographic processes, a literature search was initiated, and discussions were held with numerous individuals involved in the use of photolithography in various aspects of the microelectronics industry.

### 7.2. Mask Inspection

The need for mask inspection methods to detect faulty masks prior to their use in production was determined to be the most critical need. This criticality results from the relatively long time, several days to a few weeks, that is required for the replacement of a faulty mask. Also, because a mask or set of masks is used to produce many successive devices in production, a faulty mask, undetected for only a short time, can produce a relatively large number of defective devices.

For these reasons, the development of methods to inspect and detect faulty masks, prior to their use in production represents a potential cost per part reduction and an increase in yield. Such inspection methods need to include accurate and rapid dimensional measurements to insure the proper alignment and registration of masks used in the successive steps of device manufacture. In addition, these methods need to include a rapid, reliable means of detecting flaws such as pinholes, thereby assuring the use of only high quality masks.

Initial efforts are being directed toward examination of optical and micrometrology problems associated with mask making and mask inspection in the industry with the cooperation of the NBS Optical Physics Division.

### 7.3. Photoresist Materials

In these discussions it was also determined that measurements of photoresist properties are needed that can be made prior to the use of the resist and interpreted in terms of subsequent resist behavior. The performance and behavior of photoresists are ultimately controlled by the chemistry of the polymers. The most important performance characteristics and their relation to polymer properties are [22-24]:

Adhesion — If the polymer is composed of molecular fractions which are relatively short-chained, solvents, etches, and moisture can more easily permeate the polymer and attack the polymer-wafer surface bonding.

Resolution — Failure of the polymer to form sufficient cross linking can lead to poorly defined edges, low adhesion, and poor resolution through swelling caused by solvent permeation. Poor resolution can also be caused by the presence of large particles of gel or polymeric material. All of

## PHOTOL I THOGRAPHY

these effects can lower the resistance of the photoresist to acid and moisture attack.

Pinhole propensity — This can be increased by the presence of gel and particulate polymeric material in the resist.

Photosensitivity — Polymer molecules of relatively short chain lengths or failure to have enough photoactive and cross linking sites will cause insufficient cross linking upon exposure and fail to adhere properly. Too many of these sites will cause excessive cross linking and lead to difficulty in completly removing the photoresist.

Wet and dry coating thicknesses — These properties are directly influenced by the viscosity and solids content, both of which are interrelated through the polymer characteristics.

Illumination characteristics also influence the performance of photoresist films. The nteraction of light with the layers and interfaces of composite photoresist-coated wafers an result in light scattering and a subsequent loss in resolution. Light scattered into rotected regions can also result in exposure of the photoresist in undesired regions. Non-niform illumination across the mask-photoresist-wafer composite during exposure can lead to osses in resolution, and over- and under-exposed areas on the same wafer resulting in poor roduction yields.

Initially, the feasibility of using light scattering measurements to monitor the cleaniness, and gel and polymeric particle content of photoresists will be investigated. In

ddition, an improved mask is being obtained to facilitate completion of the development and

valuation of the test procedure for measuring velocity and acceleration of photoresist

pinners (NBS Tech. Note 592, pp. 46-47).

(D. B. Novotny)