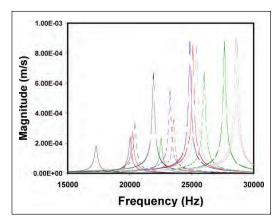

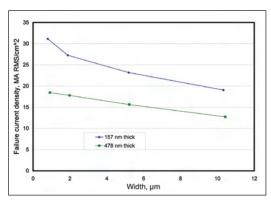

# Semiconductor Microelectronics and Nanoelectronics Programs

NISTIR 7321

July 2006

### U.S. DEPARTMENT OF COMMERCE

Carlos M. Gutierrez, Secretary

### **Technology Administration**

Robert Cresanti, Under Secretary of Commerce for Technology

### **National Institute of Standards and Technology**

William Jeffrey, Director

### **DISCLAIMER**

**Disclaimer:** Certain commercial equipment and/or software are identified in this report to adequately describe the experimental procedure. Such identification does not imply recommendation or endorsement by the National Institute of Standards and Technology, nor does it imply that the equipment and/or software identified is necessarily the best available for the purpose.

**References:** References made to the International Technology Roadmap for Semiconductors (ITRS) apply to the most recent edition, dated 2005.

Semiconductor Industry Association. *The International Technology Roadmap for Semiconductors*, 2005 edition. SEMATECH: Austin, TX, 2005.

This document is available on-line at URL: http://public.itrs.net or in printed copy by contacting SEMATECH, 2706 Montopolis Drive, Austin, TX 78741, ITRS department 860-008, phone: (512) 356-3500.

The reader will notice that there are acronyms and abbreviations throughout this document that are not spelled out due to space limitations. We have listed the acronyms and abbreviations in an appendix at the end of this document.

### **CONTENTS**

| Welcome and Introduction                                                                               | v        |

|--------------------------------------------------------------------------------------------------------|----------|

| Office of Microelectronics Programs Organization                                                       | vii      |

| Lithography Metrology Program                                                                          | 1        |

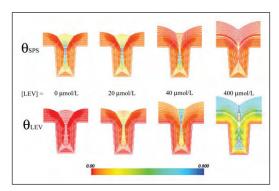

| Metrology Supporting Deep Ultraviolet Lithography                                                      | 3        |

| Metrology Supporting Extreme Ultraviolet Lithography                                                   | 9        |

| Polymer Photoresist Fundamentals for Next-Generation Lithography                                       | 15       |

| Critical Dimension and Overlay Metrology Program                                                       | 21       |

| Wafer-Level and Mask Critical Dimension Metrology                                                      | 22       |

| Scanning Electron Microscope-Based Dimensional Metrology                                               | 23       |

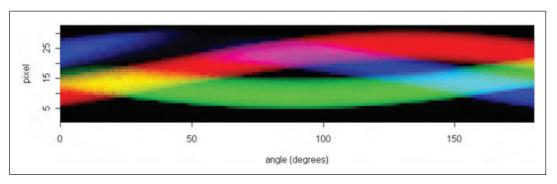

| Scatterometry-Based Dimensional Metrology                                                              | 29       |

| Scanning Probe Microscope-Based Dimensional Metrology                                                  | 33       |

| Small Angle X-Ray Scattering-Based Dimensional Metrology                                               | 39       |

| Fabrication and Calibration Metrology for Single-Crystal CD Reference Mar                              | erials43 |

| Optical-Based Photomask Dimensional Metrology                                                          | 49       |

| Model-Based Linewidth Metrology                                                                        | 53       |

| Atom-Based Dimensional Metrology                                                                       | 57       |

| Wafer-Level and Overlay Metrology                                                                      | 61       |

| Front-End Processing Metrology Program                                                                 | 67       |

| Wafer and Chuck Flatness Metrology                                                                     | 69       |

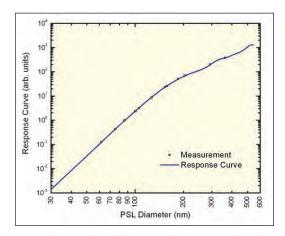

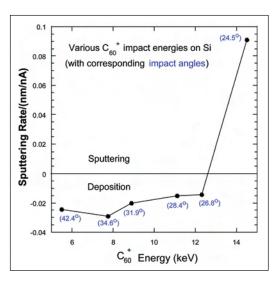

| Modeling, Measurements, and Standards for Wafer Surface Inspection                                     | 73       |

| Front-End Materials Characterization.                                                                  | 77       |

| Interconnect and Packaging Metrology Program                                                           | 87       |

| Atomic Layer Deposition – Process Models and Metrology                                                 | 89       |

| Superconformal Deposition: Copper and Advanced Interconnect Materials                                  | 95       |

| Interconnect Materials and Reliability Metrology                                                       | 98       |

| Basic Materials Properties                                                                             | 99       |

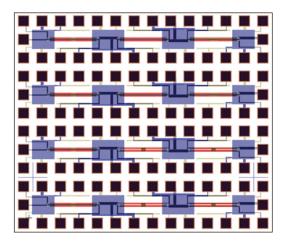

| Test Structures For Interconnect Metrology and Modeling                                                | 107      |

| Solders and Solderability Measurements for Microelectronics                                            | 113      |

| Process Metrology Program                                                                              | 117      |

| Gas Property Data and Flow Standards for Improved Gas Delivery Systems                                 | 119      |

| Low Concentration of Humidity Standards                                                                | 123      |

| Temperature Measurements and Standards for Semiconductor Processing                                    | 129      |

| Plasma Process Metrology                                                                               | 133      |

| Assessment of Measurements and Standards for Gas Phase Processes in Semiconductor Device Manufacturing | 139      |

| Analysis Tools and Techniques Program                                     | 141 |

|---------------------------------------------------------------------------|-----|

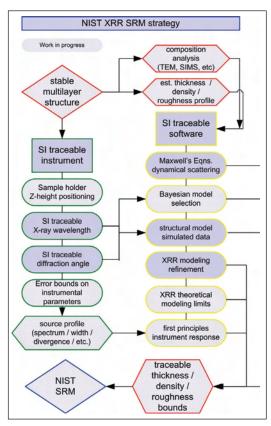

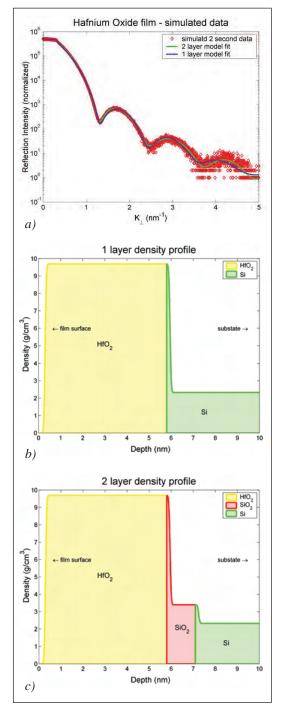

| Thin-Film X-Ray Metrology for Microelectronics                            | 143 |

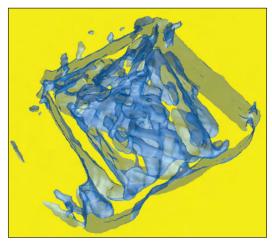

| Electron Microscope Tomography of Electronic Materials                    | 149 |

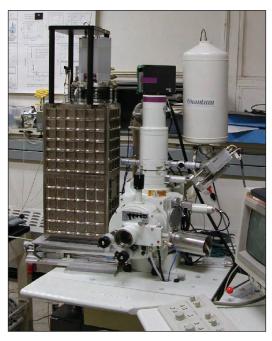

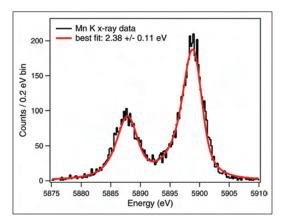

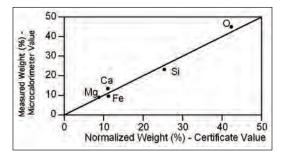

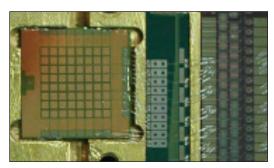

| High-Resolution Microcalorimeter X-Ray Spectrometer for Chemical Analysis |     |

| Device Design and Characterization Program                                | 157 |

| Device Characterization and Reliability                                   | 159 |

| Nanoelectronic Device Metrology                                           | 165 |

| Power Semiconductor Device Metrology                                      | 171 |

| Organic Electronics Metrology                                             | 175 |

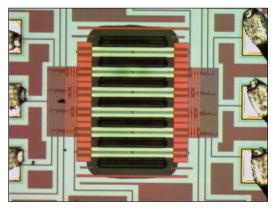

| Micro- and Nano-Electro-Mechanical Technology Metrology                   | 179 |

| NIST's Center for Nanoscale Science and Technology Nanofab                | 183 |

| Metrology for Spintronic Devices                                          | 185 |

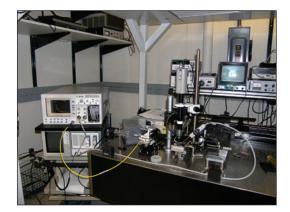

| BioElectronics Metrology                                                  | 191 |

| System Design and Test Metrology Program                                  | 195 |

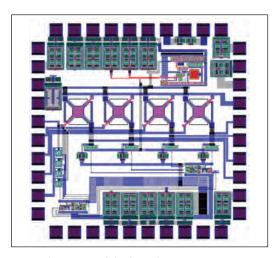

| Metrology for System-on-a-Chip                                            |     |

| At-Speed Test of Digital Integrated Circuits                              | 201 |

| Thermal Measurements and Packaging Reliability                            | 205 |

| Manufacturing Support Program                                             | 211 |

| Factory Time Synchronization Standards Development for E-Manufacturing    | 213 |

| E-Diagnostics Security                                                    |     |

| Engineering Chain Management in the Semiconductor Industry                |     |

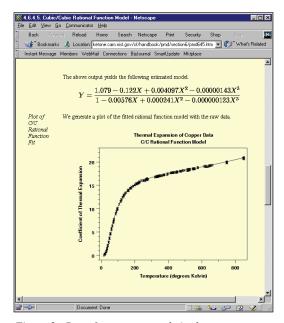

| NIST/SEMATECH E-Handbook of Statistical Methods                           |     |

| Abbreviations and Acronyms                                                | 220 |

| Technical Contacts                                                        | 224 |

### WELCOME AND INTRODUCTION

### **W**ELCOME

The microelectronics industry supplies vital components to the electronics industry and to the U.S. economy, enabling rapid improvements in productivity and in new high technology growth industries such as electronic commerce and biotechnology. The National Institute of Standards and Technology, NIST, in fulfilling its mission of strengthening the U.S. economy, works with industry to develop and apply technology, measurements and standards; and applies substantial efforts on behalf of the semiconductor industry and its infrastructure. This report describes the many projects being conducted at NIST that constitute that effort.

### HISTORICAL PERSPECTIVE

NIST's predecessor, the National Bureau of Standards (NBS), began work in the mid-1950s to meet the measurement needs of the infant semiconductor industry. While this was initially focused on transistor applications in other government agencies, in the early 1960s the Bureau sought industry guidance from the American Society for Testing and Materials (ASTM) and the U.S. Electronic Industries Association (EIA). ASTM's top priority was the accurate measurement of silicon resistivity. NBS scientists developed a practical nondestructive method ten times more precise than previous destructive methods. The method is the basis for five industrial standards and for resistivity standard reference materials widely used to calibrate the industry's measurement instruments. The second project, recommended by a panel of EIA experts, addressed the "second breakdown" failure mechanism of transistors. The results of this project have been widely applied, including solving a problem in main engine control responsible for delaying the launch of a space shuttle.

From these beginnings, by 1980 the semiconductor metrology program had grown to employ a staff of 60 with a \$6 million budget, mostly from a variety of other government agencies. Congressional funding in that year gave NBS the internal means to maintain its semiconductor metrology work. Meeting industrial needs remained the most important guide for managing the program.

### INDUSTRIAL METROLOGY NEEDS

By the late 1980s, NBS (now NIST) recognized that the semiconductor industry was applying a much wider range of science and engineering technology than the existing NIST program was designed to cover. The necessary expertise existed at NIST, but in other parts of the organization. In 1991, NIST established the Office of Microelectronics Programs (OMP) to coordinate and fund metrological research and development across the agency, and to provide the industry with easy single point access to NIST's widespread projects. Roadmaps developed by the U.S. Semiconductor Industry Association (SIA) have independently identified the broad technological coverage and growing industrial needs for NIST's semiconductor metrology developments. As the available funding and the scope of the activities grew, the collective name became the National Semiconductor Metrology Program (NSMP), operated by the OMP.

The NSMP has stimulated a greater interest in semiconductor metrology, motivating most of NIST's laboratories to launch additional projects of their own and to cost-share OMP-funded projects. The projects described in this book represent this broader portfolio of microelectronics projects. Most, but not all, of the projects described are partially funded by the NSMP, which is providing a \$12 million budget in fiscal year 2006.

### FOSTERING NIST'S RELATIONSHIPS WITH THE INDUSTRY

NIST's relationships with the SIA, SEMATECH and its subsidiary, International SEMATECH Manufacturing Initiative (ISMI), and the Semiconductor Research Corporation (SRC) are also coordinated through the OMP. Staff from OMP and NIST Laboratories represents NIST on the SIA committees that develop the International Technology Roadmap for Semiconductors (ITRS), as well as on numerous SRC Technical Advisory Boards. NIST staff is also active in the semiconductor standards development work of the ASTM, the International National Electronics Manufacturers Initiative (iNEMI), the EIA, the International Organization for Standardization (ISO), and Semiconductor Equipment and Materials International (SEMI).

### LEARN MORE ABOUT SEMICONDUCTOR METROLOGY AT NIST

This publication provides summaries of NIST's metrology projects for the silicon semiconductor industry and their suppliers of materials and manufacturing equipment. Each project responds to one or more metrology requirements identified by the industry in sources such as the ITRS. NIST is committed to listening to the needs of industry, working with industry representatives to establish priorities, and responding where resources permit with effective measurement technology and services. For further information, please contact NIST as follows:

Office of Microelectronic Programs National Institute of Standards and Technology 100 Bureau Drive Building 225, Room A317, Mail Stop 8101 Gaithersburg, MD 20899-8101

Gaithersburg, MD 20899-8101 Telephone: (301) 975-4400

Fax: (301) 975-6513 e-mail: nsmp@nist.gov

Internet: http://www.eeel.nist.gov/omp

# Office of Microelectronics Programs Organization

KNIGHT, Stephen (Director) (301) 975-2871

stephen.knight@nist.gov

MARTINEZ DE PINILLOS, Joaquin V. (Senior Scientist) (301) 975-8125

jack.martinez@nist.gov

BUCKLEY, Michele L. (Secretary) (301) 975-4400

michele.buckley@nist.gov

From left to right: Joaquin Martinez de Pinillos, Stephen Knight, and Michele Buckley.

### LITHOGRAPHY METROLOGY PROGRAM

Advances in lithography have largely driven the spectacular productivity improvements of the integrated circuit industry, a steady quadrupling of active components per chip every three years over the past several decades. This continual scaling down of transistor dimensions has allowed more and more components on a chip, lowered the power consumption per transistor, and increased the speed of the circuitry. The shrinking of device dimensions has been accomplished by shortening the wavelength of the radiation used by the lithography exposure tools. The industry at this point has moved into the deep ultraviolet (DUV) spectrum. Currently, exposure tools operating at 193 nm are in leading edge manufacturing facilities. The first 193 nm immersion lithography tools have been shipped to leading edge manufacturers and are being exercised for manufacture. High index fluids and lens materials for 193 nm tools are under intense exploration to develop high numerical aperture systems. Looking beyond the deep ultraviolet, extreme ultraviolet radiation (EUV) at 13 nm is being investigated, and demonstration tools are being designed and assembled. At least three alpha tools will be shipped to development consortia in 2006. The overall goal of this task is to support these developments in DUV and EUV. The areas of emphasis are characterization of lens materials, and immersion fluids, laser calorimetry, radiation detector sensitivity and damage, EUV lens metrology, and metrology for the development of advanced photoresist materials for both DUV and EUV.

## METROLOGY SUPPORTING DEEP ULTRAVIOLET LITHOGRAPHY

### GOALS

Develop solutions to key optical metrology issues confronting the semiconductor lithography industry. These include development of measurement methods and standards for characterizing deep ultraviolet (DUV) laser sources, detectors, and materials. One focus is on delivering high-accuracy measurements of DUV detector parameters and materials properties of immediate need by the industry. There is ongoing activity in the following areas: standards development, calibration services, characterization of optical materials, sources, and detectors, in addition to advising customers on in-house measurements.

### CUSTOMER NEEDS

Increasing information technology requirements have created a strong demand for faster logic circuits and higher-density memory chips. This demand has led to the introduction of DUV laser-based lithographic tools for semiconductor manufacturing. These tools, which employ KrF (248 nm) and ArF (193 nm) excimer lasers, have led to an increased demand for accurate optical measurements at DUV laser wavelengths.

A new lithography technology, immersion lithography, depends on incorporating a high-index fluid between the optical system and the wafer and possibly also incorporating a high-index material as the last lens element. Design and development of 193 nm and 157 nm immersion lithographies require accurate measurements of the index properties of the potential 193 nm and 157 nm fluids and materials.

To support these efforts, the National Institute of Standards and Technology (NIST), with SEMA-TECH, has developed a DUV metrology program focusing on the characterization of DUV optical materials, sources, and detectors.

The potential challenges for lithographic development are discussed in the 2005 International Technology Roadmap for Semiconductors. Page 1 of the Lithography section states: "Significant challenges exist in extending optical projection lithography at 193 nm wavelength using immersion lenses...." The need for advancing metrology in lithography is discussed on page 1

of the Metrology section: "Metrology continues to enable research, development, and manufacture of integrated circuits. The pace of feature size reduction and the introduction of new materials and structures challenge existing measurement capability."

### TECHNICAL STRATEGY

High-accuracy measurements of the index properties of UV materials are required for the design of DUV lithography systems. NIST has been providing absolute index measurements at 193 nm and 157 nm with an accuracy of about 5 ppm to the industry using its DUV minimumdeviation-angle refractometer. To improve on this absolute accuracy, NIST has begun constructing a new state-of-the-art minimum-deviation system and separately developed another system based on a vacuum ultraviolet (VUV) FT spectrometer and synchrotron radiation as a continuum source (see Fig. 1). Both of these systems will enable measurements to an accuracy of 1 ppm, and will be used to characterize high-index lens materials and immersion fluids for 193 nm and 157 nm lithography systems.

Figure 1. Facility for detector VUV radiation damage study using synchrotron radiation from SURF and a 157 nm excimer laser.

**DELIVERABLES:** Index measurement capability with 1 ppm uncertainty. 2Q 2006

### **Technical Contacts:**

J. H. Burnett M. Dowell

"It's an excellent service NIST has performed for the entire industry. The kind of thing NIST is there for – to identify issues before the train wreck takes place."

> Mordechai Rothschild, Massachusetts Institute of Technology's Lincoln Laboratory

■ Taking full advantage of the potential resolution gain with immersion lithography may require using high-index materials as the last lens element, though as yet no such material has been demonstrated at 193 nm. To address this need we have begun, with the support of SEMATECH, a survey of candidate materials. We have identified several classes of oxide-based materials which have very high indices (near 2.0) at this wavelength and which can in principle be highly transparent at 193 nm. We have begun a program of complete optical characterization measurements of these materials to identify the most promising candidates and to assess their potential for development for lithography optics.

**DELIVERABLES:** Fully characterize the 193 nm optical properties of leading candidate high-index materials. 2Q 2006

An absolute light source in the DUV range based on synchrotron radiation using NIST's Synchrotron Ultraviolet Radiation Facility (SURF III) has been established using a dedicated beamline at SURF III. The flux of the DUV radiation at this beamline can be known to very high accuracy through the well established equations governing the behavior of the synchrotron radiation. The beamline is designed for customer calibration of a variety of DUV instruments to assist the development of the DUV lithography such as monochromators, discharge lamps, and irradiance meters. The spectral range covers all of the current important wavelengths for semiconductor industry such at 248 nm, 193 nm, 157 nm and even down to 13 nm. The uncertainty of such calibration is better than 1 % in the case of deuterium lamp calibration.

**DELIVERABLES:** Provide customer DUV calibration for discharge lamps, monochromators, and irradiance meters using SURF III source-based beamline with highest accuracy. Ongoing

■ Beginning with the first edition of the National Technology Roadmap for Semiconductors (NTRS) in 1992, the semiconductor industry has made an organized, concentrated effort to reduce the feature sizes of integrated circuits. As a result, there has been a continual shift towards shorter exposure wavelengths in the optical lithography process. Because of their inherent characteristics, deep ultraviolet (DUV) lasers, and specifically KrF (248 nm) and ArF (193 nm), excimer lasers, are the preferred sources for high-resolution lithography at this time. In addition, we can provide calibrations for F<sub>2</sub> (157 nm) excimer lasers. To

meet the laser metrology needs of the optical lithography community, we have developed primary standards and associated measurement systems at 193 nm and 248 nm, and 157 nm. Figure 2 shows the excimer laser calibration facility.

Figure 2. Laboratory for excimer laser energy and power meter calibrations, with measurement systems for 248 nm, 193 nm, and 157 nm. The excimer lasers are along the top right and the enclosures for nitrogen gas purging are in the foreground.

**DELIVERABLES:** Proven high-quality calibration services, and supporting measurements for excimer laser power and energy meters to the Semiconductor Industry at 248 nm, 193 nm, and 157 nm. Ongoing

### **A**CCOMPLISHMENTS

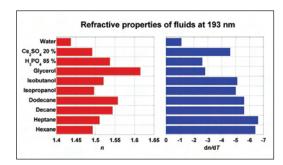

We have used our Hilger-Chance refractometer system to assist the industry in the search for appropriate high-index fluids (with n greater than water, 1.4366 at 193 nm) for possible use in immersion photolithography. In addition to providing measurement services to several companies which are developing new fluids for 157 nm and 193 nm lithography, we have performed our own survey of fluids at 193 nm. The results are shown in Fig. 3. As this figure shows, there are a number of fluids which are transparent at 193 nm and have *n* larger than water, up to 1.62 for glycerol. However, the thermo-optic coefficient, dn/dT, is larger as well, which may make the use of these difficult in a commercial stepper system because of thermal stability issues.

Figure 3. Measured index of refraction n and thermo coefficient dn/dT of a number of potential immersion fluids for 193 nm lithography.

- We have performed additional measurements of the effect of dissolved air on the refractive index of water at several wavelengths in the visible and UV and compared the results with predictions based on the equation of state of water and the known partial molar volumes and polarizabilities of the soluble components of air. The data and model calculations are in reasonable agreement, and demonstrate that the magnitude of the effect gets larger at shorter wavelength, up to −6.7x10<sup>-6</sup> at 193 nm. While industry uses degassed water for immersion lithography, our results will enable any potential optical distortions due to air exposure to be modeled at the system level.

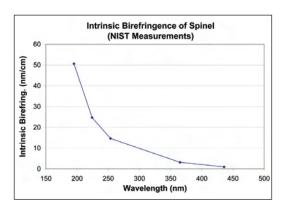

- We have identified four major classes of oxide-based materials that have potential to be used as high-index lens materials for enabling further feature-size reduction with immersion lithography. The four classes are: (1) Group II oxides, *e.g.*, MgO, (2) crystalline spinel (MgAl<sub>2</sub>O<sub>4</sub>) and its variants, (3) a ceramic form of spinel, and (4) aluminum garnets, *e.g.*, YAG. We have made preliminary characterization measurements of the key 193 nm optical properties (see Fig. 4), including the intrinsic birefringence, of members

Figure 4. Measured intrinsic birefringence of crystalline spinel vs. wavelength.

of each of these classes needed to assess their suitability. As a result of these measurements, several potentially feasible candidates have been established.

- We have constructed a radiometric facility tailored for the DUV range using a beamline at NIST's SURF III with the radiation measurement scale derived from a high-accuracy cryogenic radiometer. The beamline is designed for very general-propose high-accuracy measurements. We have used this facility to measure DUV general material properties such as transmission and reflectance. Examples of such measurements include DUV mirrors, windows, filters, and also the transmission and absorption of liquids that could be used for immersion lithography. On the detector side, we have calibrated and characterized a variety of DUV detectors such as solid state photodetectors, solar-blind detectors, photoconductive detectors, and pyroelectric detectors. We also performed irradiance calibrations for DUV irradiance meters.

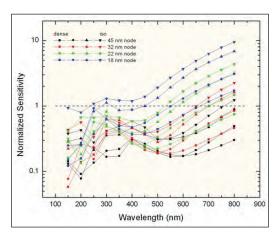

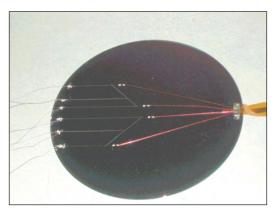

- We have built a facility at SURF III that allows simultaneous exposure of photodiodes to excimer radiation (see Fig. 5) and synchrotron radiation. Measurements of the spectral responsivity can be made in the spectral range from 130 nm to 320 nm with a standard uncertainty of less than 1 %. The intense, pulsed laser radiation was used to expose the photodiodes for varying amounts of accumulated irradiation whereas the low intensity, continuously-tunable cw radiation from the synchrotron source was used to characterize the photodiodes. The changes in the spectral responsivity of different kinds of diodes such as UV silicon, GaP, GaAsP, PtSi, diamond, and GaN were measured for a large range of total accumulated dose from an F<sub>2</sub> excimer laser operating at 157 nm. Differing amounts of changes were seen

Figure 5. Measurement system for detector damage study by a 157 nm pulsed excimer laser.

in different diodes depending on the total excimer irradiation dose and they showed different spectral changes in the responsivity as well. This yields important information about the mechanism responsible for the degradation of photodiodes. For example, we have determined that for silicon photodiodes under irradiation with a 157 nm excimer laser, an important mechanism for the degradation is the formation of trap states at the interface of the silicon-silicon dioxide induced by the damaging radiation. These trap states act as recombination centers and reduce the yield of electric current generated by incident radiation. A model was developed to simulate the change in response for photodiode irradiated by 157 nm radiation.

- During the last 15 years we have developed a suite of laser calorimeter standards for 248 nm, 193 nm, and 157 nm excimer laser energy and power measurements traceable to SI units. The 248 nm and 193 nm calorimeters use a specially designed absorbing cavity with a volume absorbing glass to reduce potential damage to the cavity by the high peak power in the UV laser pulses. The 157 nm calorimeter is a fundamentally new type of laser calorimeter standard that uses a thinwalled SiC absorbing cavity, which is designed to completely absorb and spread the incoming laser energy through multiple reflections. All of these calorimeters are calibrated using an imbedded electrical heater that allows for traceability to SI units through electrical standards of resistance and voltage. Calibrations for industry customers are accomplished for each wavelength with appropriate measurement systems that involve purging of oxygen to eliminate atmospheric absorption of the laser radiation.

- As a further extension of our excimer laser services we have developed the capability to directly measure UV irradiance or "dose" at 248 nm and 193 nm, which involves homogenizing the beam profile and measuring the energy transmitted through a calibrated aperture. This capability can improve accuracy for customers who need to measure the energy absorbed at a surface such as at the wafer plane.

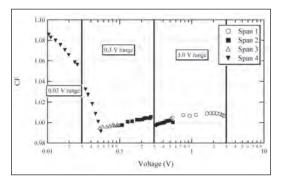

- We have also developed the capability to characterize the nonlinear response of 193 nm and 248 nm excimer laser detectors based on the correlation method. The method and system solves measurement difficulties associated with the temporal and spatial fluctuations of excimer laser pulse energy. Using this system, one can easily determine problems such as those due to the

incident pulse energy, range discontinuities associated with detector gain, and detector background noise (see Fig. 6).

Figure 6. Nonlinearity measurement result of a 193 nm pulsed laser energy detector. CF is the correction for the detector's nonlinear response. The response is measured in four spans, covering 2.5 meter settings. The large degree of nonlinearity at the low end of the meter range is due to background effects.

We completed the first internal comparison of the NIST UV excimer laser calorimeters. This work includes measurements taken over the course of a two-year period in which the performance of the NIST 157, 193, and 248 nm excimer laser calorimeters was monitored at the design wavelengths as well as at the other excimer laser wavelengths. The results show good agreement among the transfer standards and excellent stability over time. From these data, we determined that the responsivity of the NIST UV laser calorimeters all agree within their stated uncertainties. In all but one case, the calorimeters' responsivities agree to better than 0.3 %. The comparison between the DUV (193 nm) and UV (248 nm) calorimeters at 248 nm uncovered a 1 percent difference between the calorimeters' responsivities. This difference is due to partial transmission of the 248 nm radiation through the absorbing glass of the DUV calorimeter which, reduces the calorimeter's absorptance and alters its response.

### **COLLABORATIONS**

Air Products and Chemicals, Inc., Bridgette Budhlall, immersion photolithography fluid development.

### RECENT PUBLICATIONS

S. G. Kaplan and J. H. Burnett, "Optical properties of fluids for 248 nm and 193 nm immersion photolithography," *Applied Optics* **45**, 1721 (2006).

A.H. Harvey, S.G. Kaplan, and J.H. Burnett, "Effect of dissolved air on the density and refractive index of water," submitted to *International Journal of Thermophysics* (2005).

- P. S. Shaw, R.Gupta, K. R. Lykke, "Stability of photodiodes under irradiation with a 157 nm pulsed excimer laser," Appl. Opt. **44**, 197 (2005).

- S. Yang, D. A. Keenan, M. L. Dowell, "Nonlinearity Measurements of the Response of Silicon Photodiodes at 193 nm," Council for Optical Radiation Measurement (CORM) 2005, May 10-12, 2005, Boulder, Colorado, (Approved by ERB).

- H. Laabs, D. A. Keenan, S. Yang, M. L. Dowell, "Measurement of detector nonlinearity at 193 nm," Appl. Opt., Vol. 44, No. 6, pp.841-848 (20-FEB-2005).

- J. H. Burnett and S. G. Kaplan, "Measurement of the refractive index and thermo-optic coefficient of water near 193nm," Journal of Microlithography, Microfabrication, and Microsystems 3, pp. 68-72 (2004).

- J. H. Burnett and S. Kaplan, "Measurement of the refractive index and thermo-optic coefficient of water near 193nm," in Proceedings of SPIE Vol. 5040 *Optical Microlithography XVI*, edited by Anthony Yen, (SPIE, Bellingham, WA, 2003) 1142-1149.

- Z. H. Levine, J. H. Burnett, and E. L. Shirley, "The photoelastic and elastic properties of the fluorite structure materials, LiF, and Si," Phys. Rev. B **68**, 155120 (2003).

- P. S. Shaw, U. Arp, H. W. Yoon, R. D. Sanders, A. C. Parr, and K.R. Lykke, "A SURF beamline for synchrotron source-based absolute radiometry," Metrologia, **40**, S124 (2003).

- D. A. Keenan, H. Laabs, S. Yang, M. L. Dowell, "A 193 nm Laser Detector Nonlinearity Measurement System," Proc., Measurement Science Conference, January 13-17, 2003, Anaheim, California, (01-JAN-2003).

- C. L. Cromer, M. L. Dowell, R. D. Jones, D. A. Keenan, S. Yang, "A Primary Standard for 157 nm Excimer Laser Measurements," 2003 Int'l Conf. on Characterization and Metrology for ULSI Tech. March 25-27, 2003, Austin, Texas, Vol. 683, pp.409-412 (01-MAR-2003).

- P. S. Shaw, D. Shear, R. J. Stamilio, U. Arp, H. W. Yoon, R. D. Sanders, A.C. Parr, and K.R. Lykke, "The new beamline 3 at SURF III for source-based radiometry," Rev. Sci. Instrum. **73**, 1576 (2002).

- P. S. Shaw, T. C. Larason, R. Gupta, and K. R. Lykke, "Characterization of UV detectors at SURF III," Rev. Sci. Instrum. **73**, 1625 (2002).

- D. X. Chen, M. L. Dowell, C. L. Cromer, Z. F. Zhang, "Thermal Response and Inequivalence of Pulsed Ultraviolet-Laser Calorimeters," J. Thermophys. Heat Trans. 16 (January 2002) 36.

- M. L. Dowell, R. D. Jones, H. Laabs, C. L. Cromer, and R. Morton, "New developments in excimer laser metrology at 157 nm," Proc. SPIE Metrology, Inspection, and Process Control for Microlithography XVI, D. J. C. Herr, Editor, (March 2002) 63.

- P. S. Shaw, R. Gupta, and K. R. Lykke, "Characterization of an ultraviolet and a vacuum-ultraviolet irradiance meter with synchrotron radiation," Appl. Opt. **41**, 7173 (2002).

## METROLOGY SUPPORTING EXTREME ULTRAVIOLET LITHOGRAPHY

### GOALS

Provide leading-edge metrology for the development and characterization of sources, optical components, and dosimeters used in Extreme Ultraviolet Lithography (EUVL). (EUVL utilizes radiation at 13.4 nm.)

### CUSTOMER NEEDS

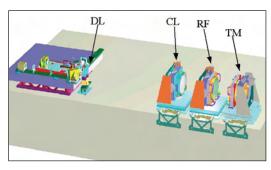

An intense international effort is presently underway to install EUVL into commercial production in 2011 at the 32 nm node. As part of that effort, ASML will deliver two alpha-generation steppers for initial testing later this year.

Several significant challenges to commercialization of EUVL remain, including source power, optics lifetime, and optics and mask fabrication. The associated metrological challenges include the development of: (1) highly precise extreme ultraviolet (EUV) reflectometry; (2) accurate pulsed EUV radiometry for source comparisons and wafer-plane dosimetry; (3) accelerated testing techniques for optics lifetime characterization; and (4) nanometer-level optical figure measurement.

### TECHNICAL STRATEGY

### 1. Precise EUV Reflectometry

The present NIST/DARPA EUV Reflectometry Facility is located on a multipurpose beamline on the NIST Synchrotron Ultraviolet Radiation Facility (SURF III) storage ring. Currently the NIST/DARPA facility is the only one in the U.S. large enough to measure optics up to 40 cm in diameter and 40 kg in mass. The facility has a demonstrated reflectivity accuracy of 0.3 % and wavelength accuracy of 0.001 nm, with plans under-way to improve each accuracy by a factor of two in the near future.

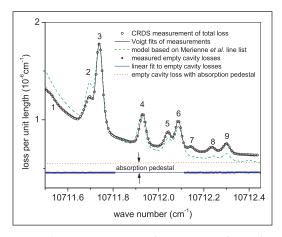

Although primarily designed to serve the EUVL community by providing accurate measurements of multilayer mirror reflectivities, this beamline with its associated sample chamber has also been used for many other types of measurements since the beamline's commissioning in early 1993. Among the other measurements in support of EUVL performed recently are the radiometric calibration of the "Flying Circus II" and "E-Mon" radiometers used for the comparison of source outputs, resist dosimetry, and determination of

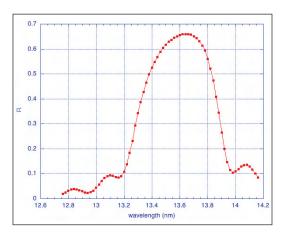

EUV optical constants through angle dependent reflectance measurements. The reflectivity of a typical mirror designed for use in a EUVL stepper is shown in Fig. 1.

Figure 1. Reflectivity vs. wavelength of a typical MoSi multilayer mirror. The measurement was made at 5° from normal incidence.

**DELIVERABLES:** Full reflectivity maps of EUV mirrors up to 40 cm in diameter and 45 kg in mass on an as needed basis for the EUVL community. Many other types of EUV measurements including transmission, resist dosimetry and other testing, and cw radiometric calibrations of fully assembled filter radiometers used in source comparisons.

### 2. EUV DOSIMETRY

NIST is the primary national source for the radiometric calibration of detectors from the infrared to the soft X-ray regions of the spectrum. The Photon Physics Group is responsible for maintaining the spectral responsivity standards in the far- and extreme-ultraviolet spectral regions, including 13.5 nm, the EUVL wavelength of interest. We operate several beamlines at the SURF III synchrotron radiation facility, a quasi-cw source, as well as laser-produced plasma source, which is pulsed with a 10 ns pulse length. With these facilities, we can calibrate EUV detectors and dosimeter packages under either cw or pulsed conditions.

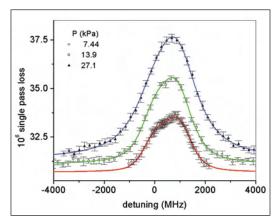

A major concern when using solid state photodiodes for detection of short pulse length radiation is that the detector may saturate under the high peak power, even though the average power is moderate. We have measured the saturation characteristics of EUV sensitive Si photodiodes using 532 nm radiation as a proxy for 13.5 nm; the

#### **Technical Contacts:**

- T. Lucatorto

- C. Tarrio

- S. Grantham

- U. Griesmann

- S. Hill

absorption characteristics in Si are nearly identical. This proxy procedure has been validated by correcting a 13.5 nm pulsed calibration for saturation in both the sample radiometer and the standard photodiode using saturation data obtained at 532 nm. The corrected results were in good agreement with individual component calibrations, while the uncorrected results were not.

We have found that the photodiode responsivity is an inherently non-linear function of pulse energy, but the responsivity can be fit by a calibration function having two constant parameters. Use of the non-linear calibration function allows the photodiode to be used with reasonable uncertainty even when the responsivity has decreased due to saturation effects by as much as a factor of two. We have developed a model of the physical processes that are responsible for saturation. The loss of total collected charge is modeled as a result of recombination processes in the device during the electronic readout time. The model correctly predicts the behavior of both calibration parameters as a function of reverse bias in the range from 0 V to 150 V and spot sizes greater than 0.01 mm<sup>2</sup>. We have found no dependence on pulse length from 10 ns to 1 µs, indicating that the effects of saturation are the same for laser-produced plasma sources and for the pinched plasma sources with longer pulse lengths. There is substantial deviation from the expected saturation behavior as the illuminated area decreases (i.e., the energy density increases) to very small spots sizes (less than 0.01 mm<sup>2</sup>). The measured saturation loss is less than our model predicts, probably due to lateral diffusion current that decreases the local carrier density. It has been reported previously that the low-power limit of the pulsed responsivity is equal to the responsivity measured with a low-power, cw source. Combining these results, it is possible to transfer a continuous wave (cw) calibration to a pulsed application with low uncertainty.

In 2006, we will participate in an international intercomparison of EUV detector responsivity. This intercomparison will establish the worldwide equivalence of detector responsivity measurements from the major National Metrology Institutes performing these calibrations. We will also work to expand our EUV measurement capabilities to include measurements of EUV spectrograph and CCD responsivity to further aid the EUV lithography community.

#### **DELIVERABLES:**

- EUV detector responsivity international intercomparison. 3Q 2006

- EUV CCD responsivity measurement. 3Q 2006

- EUV spectrograph measurement. 4Q 2006

### 3. EUV DAMAGE CHARACTERIZATION

One of the potential showstoppers for commercialization of extreme ultraviolet lithography (EUVL) is the degradation of the multilayer-mirror stepper optics. The mirrors lose reflectivity because adsorbed contaminant gases such as hydrocarbons and water are cracked by the energetic (13.5 nm) photons. This leads to growth of an amorphous carbon layer on the optics surfaces or to oxidation of the optics themselves. The former effect is largely reversible; however, the latter is not. Unfortunately, these ambient contaminants cannot be eliminated by baking because the alignment of the mirror stack must be maintained to submicron tolerances. Various capping layers are currently being developed to extend the lifetime of the multilayer mirrors towards the required goal for commercialization of only a few per-cent reflectivity loss over 30000 hours (h) of use.

To study the effectiveness of new capping layers and to better understand the underlying processes responsible for mirror degradation, NIST has commissioned a new beamline at the Synchrotron Ultraviolet Radiation Facility (SURF III) that can expose capped-multilayer samples to  $\approx$  6 mW/mm<sup>2</sup> of 13.5 nm radiation in an environment of controlled water or hydrocarbon partial pressures up to 6.7×10<sup>-4</sup> Pa. To date the most successful capping layer available to the community has been ~ 2 nm of ruthenium. Our exposure facility has demonstrated that multilayers with this capping layer suffer approximately one-tenth the reflectivity loss of bare Si-capped multilayers when exposed for  $\approx 100 \text{ h}$  under rather aggressive conditions of  $1 \times 10^{-4}$  Pa of water vapor.

Clearly, testing multiple capping layers for the required 30000 h optic-lifetime is not feasible. We have therefore developed a program for accelerated lifetime testing in which multilayers are exposed to various EUV intensities under various high-vacuum environments. The ultimate goal of this program is to develop a model of mirror damage that will enable the extrapolation of the years-long-lifetime under normal operating conditions from a few hundred hours of exposure under appropriately chosen accelerated exposure conditions. This effort requires an understanding of the

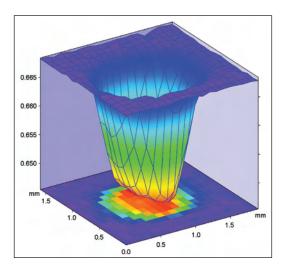

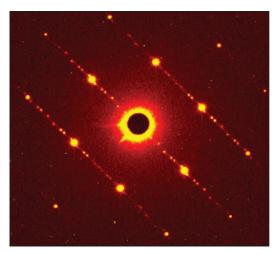

underlying damage mechanisms that are being studied by an iterative series of controlled exposures and analysis. In addition to measuring the reflectivity loss of exposed multilayers (Figure 2), the damage will be characterized using a range of surface analysis techniques. Although this effort is just beginning, we have already discovered that small levels of hydrocarbons ( $1\times10^{-7}$  Pa) can completely determine the rate of mirror damage, even in the presence of much larger partial pressures of water vapor ( $7\times10^{-4}$  Pa). Thus, the vacuum environment must be carefully controlled and well characterized for any accelerated testing procedure to produce meaningful results.

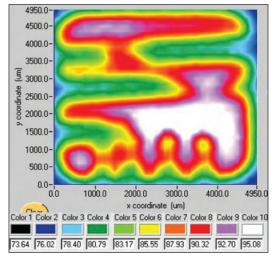

Figure 2. Spatial mapping of the reflectivity of a multilayer mirror following exposure to EUV under aggressive environmental conditions.

To respond to the growing need for optic-lifetime characterization we have continued to expand our capabilities. The original lifetime testing chamber was developed with support from Sematech and Sandia National Labs. Recently, a second beamline with a lifetime testing chamber has been constructed and commissioned with industry support. In addition, with intramural support from the NIST Advanced Technologies Program, we are installing a pulsed source so that mirror degradation caused by the quasi cw irradiation of the SURF synchrotron can be compared with that caused by pulsed irradiation. In addition to expanding our facilities, we have also established very fruitful collaborations with experts in surface science both within and outside the NIST community.

### **DELIVERABLES:**

Commission new lifetime testing beamline. 2Q 2006

- Work with industrial collaborators to evaluate titanium dioxide as a possible capping layer. 4Q 2006

- Install pulsed EUV source for testing under pulsed irradiation. 4Q 2006

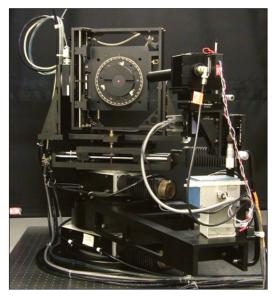

### 4. Sub-nm Uncertainty Optical Figure Measurement

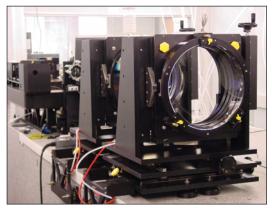

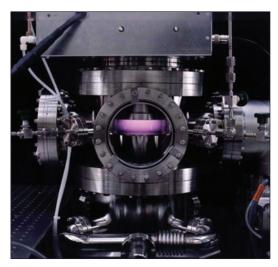

The commissioning of the "eXtremely accurate CALIBration InterferometeR" (XCALIBIR) at NIST is now complete and the instrument is fully functional (Fig. 3). The XCALIBIR interferometer is a multi-configuration precision phase-measuring interferometer for optical figure measurements of flat, spherical and aspheric optics that can achieve the very low measurement uncertainties that are required for the measurement of EUVL optics.

Figure 3. A view of the XCALIBIR interferometer.

The XCALIBIR interferometer may be operated in either Twyman-Green or Fizeau configurations. A beam expander in the test arm of the interferometer provides a collimated test beam with 300 mm diameter. Transmission spheres are used to realize a spherical Fizeau interferometer for the testing of spherical and aspheric surfaces. The part under test is mounted on a remotely controlled 5+1-axis mount that can be moved on air bearings along a precision slideway in the direction of the optical axis of the interferometer. A system of three laser-interferometers tracks the movement of the test mount in the direction of the optical axis. A single-mode external cavity diode laser (ECDL) is used as the light source in XCALIBIR. The laser frequency can be modulated to vary the effective temporal coherence over a wide range. Optical fibers with different core diameters are used to couple the light into the interferometer. The spatial coherence of the light source can thus be varied by using fibers with different core diameter.

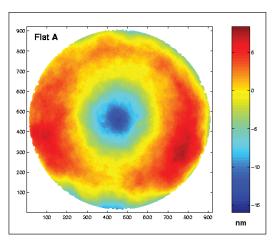

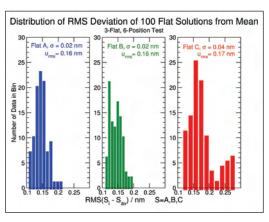

The 300 mm diameter reference flats for the flat Fizeau configuration of the interferometer were calibrated with a 3-flat, 6-position self-calibration test. Figure 4 shows the topography of one of the reference flats. A large number of 3-flat measurements were made to estimate the measurement uncertainty. For each of the flats A, B, and C the *rms* of the difference between the averaged flat solutions and the individual measurements was plotted in a histogram (Fig. 5). A (statistical) measurement uncertainty of approximately 0.2 nm rms is evident.

Figure 4. Topography of a 300 mm diameter XCALIBIR reference flat.

Figure 5. Distribution of rms deviations from best estimates surface (mean) for three flats A, B, and C.

When measurements of aspheric optics without null-optics are made, it is frequently the case that only a part, or subaperture, of a surface can be measured at once. For the figure measurement of the entire aspheric surface a number of overlapping subaperture measurements must then be combined, or "stitched" together. We have implemented flexible and robust algorithms for the stitching of subaperture measurements. To

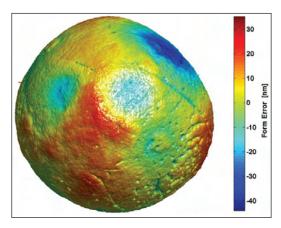

demonstrate the power of the stitching algorithm a precision silicon sphere with 96.4 mm diameter (a 1 kg mass sphere) was set up on a rotary table in XCALIBIR and the surface figure error was measured with an F/1.3 transmission sphere. 138 surface error measurements were made at 10° intervals. As shown in Fig. 6, the individual, overlapping, surface error measurements were then stitched together to form a map of the form error of the silicon sphere.

Figure 6. Deviation from perfect spherical form of a 1 kg precision silicon sphere.

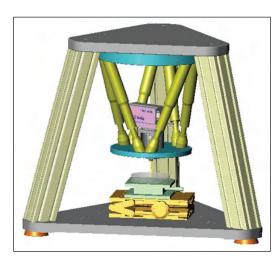

In addition to the XCALIBIR interferometer, we are developing a new metrology tool for the measurement of aspheric and free-form precision surfaces, the Geometry Measuring Machine (GEMM). In its current form, GEMM is a profilometer for free-form surfaces. A profile is reconstructed from the local curvature of a test part surface, measured at several locations along a line. For profile measurements of free-form surfaces, methods based on local part curvature sensing have strong appeal. Unlike full-aperture interferometry they do not require customized null optics. The uncertainty of a reconstructed profile is critically dependent upon the uncertainty of the curvature measurement and, to a lesser extent, on curvature sensor positioning accuracy. The new instrument, shown in Fig. 7, provides an alternative means for validating the measurements made with XCALIBIR.

**DELIVERABLES:** Validation of stitching method for form error measurements of aspheric surfaces with low uncertainty. This will be done with an industrial collaborator. 4Q 2006

Figure 7. Geometry Measuring Machine (GEMM) for form measurements of free-form precision surfaces.

### COLLABORATIONS

VNL at Lawrence Livermore National Laboratory, Saša Bajt, EUV Multilayer Development and Coating Team.

### **RECENT PUBLICATIONS**

- S. Grantham, C. Tarrio, R. E. Vest, and T. B. Lucatorto, "Metrology for EUVL Sources and Tools, in EUV Sources for Lithography," V. Bakshi, ed. (SPIE Press, Bellingham, WA, 2006).

- R. E. Vest, Y. Barad, M. L. Furst, S. Grantham, C. Tarrio, and P. S. Shaw, "NIST VUV Metrology Programs to Support Space-Based Research," Advances in Space Research 37, 283-296 (2006).

- R. E. Vest, S. Hill, and S. Grantham, "Saturation effects in solid-state photodiodes and impact on EUVL pulse energy measurements," Metrologia 43, S84-S88 (2006).

- S. M. Owens, J. S. Gum, C. Tarrio, S. Grantham, J. Dvorak, B. Kjornrattanawanich, R. Keski-Kuha, R. J. Thomas, C. C. Kankelborg, "Narrow-band EUV multilayer coating for the MOSES sounding rocket," in Proc. SPIE Vol. 5900, Optics for EUV, X-Ray, and Gamma-Ray Astronomy II, pp. 5-13 (2006).

- U. Griesmann, "Three-Flat Test Solutions Based on Simple Mirror Symmetry," Appl. Opt. 2006 (in press).

- N. Machkour-Deshayes, J. Soons, U. Griesmann, R. S. Polvani, J. Stoup, and Z. Q. Lu, "Form-profiling of optics using the Geometry Measuring Machine and the M-48 CMM at NIST," Accepted for publication in J. Res. NIST (2006).

- S. Grantham, C. Tarrio, S. B. Hill, and T. B. Lucatorto, "*Optics go to extremes in EUV Lithography*," Laser Focus World, Vol. **41**, no. 11, pp. 117-122 (2005).

- C. Tarrio and S. Grantham, "A synchrotron beamline for extreme-ultraviolet multilayer mirror endurance testing," Rev. Sci. Instrum. **76**, 056101 (2005).

- C. Tarrio, S. Grantham, R. E. Vest, and K. Liu, "A simple transfer-optics system for an extreme-ultraviolet synchrotron beamline," Rev. Sci. Instrum. 76, 046105 (2005).

- U. Griesmann, N. Machcour-Deshayes, J. Soons, B. C. Kim, Q. Wang, J. R. Stoup, and L. Assoufid, "Uncertainties in aspheric profile measurements with the Geometry Measuring Machine at NIST," in Advanced Characterization Techniques for Optics, Semiconductors, and Nanotechnologies II; Angela Duparre, Bhanwar Singh, Zu-Han Gu; Eds., Proc. SPIE 5878, 112-124 (2005).

- U. Griesmann, Q. Wang, J. Soons, and R. Carakos, "A simple ball averager for reference sphere calibrations," Optical Manufacturing and Testing VI; H. Philip Stahl; Ed., Proc. SPIE **5869**, 189-196 (2005).

- U. Griesmann, J. Soons, and Q. Wang, "Measuring Form and Radius of Spheres with Interferometry," Annals of the CIRP 53, 451-454 (2004).

- W. M. Clift, L. E. Klebanoff, C. Tarrio, S. Grantham, O. R. Wood II, and N.V. Edwards, "Scaling studies of capping layer oxidation by water exposure with EUV radiation and electrons," SPIE vol. 5374, Emerging Lithographic Technologies VIII p. 666 (2004).

# POLYMER PHOTORESIST FUNDAMENTALS FOR NEXT-GENERATION LITHOGRAPHY

### GOALS

In this project, we are developing an integrated program involving fundamental studies of photoresist materials to be correlated with resist performance metrics impacting next generation photolithography. We work closely with industrial collaborators to develop and apply high spatial resolution and chemically specific measurements to understand varying material properties and process kinetics at nanometer scales and to provide high quality data needed in advanced modeling programs. The understanding developed in this program will provide a detailed foundation for the rational design of materials and processing strategies for the fabrication of sub 50 nm structures. The unique measurement methods we apply include X-ray and neutron reflectivity (XR, NR), small angle neutron scattering (SANS), near-edge X-ray absorption fine structure (NEX-AFS) spectroscopy, quartz crystal microbalance (QCM), nuclear magnetic resonance (NMR), atomic force microscopy (AFM), fluorescence correlation spectroscopy (FCS) and combinatorial methods. Our efforts focus on the fundamentals of polymeric materials and processes that control the resolution of the photolithography process including: (1) the physical properties of and polymer chain conformation within sub 50 nm structures; (2) the spatial segregation and distribution of photoresist components; (3) the transport and kinetics of photoresist components, and the deprotection reaction interface over nanometer distances; (4) the material sources of line-edge roughness (LER), a measure of the ultimate resolution of the lithographic process; (5) the polymer physics of the developer solution and the dissolution process; and (6) influence of moisture on the thermo-physical properties of interfaces as applicable to immersion lithography. These data are needed to meet the future lithographic requirements of sub 50 nm imaging layers and critical dimensions.

### CUSTOMER NEEDS

Photolithography remains the driving and enabling technology in the semiconductor industry to fabricate integrated circuits with ever decreasing feature sizes. Today, current fabrication facilities use chemically-amplified photoresists, complex and highly tuned formulations of a

polymer film loaded with photoacid generators (PAGs) and other additives. Upon exposure of the photoresist film through a mask, the PAG creates acidic protons. A post-exposure bake is then applied and the acid protons diffuse and catalyze a deprotection reaction on the polymer that alters its solubility for development in an aqueous base solution. These reaction-diffusion, and development processes must be understood and controlled at the nanometer length scale to fabricate effectively integrated circuits. Chemically amplified resists are also deposited onto bottom anti-reflection coatings (BARCs). Interactions and component transport between the BARC and resist layer can lead to loss of profile control or pattern collapse. Detailed studies of these interaction and transport mechanisms are needed to design materials for the successful fabrication of sub 50 nm structures.

There are significant challenges in extending this technology to fabricate the smaller feature sizes (sub 50 nm) needed to continue performance increases in integrated circuits. First, new radiation sources with shorter wavelengths (193 nm or EUV) require photoresist films nearing 100 nm thick to ensure optical transparency and uniform illumination. In these ultrathin films, confinement can induce deviations in several key materials parameters such as the macromolecular chain conformation, glass transition temperature, component distribution, or transport properties. Furthermore, the required resolution for a sub 50 nm feature will be on the order of 2 nm, approaching the macromolecular dimensions of the photoresist polymers. It is not yet clear how deviations due to confinement will affect the ultimate resolution in these ultra-thin photoresist films. Additionally, the material sources of feature resolution (line-edge and sidewall roughness) and profile control need to be identified and understood to ensure the success of needed patterning technologies.

The requirements for advanced photoresists are discussed in the 2005 International Technology Roadmaps for Semiconductors on page 9, Lithography Section, "Photoresists need to be developed that provide good pattern fidelity, good line width control, low line width roughness, and few defects. As feature sizes get smaller, defects and monomers will have comparable dimensions with implications for the filtering of resists."

### **Technical Contacts:**

V. M. Prabhu E. K. Lin W. L. Wu

"[This work] opens a window of opportunity to construct structure-property relationships between chemical transport mechanisms and ultimate resist resolution. It may also lead to insights into the ultimate, intrinsic resolution limits and critical dimension control of polymer-based imaging materials."

E. Reichmanis and O. Nalamasu, Bell Labs, Lucent Technologies, Science, 297, 349 (2002).

### TECHNICAL STRATEGY

In this project, we use model photoresist materials to validate the new measurement methods. Model photoresist materials (248 nm, 193 nm, 157 nm, and EUV) have been used initially to address several important fundamental questions including the thermal properties of ultrathin films as a function of film thickness and substrate type, the conformation of polymer chains confined in ultrathin films, the surface concentration of PAGs, the diffusion and the deprotection reaction kinetics, and the physics of the development process. We also are adapting the application of combinatorial methods as a tool to determine rapidly important lithographic parameters and to identify material factors impacting feature resolution. These results provide a basis for understanding the material property changes that may affect the development of lithography for sub-50 nm structures using thin photoresist imaging layers. The interaction between model photoresists and BARC materials also requires detailed experimental investigation to optimize the materials factors impacting lithographic performance.

#### **DELIVERABLES:**

- Develop model thin films to measure the transport and kinetics of photoresist components and the deprotection reaction as a function of PAG size and resist copolymer chemistry. 2Q 2006

- Conclude protection degree effect on the dissolution and swelling behavior and the relationship to surface roughness for 193 nm photoresist polymers. 2Q 2006

- Utilize reaction-front bilayer geometry to identify and quantify the effects of developer solution parameters (base concentration, ionic strength) on the final resolution of lithographic materials. 3Q 2006

- Quantify surface segregation, surface deprotection chemistry, distribution of photoresist components (resist, photoacid, base additive) in 193 nm resists, using NEXAFS. 4Q 2006

- Conclude PAG loading effect on the dissolution and swelling behavior and the relationship to surface roughness for model EUV photoresist polymers.

4Q 2006

- Quantify the effect of dose on the form and spatial extent of photoacid diffusion at model lithographic line edges for EUV photoresist. 2Q 2006

### **A**CCOMPLISHMENTS

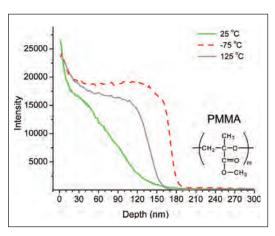

■ The molecular origin of dimensional changes within ultrathin films when exposed to developer

solutions was measured using neutron reflectivity. A model photoresist material provided needed in the fundamentals of material sources to line-edge roughness. Quartz crystal microbalance measurements complement these measurements with the added ability to measure the kinetics of swelling, however, the profile and chemical specificity are exclusively obtained with NR.

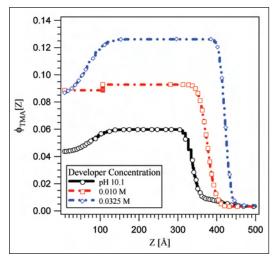

These new measurement methods, applicable to immersion lithography, demonstrate that swelling and aqueous base penetration must be considered to improve dissolution models involving solid-liquid interfaces. The aqueous base profile, shown in Fig. 1, illustrates the penetration of the small base molecule throughout the thin film as a function of developer strength. The swelling, due to polyelectrolyte effects, was predicted in FY03. The influence of moisture and interfacial energy are also probed using NR, XR, and quartz crystal microbalance techniques, allowing complete equilibrium and kinetics measurement methods.

Figure 1. Developer Fundamentals for LER. Direct measure of the base concentration dependence of swelling and deuterated tetramethyl ammonium ion profile throughout the thickness, of a model 157 nm photoresist using liquid immersion neutron reflectivity.

■ The kinetics of an acid-catalyzed deprotection reaction in model photoresist materials was studied as a function of copolymer composition with Fourier transform infrared (FTIR) spectroscopy. Three methacrylate-based terpolymers with varying compositions of acid-labile and non-reactive (lactone) monomers were studied. A mathematical model was developed to analyze the acid catalyzed deprotection kinetics with respect to coupled reaction rate and acid-diffusion

processes. The first order reaction rate constant decreases as a non-reactive comonomer content is increased. Additionally, the extent of reaction appears self-limiting as verified by a slowing down necessitating an acid-trapping chemical equation to model the data. An example is shown in Fig. 2. This composition-dependent reaction constant indicates a strong interaction of the acid with the increasing polar resist matrix that drastically reduces the acid transport rate. The severely reduced acid transport is consistent with hydrogen bonding between photoacid and methacrylic acid product. These results demonstrate a correlation between polymer microstructure and acid catalyzed kinetics; necessary measurements for analysis of coupled reaction-diffusion processes. Finally, the models were applied to understand the limiting spatial extent of photoacid diffusion at the model line edge determined by neutron reflectivity.

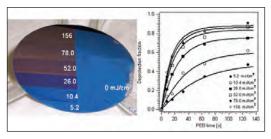

Figure 2. Wafer after exposure to varied DUV dose and fixed baking time the color change represents slight changes in film thickness with extent of reaction. Quantification of the extent of reaction (deprotection fraction) versus post-exposure bake time for model 193 nm resist for varying dose.

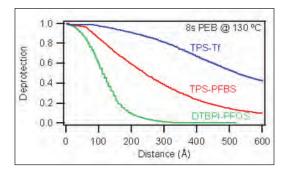

The deprotection reaction front profile was measured with nanometer resolution by combining neutron reflectivity and FTIR on a bilayer structure prepared with model 193 nm photoresists. The upper layer of the structure is loaded with the photoacid generator. Upon exposure and baking, the acid diffuses into the lower layer and catalyzes the deprotection reaction. The protecting group partially leaves the film, quantified by FTIR, upon reaction. The contrast to neutrons results from the reaction allowing for observation of the reaction front. By comparing the reaction front to the developed film profile, we obtain important insight into both the spatial extent of the reaction and the development process itself. These data are the first available with this spatial resolution and are critically needed for the development of process control over nanometer length scales. We find that the reaction front broadens with time while the surface roughness of the developed structure remains relatively sharp. Additionally, we find that the reaction front width is dependent upon resist chemistry and PAG size as shown in Fig. 3. These experimental data provide a rational design of next-generation photoresist component from the resist chemistry to the reaction-diffusion process.

Figure 3. Neutron reflectivity results of the nanometer scale deprotection profile shape dependence on photoacid generator size:

TPS-Tf < TPS-PFBS < DTBPI-PFOS. These high-resolution experimental data help verify current advanced reaction-diffusion models.

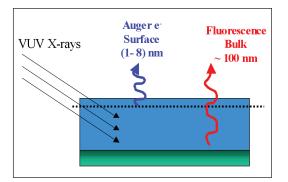

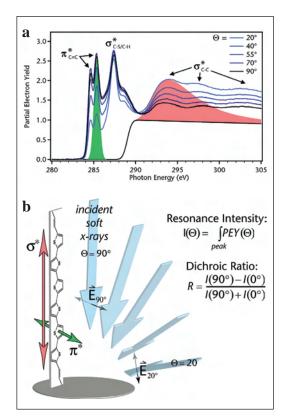

■ NEXAFS measurements were used to measure the surface concentration and depth profile of photoresist and BARC components and the surface reaction kinetics in model photoresist polymers as a function of common processing conditions. A significant advantage of the NEXAFS measurement is the capability of separating interfacial and bulk signals within the same sample and experiment in Fig. 4. NEXAFS measurements of interfacial chemistry are possible because of the limited escape depth of produced secondary electrons. By separately observing the electron and fluorescence yield, the chemistry at the surface (2 nm) and bulk (200 nm) may be determined.

Figure 4. Schematic diagram of the NEXAFS measurement geometry. Spectra are obtained from the film surface and bulk simultaneously.

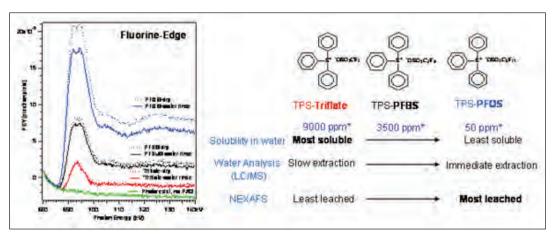

Different chemistries may be observed by examining the near-edge X-ray spectra of light elements such as carbon, oxygen, fluorine, and nitrogen. In this way, changes in the surface chemistry relative to the bulk film can be investigated as a function of lithographic processing steps such as exposure and heating. We have found that fluorinated PAG molecules preferentially segregate to the film surface. The relative amount of segregation is dependent upon the specific polymer chemistry and PAG size. In addition, NEXAFS analysis of residual layers arising from BARC-resist component transport and interactions enable detailed analysis of potential mechanisms leading to loss of profile control. UV exposure, post-exposure bake, and a novel atmosphere controlled chamber have been developed to test environmental stability against model airborne contaminants and influence on in-situ processing.

NEXAFS measurements were used to measure the surface concentration and depth profile of photoacid generators for advanced 193 nm photoresist materials for immersion lithography. These measurements quantify the influence of water immersion on the loss of these critical components. NEXAFS on wafer analysis combined with LC/MS demonstrate that equilibrium water solubility of PAGs with varying perfluoroalkyl length does not serve as the appropriate criteria for selecting PAGs for immersion lithography; rather the segregation of PAGs to the top few nanometers provides the majority of leaching as shown in Fig. 5. Additionally, the effects of critical top coats are also investigated to understand the segregation and retention of PAG additives.

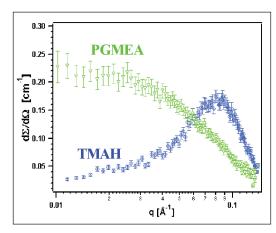

The development step selectively removes UV exposed photoresist material and represents the last step in the fabrication of nanostructures prior to semiconductor etch and deposition. With dimensions shrinking to sub-50 nm, control of line-edge roughness becomes more important and contributions to roughness from the development step requires an improved framework. In the development step, the aqueous base TMAH developer shifts the local chemical equilibrium from an unionized form to the ionized form, for instance in the 248 nm material poly(hydroxystyrene). SANS data, in Fig. 6, demonstrate the origin of the miscibility in aqueous base is due to the ionization of the photoresist leading to polyelectrolyte behavior. The identification of the presence of polyelectrolyte behavior during the development process provides an improved framework to understand the roles of added electrolytes, such as low molecular weight organic (tetramethylammonium chloride) and inorganic salts (NaCl, KCl). The addition of salts reduce the influence of polyelectrolyte behavior. Current experiments with different developing and rinsing protocols demonstrate that the pH of the rinse step is very important. This suggests the surface layer may contain polyelectrolyte effects even after development as demonstrated by an increase in surface RMS roughness for the development of bilayer samples with 0.26N TMAH followed by water rinse and 0.01 M HCl rinse.

Figure 5. NEXAFS fluorine-edge experimental results quantifying the extent of PAG loss from the surface due to water immersion. The series of PAGs tested for immersion lithography is shown as a function of equilibrium water solubility, extraction from thin films, and NEXAFS surface composition analysis.

Figure 6. SANS data from a model photoresist polymer in organic solvent (PGMEA) and the developer base solution (TMAH). The scattering peak in TMAH solution is representative of the polyelectrolyte behavior.

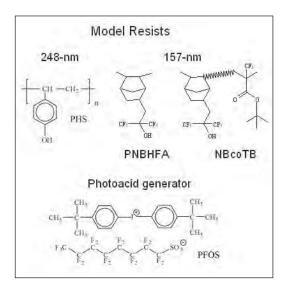

■ Characterization of local bulk scale mixing is necessary for understanding future photoresist materials as feature dimensions are reduced to sub-65 nm. The intimacy of mixing of PAG and photoresist was probed by solid state proton NMR methods based on inversion-recovery, solid-echo-spin-diffusion, and chemical-shift-based-spin-diffusion pulse sequences. The effect of PAG concentration on the dispersion and phase separation within bulk blends was found to depend strongly on the photoresist chemistry (see Fig. 7). In model 248 nm materials PFOS was found to mix on the molecular scale for loadings between 9 % and 45 %; hence the two components are thermodynamically miscible in this range.

Figure 7. Model 248 nm and 157 nm photoresist materials used to probe the intimacy of mixing of photoacid generator in blends by NMR methods.

These results were extended to a challenging 157 nm formulation and revealed that, while PFOS is miscible within the two photoresists, the ternary system exhibits phase separation into domains exceeding 30 nm.

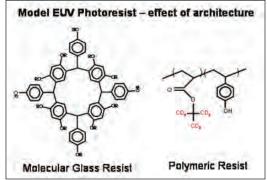

EUV photoresist polymers are expected for imaging at the 32 nm node and smaller. Similar to 193 nm the deprotection reaction front profile is a critical factor. However, in particular to EUV photoresists high PAG loading as well as lower EUV doses are expected. We applied neutron reflectivity to understand the effect of dose using model deuterated polymeric resists as shown in Fig. 8. The deprotection fronts exhibits two different length scales; a slow front that initiates high degrees of deprotection near the interface and a fast front that propagates into the resist with reaction-diffusion lengths consistent with those reported in the literature. However, the deprotection level and diffusion-length scale are exposure dose (photoacid concentration) dependent. The origin of the fast-diffusion front dependence on dose was hypothesized due to the increase in copolymer composition polarity as the reaction proceeds thereby limiting the spatial-extent. The evolving copolymer composition appears central in future modeling of latent image profiles. Neutron reflectivity was demonstrated to have sufficient chemical sensitivity and spatial resolution to measure the interfacial structure on sub-nm length scales. This approach can be extended to understand the effects of additives, such as photodegradable bases, as well as different architecture such as the molecular glass photoresists shown in Fig. 8. The effect of architecture or "pixel size" may also play a crucial role to higher fidelity imaging. We develop dissolution fundamentals to help quantify the effects of swelling and dissolution rate on the effect of resist architecture.

Figure 8. Two contrasting architectures of photoresist materials, but with similar chemistry: molecular glass and polymeric chemically amplified resist.

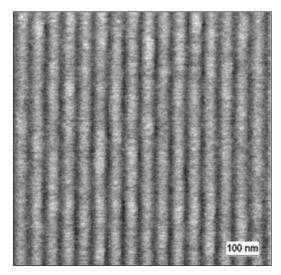

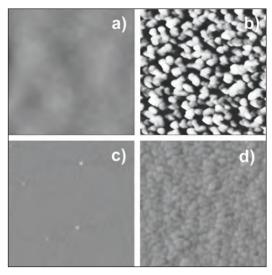

The Optical Technology Division is developing chemical force microscopy (CFM) to measure the surface spatial distribution of chemical species in the imaged resist. Using CFM, the homogeneity of the resist can be imaged with chemical contrast using specially prepared probe tips. This information complements the height images obtained with AFM. The distribution of PAG after exposure and deprotected polymer after PEB are of interest. The distribution of deprotected polymer is of particular interest to quantify LER by non-destructive imaging techniques at the nanometer length scale. Figure 9 shows a CFM image of an EUV-exposed PMMA thin film with 30 nm half pitch lines that has not been developed. The lighter areas are the unexposed PMMA.

Figure 9. Chemical Force Microscopy image on an EUV imaged PMMA thin film with 30 nm half-pitch lines.

### **C**OLLABORATIONS

Polymers Division, NIST – Bryan D. Vogt, Shuhui Kang, Ashwin Rao, David VanderHart, Kristopher Lavery

Ceramics Division, NIST – Sharadha Sambasivan, Daniel A Fischer

Center for Neutron Research, NIST - Sushil K. Satija

Optical Technology Division, NIST – John Woodward, Jeeseong Hwang

SEMATECH - Karen Turnquest

Intel - Kwang-Woo Choi (Assignee to NIST), George Thompson

IBM T. J. Watson Research Center - Dario L. Goldfarb

IBM Almaden Research Center – Hiroshi Ito, Robert D. Allen, William D. Hinsberg

AZ Electronics - Ralph Dammel, Frank Houlihan

DuPont Electronic Polymers L.P. – Jim Sounik, Michael T. Sheehan

Cornell University - Christopher Ober

SEMATECH - Agreement 309841 OF

Intel - CRADA 1893

### **RECENT PUBLICATIONS**

S. Kang, V. M. Prabhu, B. D. Vogt, E. K. Lin, W.-L. Wu, and K. Turnquest, "Copolymer fraction effect on acid catalyzed deprotection reaction kinetics in model 193 nm photoresists," Proceedings of the SPIE, Vol 6153, (2006).

B. D. Vogt, S. Kang, V. M. Prabhu, A. Rao, E. K. Lin, S. K. Satija, K. Turnquest, and W.-L. Wu. "The deprotection reaction front profile in model 193 nm methacrylate-based chemically amplified photoresists," Proceedings of the SPIE, Vol 6153, (2006).

K. A. Lavery, K.-W. Choi, B. D. Vogt, V. M. Prabhu, E. K. Lin, W.-L. Wu, S. K. Satija, M. J. Leeson, H. B. Cao, G. Thompson, D. S. Fryer "Fundamentals of the Reaction-Diffusion Process in Model EUV Photoresists," Proceedings of the SPIE, Vol 6153, (2006).

A. Rao, S. Kang, V. M. Prabhu, B. D. Vogt, V. M. Prabhu, E. K. Lin, W.-L. Wu, K. Turnquest, and W. D. Hinsberg, "Dissolution Fundamentals of 193 nm Methacrylate Based Photoresist," Proceedings of the SPIE, Vol 6153, (2006).

V. M. Prabhu, S. Sambasivan, D. A. Fischer, L. Sundberg, and R. D. Allen, "Quantitative depth profiling of photoacid generators in photoresist materials by near-edge X-ray absorption fine structure spectroscopy," accepted, App. Surf. Sci. (2006).

B. D. Vogt, C. L. Soles, C.-Y. Wang, V. M. Prabhu, P. M. McGuiggan, J. F. Douglas, E. K. Lin, W.-L. Wu, S. K. Satija, D. L. Goldfarb, M. Angelopoulos "Water immersion of model photoresists: interfacial influences on water concentration and surface morphology," Journal of Microlithography, Microfabrication, and Microsystems, 4(1), 013003 (2005).

B. D. Vogt, V. M. Prabhu, C. L. Soles, S. K. Satija, E. K. Lin, W.-L. Wu, "Control of moisture at buried polymer/alumina interfaces through substrate surface modification," Langmuir 21, 2460-2464 (2005).

V. M. Prabhu, B. D. Vogt, W.-L. Wu, E. K. Lin, J. F. Douglas, S. K. Satija, D. L. Goldfarb, and H. Ito, "Direct measurement of the counterion distribution within swollen polyelectrolyte films," Langmuir 74, 6647 (2005).

V. M. Prabhu and E. K. Lin, "Advanced Measurements for Photoresist Fundamentals," Semiconductor Fabtech International Quarterly, 24th Edition, 99 (2004).

D. L. VanderHart, V. M. Prabhu, E. K. Lin, "Proton NMR Determination of Miscibility in a Bulk Model Photoresist System: Poly(4-hydroxystyrene) and the Photoacid Generator, Di(t-butylphenyl) Iodonium Perfluorooctane Sulfonate," Chemistry of Materials, 16(16), 3074-3084 (2004).

V. M. Prabhu and E. K. Lin, "Advanced Measurements for Photoresist Fundamentals," Semiconductor Fabtech International Quarterly, 24, 99-103 (2004).

R. L. Jones, V. M. Prabhu, D. L. Goldfarb, E. K. Lin, C. L. Soles, J. L. Lenhart, W. Wu, and M. Angelopoulos, "Correlation of the Reaction Front with Roughness in Chemically Amplified Photoresists," ACS Symposium Series No. 874, "Polymers for Micro- and Nano-electronics," 86, (2004).

# CRITICAL DIMENSION AND OVERLAY METROLOGY PROGRAM

The principal productivity driver for the semiconductor manufacturing industry has been the ability to shrink linear dimensions. A key element of lithography is the ability to create reproducible undistorted images, both for masks and the images projected by these masks onto semiconductor structures. Lithography as a whole, fabricating the masks, printing and developing the images, and measuring the results, currently constitutes  $\approx 35$  % of wafer processing costs. The overall task of the Critical Dimension and Overlay Program is to assist the industry in providing the necessary metrology support for current and future generations of lithography technology. These goals include advances in modeling, the provision of next generation critical dimension and overlay artifacts, development of advanced critical dimension and overlay measurement techniques, and comparisons of different critical dimension and overlay measurement techniques.

Currently, critical dimension and overlay measurement improvements have barely kept up with lithography capabilities. To maintain cost effectiveness, continued advances need to be made.

# Wafer-Level and Mask Critical Dimension Metrology

This project is the single largest project at NIST supporting the semiconductor industry. It involves metrology and artifact development across a broad range of techniques. For this reason, the project is presented in a number of sub-sections, each focusing on a single technology. These are:

- Scanning Electron Microscope-Based Dimensional Metrology

- Scatterometry-Based Dimensional Metrology

- Scanning Probe Microscope-Based Dimensional Metrology

- Small Angle X-Ray Scattering-Based Dimensional Metrology

- Fabrication and Calibration Metrology for Single-Crystal CD Reference Materials

- Optical-Based Photomask Dimensional Metrology

- Model-Based Linewidth Metrology

- Atom-Based Dimensional Metrology

# SCANNING ELECTRON MICROSCOPE-BASED DIMENSIONAL METROLOGY

### GOALS

Provide the microelectronics industry with highly accurate scanning electron microscope (SEM) measurement and modeling methods for shapesensitive measurements and relevant calibration standards with nanometer-level resolution.

Carry out SEM metrology instrumentation development, including improvements in electron gun, detection, sample stage, and vacuum system.

Conduct research and development of new metrology techniques using digital imaging and networked measurement tools solutions to key metrology issues confronting the semiconductor lithography industry.

### CUSTOMER NEEDS

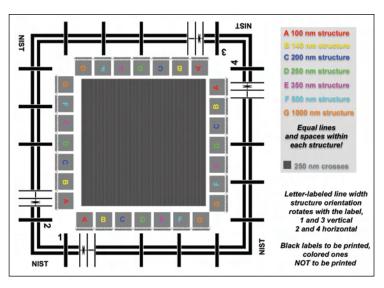

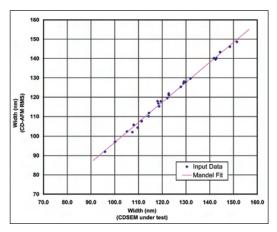

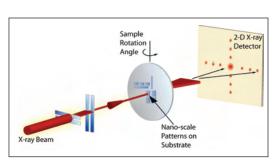

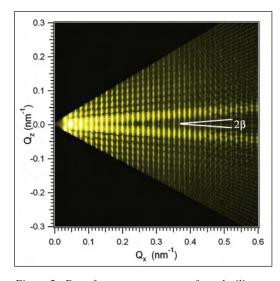

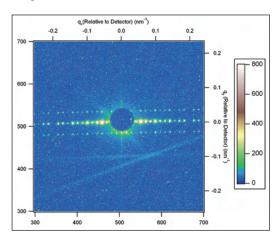

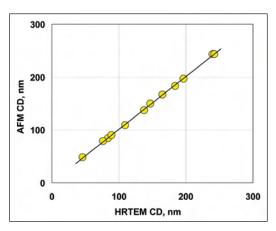

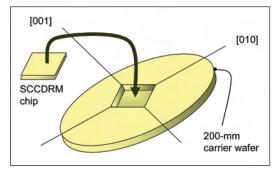

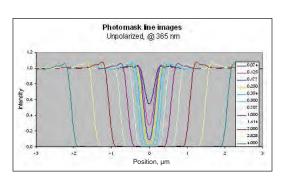

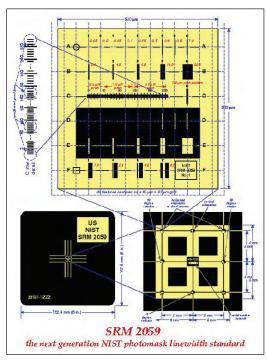

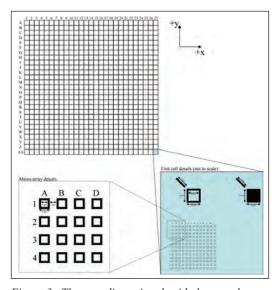

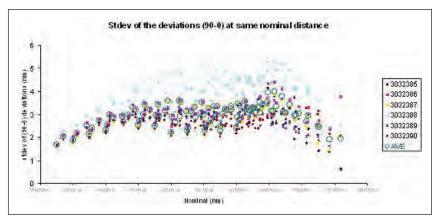

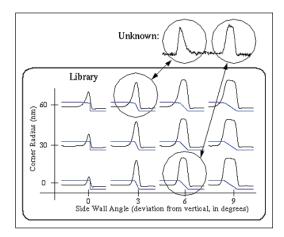

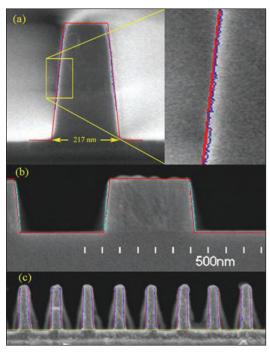

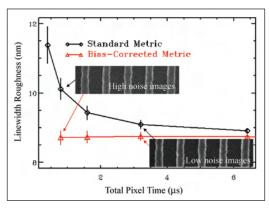

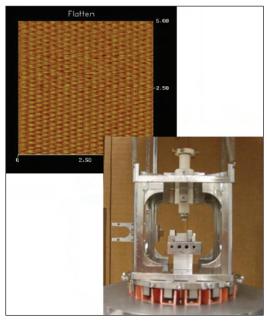

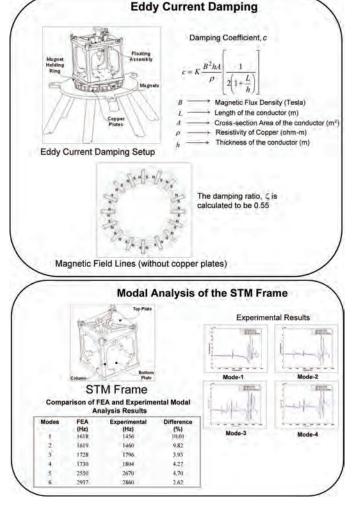

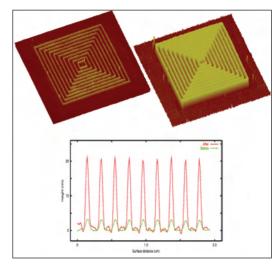

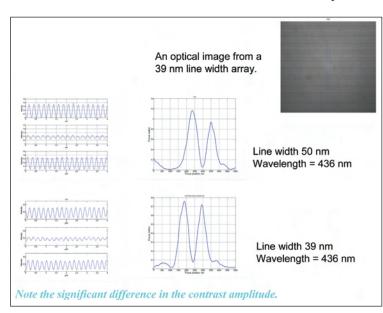

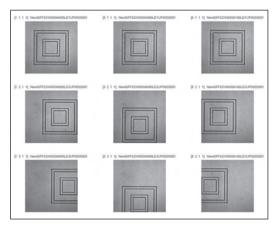

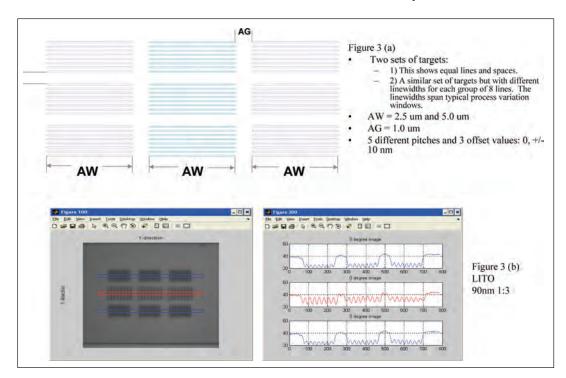

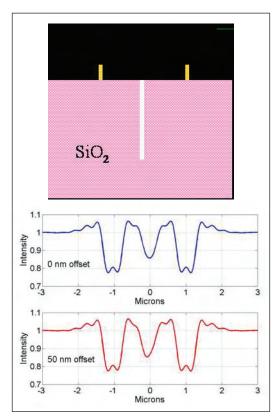

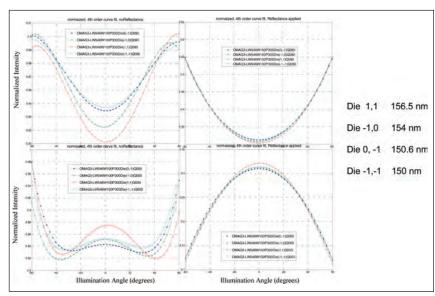

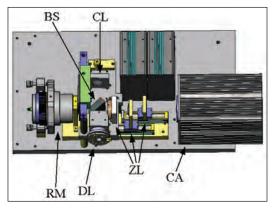

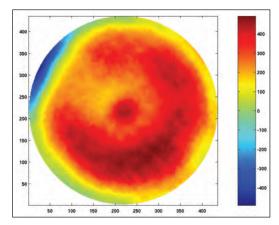

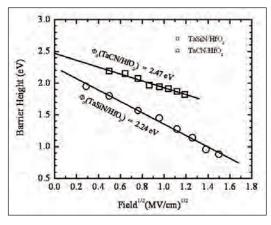

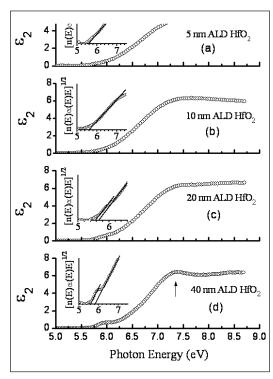

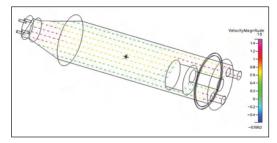

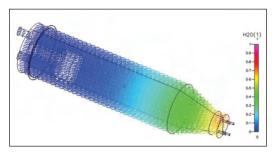

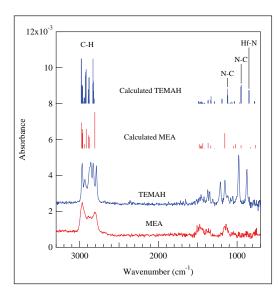

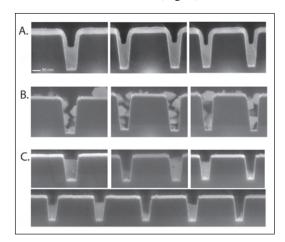

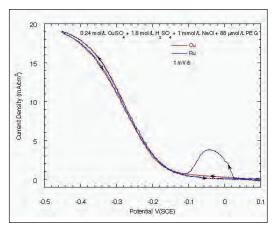

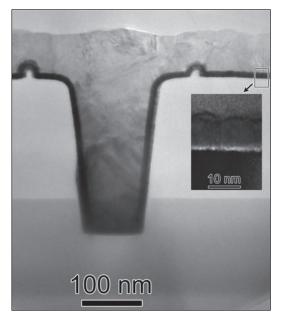

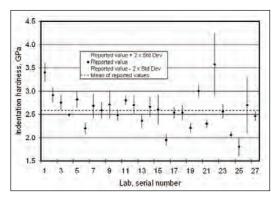

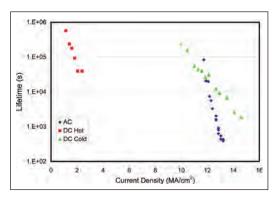

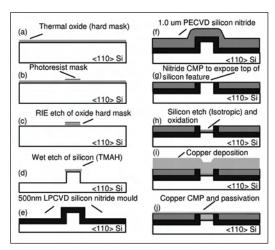

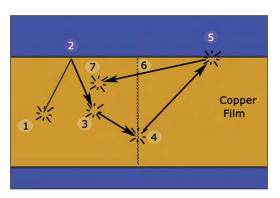

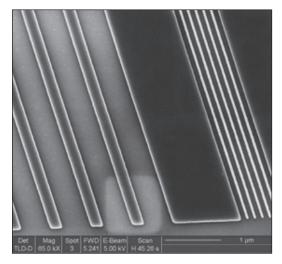

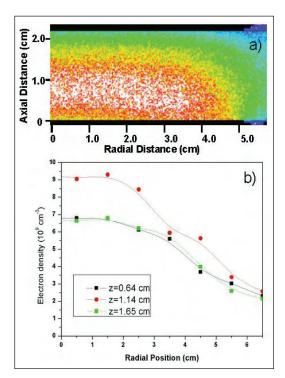

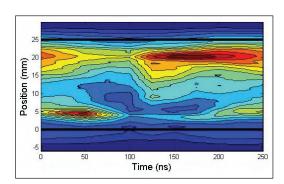

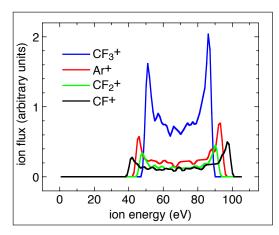

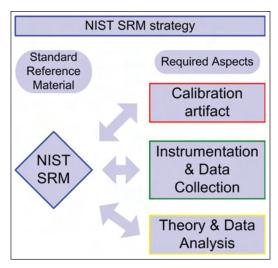

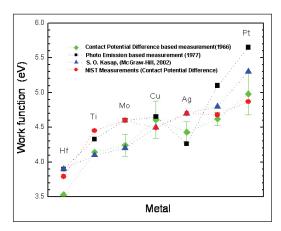

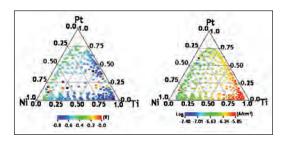

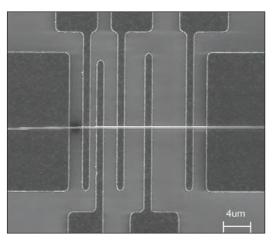

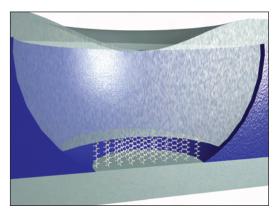

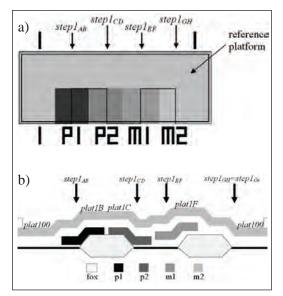

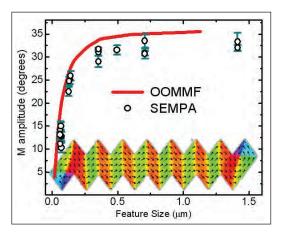

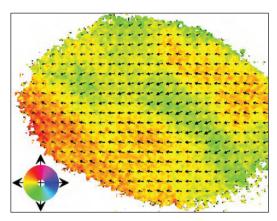

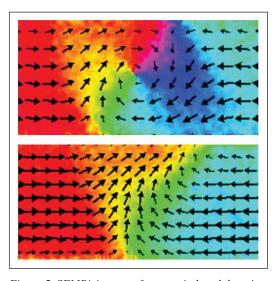

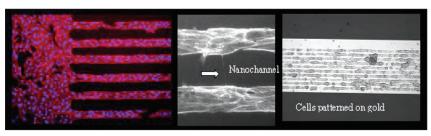

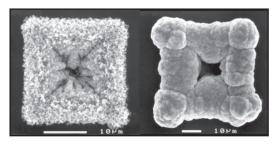

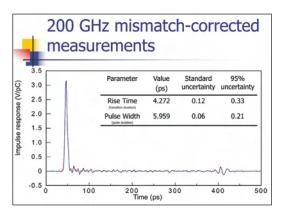

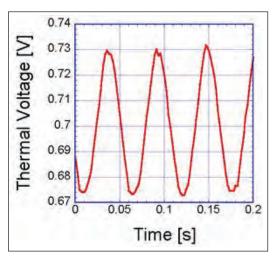

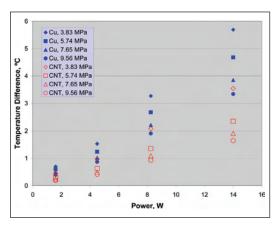

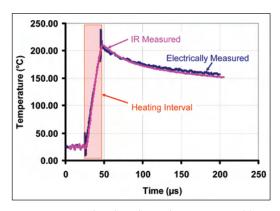

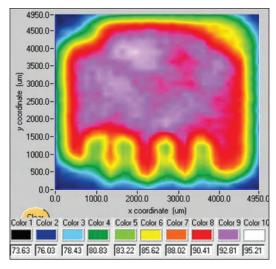

The scanning electron microscope is used extensively in many types of industry, including the more than \$200 billion semiconductor industry in the manufacture and quality control of semiconductor devices. The International Technology Roadmap for Semiconductors (2005) states that "Scanning Electron Microscopy continues to provide at-line and inline imaging for characterization of cross-sectional samples, particle and defect analysis, inline defect imaging (defect review), and critical dimension (CD) measurements. Improvements are needed for effective CD and defect review (and SEM detection in pilot