A BETTO ENERGE OFFICERE EXPENSE PROPERTY AND AN

## NES SPECIAL PUBLICATION 337

# Silvon Dovice Procesing

U.S.

DESYMMTMISSE

OF

COMMERCE

Nexional

Bureau

of

Standards

DATE DUE

|  | , |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

### Silicon Device Processing

Proceedings of a Symposium Held at Gaithersburg, Maryland June 2-3, 1970

Charles P. Marsden, Editor

Institute for Applied Technology National Bureau of Standards Washington, D.C. 20234

Under the Sponsorship of Committee F-1

of the

American Society for Testing and Materials

and

The National Bureau of Standards

S, National Bureau of Standards Special Publication 337

Nat. Bur. Stand. (U.S.), Spec. Publ. 337, 467 pages (Nov. 1970) CODEN: XNBSA

Issued November 1970

NATIONAL BUREAU OF STANDARDS

FEB 1 2 1971

L49905

QC/00

,U57

Library of Congress Catalog Card Number: 74-608543

### FOREWORD

The 20th anniversary of the development of the alloy junction, and the 15th anniversary of both commercial silicon devices and the founding of ASTM Committee F-1, was an appropriate time for this Symposium. NBS welcomed the opportunity to cosponsor, with Committee F-1, a meeting that should produce better understanding of both currently used and newer methods of silicon material characterization.

The rate of development of silicon devices has often exceeded the ability to measure their properties. Committee F-l has attempted to provide the leadership necessary for standardization of measurement methods, and, through symposia, vehicles for promoting discussion and understanding of such measurement methods.

Standard methods for material characterization are a major factor in the producer-consumer interface, and provide a common language in procurement. Standard methods also should provide the producer with greater product uniformity, and the consumer with increased reliability. The Federal Government, as a major consumer of silicon devices, has a profound interest in the advancement of measurement methodology, an area to which NBS contributes strongly through the efforts of its technical staff.

Lewis M. Branscomb Director

### **PREFACE**

This Symposium on Silicon Device Processing was held on June 2 - 3, 1970 at the National Bureau of Standards under the cosponsorship of this Bureau and Committee F-1 of the American Society for Testing and Materials. It consisted of seven sessions as detailed in the Index on page Vi to Viii.

The objective of the Symposium was to provide an opportunity for engineers and applied scientists actively engaged in the silicon device technology field to discuss the most advanced measurement methods for process control and materials characterization. The basic theme of the meeting was to stress the interdependence of measurements techniques, facilities, and materials as they relate to the overall problems of improving and advancing silicon device sciences and technologies.

Speakers were generally invited to talk on specific phases of the subject matter of the session, which usually concerned present work for which they had shown unusual competence and could be considered in the forefront of their field. The General Session consisted entirely of invited tutorial papers.

It is hoped that this proceedings will be an effective reference in its field. The information given in the evaluation of current measurement techniques as well as the exhaustive efforts in assembling evidence to prove their validity, should prove of lasting value.

Charles P. Marsden, Editor

### SYMPOSIUM COMMITTEE

- D. E. KOONTZ, Symposium Chairman Bell Telephone Laboratories Murray Hill, N. J.

- W. M. BULLIS, Member Organizing Committee National Bureau of Standards Washington, D. C.

- W. B. BURFORD III, Committee F-1 Vice Chairman Westinghouse Electric Corporation Baltimore, Md.

- J. W. CARLSON, Chairman Session II-A Monsanto Co. St. Peters, Mo.

- J. A. DWYER, Society Representative American Society for Testing and Materials Philadelphia, Pa.

- E. E. GARDNER, Chairman Session II-B

IBM

Essex Junction, Vt.

- F. GITTLER, Chairman Session III-A Bell Telephone Laboratories Allentown, Pa.

- D. C. GUPTA, Chairman Session III-B General Telephone and Electronics Corp. Woburn, Mass.

- C. P. MARSDEN, Chairman Arrangements and Publications National Bureau of Standards Washington, D. C.

- E. MENDEL, Chairman Session IV-B IBM Hopewell Junction, N. Y.

- J. OROSHNIK, Symposium Secretary and Chairman Session IV-A National Bureau of Standards Washington, D. C.

- R. I. SCACE, Committee F-1 Chairman General Electric Co. Auburn, N. Y.

- P. A. Schumann, Member Organizing Committee IBM

Hopewell Junction, N. Y.

### CONTENTS

| <u>Paper No</u> . |                                                                                                                                                                                                                                    | Page No |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 1.                | Welcoming Remarks<br>Dr. Lewis M. Branscomb, Director, National Bureau of Standards                                                                                                                                                | 1       |

| 2.                | Some Thoughts on How We Might Improve Our Materials and Process Work Dr. D. G. Thomas, Executive Director, Bell Telephone Laboratories                                                                                             | 3       |

|                   | SESSION I - GENERAL, CHAIRMAN - D. E. KOONTZ                                                                                                                                                                                       |         |

| 3.                | Crystallographic Imperfections as Related to Silicon Crystal Growth J. A. Lenard, IBM, Components Division                                                                                                                         | 11      |

| 4.                | A Review of Silicon Substrates Surface Preparation and Evaluation K. E. Lemons, Signetics Corporation Paper Withdrawn from Publication                                                                                             | -       |

| 5.                | Epitaxial Growth of Silicon B. A. Joyce, Mullard Research Laboratories                                                                                                                                                             | 19      |

| 6.                | Diffusion in Silicon: Properties and Techniques C. F. Gibbon, Bell Telephone Laboratories, Inc.                                                                                                                                    | 21      |

| 7.                | Measurement and Control of Dielectric Film Properties During Semiconductor Device Processing B. E. Deal, Fairchild Camera and Instrument                                                                                           | 36      |

|                   | SESSION II-A - EPITAXY-TECHNIQUES AND FACILITIES, CHAIRMAN - J. W. CARLSON                                                                                                                                                         |         |

| 8.                | Equipment Considerations for Silicon Epitaxy Reactors M. L. Hammond and W. P. Cox, Hugle Industires, Inc.                                                                                                                          | 51      |

| 9.                | A Comparison of a Resistance Heated Reactor for Silicon Epitaxial Growth With Other Epitaxial Systems<br>W. A. Kohler, Fairchild Camera and Instrument Corp.                                                                       | 60      |

| 10.               | Techniques for Depositing Highly Uniform and Defect-Free Epitaxial Silicon D. C. Gupta, The Waltham Research Center of the General Telephone and Electronics Laboratories, Inc. and J. L. Porter, Sylvania Electric Products, Inc. | 66      |

| 11.               | Control of Thin Silicon Films Grown From Silane D. J. Dumin, RCA Laboratories                                                                                                                                                      | 79      |

| 12.               | The Growth of Submicron Single and Multilayer Silicon Epitaxy J. Simpson, A. C. Adams and M. H. Hanes, Bell Telephone Laboratories, Inc.                                                                                           | 87      |

|                   | SESSION II-B - DIFFUSION-PROPERTIES CHARACTERISTICS, CHAIRMAN - E. E. GARDNER                                                                                                                                                      |         |

| 13.               | Techniques for Determining Surface Concentration of Diffusants J. C. Irvin, Bell Telephone Laboratories                                                                                                                            | 99      |

| 14.               | Current Status of the Spreading Resistance Probe and Its Application T. H. Yeh, IBM Components Division                                                                                                                            | 111     |

| 15.               | Incremental Sheet Resistivity Technique for Determining Diffusion Profiles R. P. Donovan and R. A. Evans, Research Triangle Institute                                                                                              | 123     |

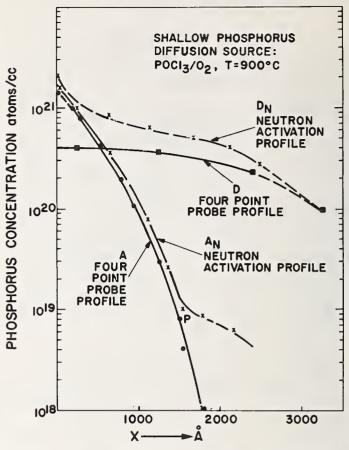

| 16.               | Nuclear Methods for the Determination of Diffusion Profiles B. J. Masters, IBM Components Division                                                                                                                                 | 132     |

| 17.               | Use of High-Energy Ion Beams for Analysis of Doped Surface Layers S. L. Chou, L. A. Davidson and J. F. Gibbons, Stanford Electronics Laboratories                                                                                  | 141     |

| Paper No. |                                                                                                                                                                                                      | Page No |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 18.       | Determination of Diffusion Coefficients in Silicon and Accepted Values<br>M. F. Millea, Aerospace Corporation                                                                                        | 156     |

|           | SESSION III-A - DIFFUSION-TECHNIQUES AND FACILITIES, CHAIRMAN - F. L. GITTLER                                                                                                                        | *       |

| 19.       | Diffusion Technology For Advanced Microelectronic Processing<br>W. Greig, K. Cunniff, H. Hyman and S. Muller, RCA Solid State Division                                                               | 168     |

| 20.       | Diffusion From Doped-Oxide Sources<br>M. L. Barry, Fairchild Camera and Instrument Corporation                                                                                                       | 175     |

| 21.       | Capacitance-A Device Parameter and Tool for Measuring Doping Profiles B. R. Chawla, Bell Telephone Laboratories, Inc.                                                                                | 182     |

| 22.       | Concentration Dependent Diffusion Phenomena<br>P. E. Bakeman, Jr., Rensselaer Research Corporation and J. M. Borrego,<br>Rensselaer Polytechnic Institute                                            | 184     |

| 23.       | Orientation Dependent Diffusion Phenomena<br>L. E. Katz, Bell Telephone Laboratories, Inc.                                                                                                           | 192     |

| 24.       | Diffusion Inducted Defects and Diffusion Kinetics in Silicon M. L. Joshi, IBM, Components Division and S. Dash, Fairchild Semiconductor                                                              | 202     |

|           | SESSION III-B - EPITAXY-PROPERTIES AND CHARACTERISTICS, CHAIRMAN - D. C. GUPTA                                                                                                                       |         |

| 25.       | Limitations of Current Epitaxial Evaluations (Abstract Only) R. N. Tucker, Fairchild Semiconductor. Paper Withdrawn from Publication                                                                 | . 223   |

| 26.       | On the Interpretation of Some Measurement Methods for Epitaxially Grown Layers P. J. Severin, Philips Research Laboratories                                                                          | 224     |

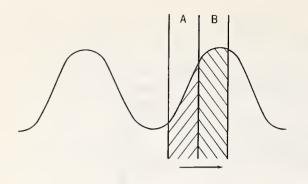

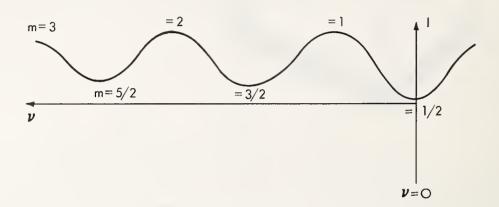

| 27.       | Thickness Measurement of Very Thin Epitaxial Layers by Infrared Reflectance P. A. Schumann, Jr., IBM Components Division                                                                             | 234     |

| 28.       | Spreading Resistance Measurements on Buried Layers in Silicon Structures R. G. Mazur, Westinghouse Research Laboratories                                                                             | 244     |

| 29.       | Variations of a Basic Capacitance-Voltage Technique for Determination of Impurity Profiles in Semiconductors<br>W. C. Niehaus, W. vanGelder, T. D. Jones and P. Langer, Bell Telephone Laboratories  | 256     |

| 31.       | Structural Faults in Epitaxial and Buried Layers in Silicon in Device Fabrication P. Wang, F. X. Pink and D. C. Gupta, General Telephone and Electronics Laboratories                                | 285     |

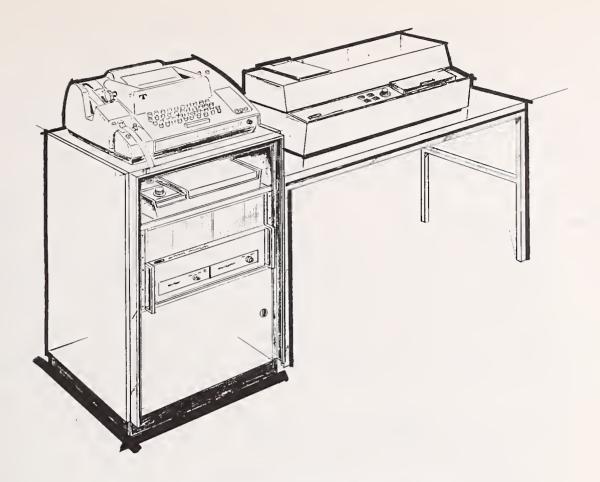

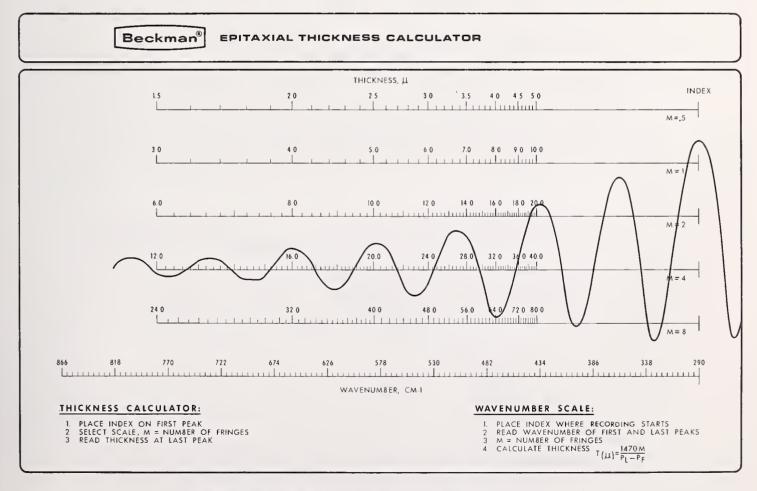

| 32.       | An Instrument for Automatic Measurement of Epitaxial Layer Thickness<br>A. C. Roddan, Beckman Instruments, Inc. and V. Vizir, Fairchild Semiconductor                                                | 302     |

| 30.       | A New Impurity Profile Plotter for Epitaxy and Devices B. J. Gordon and H. L. Stover, University of Southern California and R. S. Harp, California Institute of Technology                           | 273     |

|           | SESSION IV-A - INTERDEPENDENCE OF UNIT PROCESSING OPERATIONS, CHAIRMAN - J. OROSHNIK                                                                                                                 | (       |

| 33.       | A Statistical Approach to the Design and Fabrication of Diffused Junction Transistors D. P. Kennedy, IBM, Components Division Previously published in IBM J. of R and D $\underline{8}$ , 482 (1964) | •       |

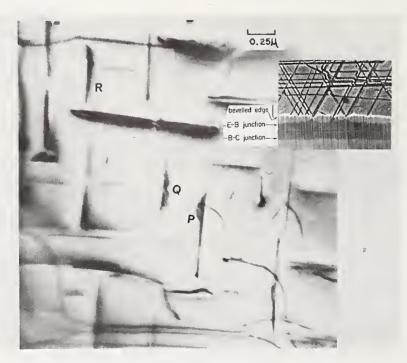

| 34.       | Defects Induced in Silicon Through Device-Processing M. L. Joshi and J. K. Howard, IBM, Components Division                                                                                          | 313     |

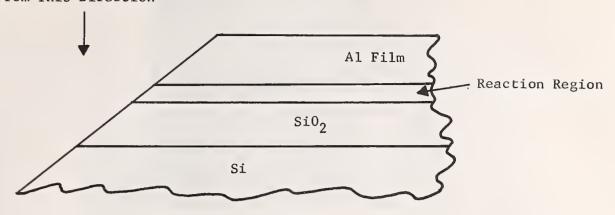

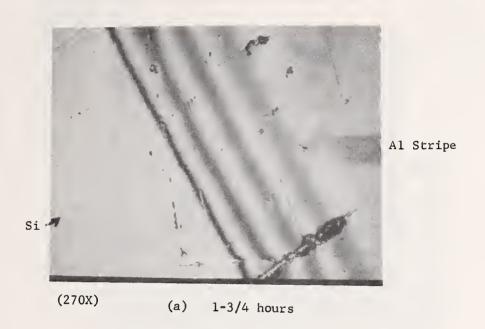

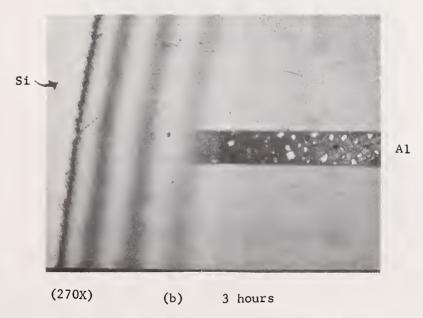

| 35.       | A Study Relating MOS Processes to a Model of the Al-SiO <sub>2</sub> -Si System M. H. White, F. C. Blaha and D. S. Herman, Westinghouse Corporation                                                  | 365     |

| Paper No. |                                                                                                                                                                                                   | Page No. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 36.       | Activation Analysis in Silicon Device Processing<br>G. B. Larrabee and H. G. Carlson, Texas Instruments, Inc.                                                                                     | 375      |

| 37.       | The Use of the Scanning Electron Microscope as a Semiconductor Device Production Line Quality Control Tool J. W. Adolphsen and R. J. Anstead, NASA Goddard Space Flight Center.                   | 384      |

| 38.       | Metallization Deposition Parameters and Their Effect on Device Performance J. R. Black, Motorola, Inc.                                                                                            | 398      |

| 39.       | Methods for Determination of the Characteristics of Hyper-pure Semiconductor<br>Silicon and Their Information Content for Device Production<br>Fritz G. Vieweg-Gutberlet, Wacker Chemitronic GMBH | 409      |

|           | SESSION IV-B - SURFACE PREPARATION, CHAIRMAN - E. MENDEL                                                                                                                                          |          |

| 40.       | Mechanical Damage-Its Role in Silicon Surface Preparation R. B. Soper, Semiconductor Processing Co., Inc.                                                                                         | 412      |

| 41.       | Crystallographic Damage to Silicon By Typical Slicing, Lapping, and Polishing Operations T. M. Buck and R. L. Meek, Bell Telephone Laboratories                                                   | 419      |

| 42.       | The Preparation of Practical, Stabilized Surfaces for Silicon Device Fabrication A. Mayer and D. A. Puotinen, RCA Corporation                                                                     | 431      |

| 43.       | Surface Contamination J. W. Faust, Jr., University of South Carolina                                                                                                                              | 436      |

| 44.       | The Precipitation of Oxygen in Silicon and Its Effect on Surface Perfection W. J. Patrick, IBM, Components Division                                                                               | 442      |

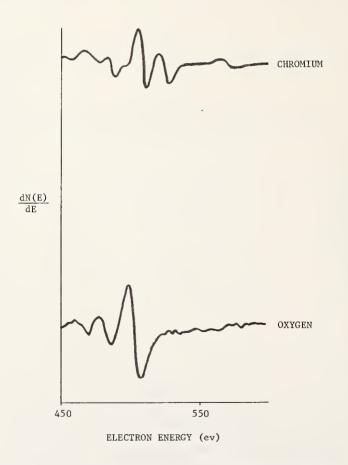

| 45.       | Auger Spectroscopy and Silicon Surfaces J. H. Affleck, General Electric Company                                                                                                                   | 450      |

| 46.       | Characterization of Semiconductor Surfaces and Interfaces by Ellipsometry  N. M. Bashara, University of Nebraska                                                                                  | 457      |

### AUTHOR INDEX

| Adams, A. C. 87 Irvin, J. C. 99 Adolphsen, John W. 384 Jones, T. D. 256 Affleck, J. H. 450 Joshf, M. L. 202, 313 Anstead, Robert J. 384 Joyce, B. A. 19 Bakeman, P. E., Jr. 184 Katz, L. E. 192 Barry, M. L. 175 Kohler, William A. 60 Bashara, N. M. 457 Langer, P. 256 Black, J. R. 398 Larrabee, Graydon B. 375 Blaha, Franklyn C. 365 Lenard, J. A. 11 Borrego, J. M. 184 Masters, B. J. 132 Branscomb, L. M. 1 Mayer, A. 431 Buck, T. M. 419 Mazur, R. G. 244 Carlson, H. Gary 375 Meek, R. L. 419 Chawla, B. R. 182 Millea, M. F. 156 Chou, S. L. 141 Muller, S. 168 Cox, W. P. 51 Nichaus, W. C. 256 Cunniff, K. 168 Patrick, William J. 442 Dash, S. 202 Pink, F. X. 285 Davidson, L. A. 141 Porter, John L. 66 Deal, Bruce E. 36 Puotinen, D. A. 431 Donovan, R. P. 123 Roddan, Allison 302 Dumin, D. J. 79 Schumann, P. A., Jr. 234 Faust, J. W., Jr. 436 Simpson, J. 87 Gibbons, J. F. 141 Stover, B. L. 273 Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 66, 285 Van Gelder, W. 225 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hammond, M. L. 18 Norman, P. S. 110 Harp, R. S. 273 Wang, P. 285 Herman, David S. 110 Harp, R. S. 118 Harmon, W. H. 168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Author            | Page    | Author                  | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|-------------------------|------|

| Adolphsen, John W. 384 Jones, T. D. 256 Affleck, J. H. 450 Joshi, M. L. 202, 313 Anstead, Robert J. 384 Joyce, B. A. 19 Bakeman, P. E., Jr. 184 Katz, L. E. 192 Barry, M. L. 175 Kohler, Milliam A. 60 Bashara, N. M. 457 Langer, P. 256 Black, J. R. 398 Larrabee, Graydon B. 375 Blaha, Franklyn C. 365 Lenard, J. A. 11 Borrego, J. M. 184 Masters, B. J. 132 Branscomb, L. M. 1 Mayer, A. 431 Buck, T. M. 419 Mazur, R. G. 244 Carlson, H. Gary 375 Meck, R. L. 419 Chawla, B. R. 182 Millea, M. F. 156 Chou, S. L. 141 Muller, S. 168 Cox, W. P. 51 Nichaus, W. C. 256 Cunniff, K. 168 Patrick, William J. 442 Dash, S. 202 Pink, F. X. 285 Davidson, L. A. 141 Porter, John L. 66 Deal, Bruce E. 36 Puotinen, D. A. 431 Donovan, R. P. 123 Roddan, Allison 302 Dumín, D. J. 79 Schunann, P. A., Jr. 234 Evans, R. A. 123 Severin, P. J. 224 Faust, J. W., Jr. 436 Simpson, J. 87 Gibbon, C. F. 21 Soper, R. B. 412 Gordon, E. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Gupta, D. C. 66, 285 Wan Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Harp, R. S. 273 Wang, P. 285 Herman, David S. 161 Howard, J. K. 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Adams A C         | 87      | Irvin I C               | 00   |

| Affleck, J. H. 450 Joshi, M. L. 202, 313 Anstead, Robert J. 384 Joyce, B. A. 19 Bakeman, P. E., Jr. 184 Katz, L. E. 192 Barry, M. L. 175 Kohler, William A. 60 Bashara, N. M. 457 Langer, P. 256 Black, J. R. 398 Larrabec, Graydon B. 375 Blaha, Franklyn C. 365 Lenard, J. A. 11 Borrego, J. M. 184 Masters, B. J. 132 Branscomb, L. M. 1 Mayer, A. 431 Bruck, T. M. 419 Mazur, R. G. 244 Carlson, H. Gary 375 Meek, R. L. 419 Chawla, B. R. 182 Millea, M. F. 156 Chou, S. L. 141 Muller, S. 168 Cox, W. P. 51 Niehaus, W. C. 256 Cunniff, K. 168 Patrick, William J. 442 Dash, S. 202 Pink, F. X. 285 Davidson, L. A. 141 Porter, John L. 66 Deal, Bruce E. 36 Puotinen, D. A. 234 Evans, R. P. 123 Roddan, Allison 302 Dumin, D. J. 79 Schumann, P. A., Jr. 234 Evans, R. A. 123 Severin, P. J. 224 Faust, J. W., Jr. 436 Simpson, J. 87 Gibbon, C. F. 21 Soper, R. B. 412 Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Gueta, D. C. 66, 285 Van Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Harp, R. S. 273 Wang, P. 285 Herman, David S. 365 White, Marvin H. 365 Howard, J. K. 111 Harbert Aspendicular and the property of the |                   |         |                         |      |

| Anstead, Robert J. 384 Joyce, B. A. 19 Bakeman, P. E., Jr. 184 Katz, L. E. 192 Barry, M. L. 175 Kohler, William A. 60 Bashara, N. M. 457 Langer, P. 256 Black, J. R. 398 Larrabee, Graydon B. 375 Blaha, Franklyn C. 365 Lenard, J. A. 11 Borrego, J. M. 184 Masters, B. J. 132 Branscomb, L. M. 1 Mayer, A. 431 Buck, T. M. 419 Mazur, R. G. 244 Carlson, H. Gary 375 Meek, R. L. 419 Chavla, B. R. 182 Millea, M. F. 156 Chou, S. L. 141 Muller, S. 168 Cox, W. P. 51 Niehaus, W. C. 256 Cunniff, K. 168 Patrick, William J. 442 Dash, S. 202 Pink, F. X. 285 Davidson, L. A. 141 Porter, John L. 66 Deal, Bruce E. 36 Puotinen, D. A. 431 Donovan, R. P. 123 Roddan, Allison 302 Dumin, D. J. 79 Schumann, P. A., Jr. 234 Evans, R. A. 123 Severin, P. J. 224 Faust, J. W., Jr. 436 Simpson, J. 87 Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Cupta, D. C. 66, 285 Van Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hanes, M. H. 87 Vizir, Vitali 302 Harp, R. S. 273 Wang, P. 285 Herman, David S. 365 White, Marvin H. 311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |         |                         |      |

| Bakeman, P. E., Jr.         184         Katz, L. E.         192           Barry, M. L.         175         Kohler, William A.         60           Bashara, N. M.         457         Langer, P.         256           Black, J. R.         398         Larrabee, Graydon B.         375           Blaha, Franklyn C.         365         Lenard, J. A.         11           Borrego, J. M.         184         Masters, B. J.         132           Branscomb, L. M.         1         Mayer, A.         431           Buck, T. M.         419         Mazur, R. G.         244           Carlson, H. Gary         375         Meek, R. L.         419           Chavla, B. R.         182         Millea, M. F.         156           Chou, S. L.         141         Multer, S.         168           Cox, W. P.         51         Niehaus, W. C.         256           Cunniff, K.         168         Patrick, William J.         442           Dash, S.         202         Pink, F. X.         285           Davidson, L. A.         141         Porter, John L.         66           Deal, Bruce E.         36         Puotinen, D. A.         431           Donovan, R. P.         123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |         |                         |      |

| Barry, N. L.         175         Kohler, William A.         60           Bashara, N. M.         457         Langer, P.         256           Black, J. R.         398         Larrabee, Graydon B.         375           Blaha, Franklyn C.         365         Lenard, J. A.         11           Borrego, J. M.         184         Masters, B. J.         132           Branscomb, L. M.         1         Mayer, A.         431           Buck, T. M.         419         Mazur, R. G.         244           Carlson, H. Gary         375         Meek, R. L.         419           Chawla, B. R.         182         Millea, M. F.         156           Chou, S. L.         141         Muller, S.         168           Cox, W. P.         51         Niehaus, W. C.         256           Cunniff, K.         168         Patrick, William J.         442           Dash, S.         202         Pink, F. X.         285           Davidson, L. A.         141         Porter, John L.         66           Deal, Bruce E.         36         Puotinen, D. A.         431           Donovan, R. P.         123         Roddan, Allison         302           Evans, R. A.         123 <th< td=""><td></td><td></td><td></td><td></td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |         |                         |      |

| Bashara, N. M.         457         Langer, P.         256           Black, J. R.         398         Larrabee, Graydon B.         375           Blaha, Franklyn C.         365         Lenard, J. A.         11           Borrego, J. M.         184         Masters, B. J.         132           Branscomb, L. M.         1         Mayer, A.         431           Buck, T. M.         419         Mazur, R. G.         244           Carlson, H. Gary         375         Meek, R. L.         419           Chavla, B. R.         182         Millea, M. F.         156           Chou, S. L.         141         Muller, S.         168           Cox, W. P.         51         Niehaus, W. C.         256           Cunniff, K.         168         Patrick, William J.         442           Dash, S.         202         Pink, F. X.         285           Davidson, L. A.         141         Porter, John L.         66           Deal, Bruce E.         36         Puotinen, D. A.         431           Donovan, R. P.         123         Roddan, Allison         302           Pumin, D. J.         79         Schumann, P. A., Jr.         234           Evans, R. A.         123         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |         |                         |      |

| Black, J. R.       398       Larrabee, Graydon B.       375         Blaha, Franklyn C.       365       Lenard, J. A.       11         Borrego, J. M.       184       Masters, B. J.       132         Branscomb, L. M.       1       Mayer, A.       431         Buck, T. M.       419       Mazur, R. G.       244         Carlson, H. Gary       375       Meek, R. L.       419         Chawla, B. R.       182       Millea, M. F.       156         Chou, S. L.       141       Muller, S.       168         Cox, W. P.       51       Niehaus, W. C.       256         Cunniff, K.       168       Patrick, William J.       442         Dash, S.       202       Pink, F. X.       285         Davidson, L. A.       141       Porter, John L.       66         Deal, Bruce E.       36       Puotinen, D. A.       431         Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Sop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |         |                         |      |

| Blaha, Franklyn C.       365       Lenard, J. A.       11         Borrego, J. M.       184       Masters, B. J.       132         Branscomb, L. M.       1       Mayer, A.       431         Buck, T. M.       419       Mazur, R. G.       244         Carlson, H. Gary       375       Meek, R. L.       419         Chavla, B. R.       182       Millea, M. F.       156         Chou, S. L.       141       Muller, S.       168         Cox, W. P.       51       Niehaus, W. C.       256         Cunniff, K.       168       Patrick, William J.       442         Dash, S.       202       Pink, F. X.       285         Davidson, L. A.       141       Porter, John L.       66         Deal, Bruce E.       36       Puotinen, D. A.       431         Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbons, J. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stoverin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |         | g ,                     |      |

| Borrego, J. M. 184 Masters, B. J. 132 Branscomb, L. M. 1 Mayer, A. 431 Buck, T. M. 419 Mazur, R. G. 244 Carlson, H. Gary 375 Meek, R. L. 419 Chawla, B. R. 182 Millea, M. F. 156 Chou, S. L. 141 Muller, S. 168 Cox, W. P. 51 Niehaus, W. C. 256 Cunniff, K. 168 Patrick, William J. 442 Dash, S. 202 Pink, F. X. 285 Davidson, L. A. 141 Porter, John L. 66 Deal, Bruce E. 36 Puotinen, D. A. 431 Donovan, R. P. 123 Roddan, Allison 302 Dumín, D. J. 79 Schumann, P. A., Jr. 234 Evans, R. A. 123 Severin, P. J. 224 Faust, J. W., Jr. 436 Simpson, J. 87 Gibbon, C. F. 21 Soper, R. B. 412 Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Gupta, D. C. 66, 285 Van Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hanes, M. H. 87 Vizir, Vitali 302 Harp, R. S. 273 Wang, P. 285 Herman, David S. 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |         |                         |      |

| Branscomb, L. M. 419 Mazur, R. G. 244  Carlson, H. Gary 375 Meek, R. L. 419  Chawla, B. R. 182 Millea, M. F. 156  Chou, S. L. 141 Muller, S. 168  Cox, W. P. 51 Niehaus, W. C. 256  Cunniff, K. 168 Patrick, William J. 442  Dash, S. 202 Pink, F. X. 285  Davidson, L. A. 141 Porter, John L. 66  Deal, Bruce E. 36 Puotinen, D. A. 431  Donovan, R. P. 123 Roddan, Allison 302  Dumín, D. J. 79 Schumann, P. A., Jr. 234  Evans, R. A. 123 Severin, P. J. 224  Faust, J. W., Jr. 436 Simpson, J. 61  Gibbons, J. F. 21 Soper, R. B. 412  Gibbons, J. F. 21 Soper, R. B. 412  Gibbons, J. F. 141 Stover, H. L. 273  Gordon, B. J. 273 Thomas, D. G. 3  Greig, W. 168 Tucker, R. N. 223  Gupta, D. C. 66, 285 Van Gelder, W. 409  Hanes, M. H. 87 Vizir, Vitali 302  Harp, R. S. 273 Wang, P. 285  Herman, David S. 365 White, Marvin H. 365  Howard, J. K. 313 Yeh, T. H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |         |                         |      |

| Buck, T. M.       419       Mazur, R. G.       244         Carlson, H. Gary       375       Meek, R. L.       419         Chawla, B. R.       182       Millea, M. F.       156         Chou, S. L.       141       Muller, S.       168         Cox, W. P.       51       Niehaus, W. C.       256         Cunniff, K.       168       Patrick, William J.       442         Dash, S.       202       Pink, F. X.       285         Davidson, L. A.       141       Porter, John L.       66         Deal, Bruce E.       36       Puotinen, D. A.       431         Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |         |                         |      |

| Carlson, H. Gary 375 Meek, R. L. 419 Chawla, B. R. 182 Millea, M. F. 156 Chou, S. L. 141 Muller, S. 168 Cox, W. P. 51 Niehaus, W. C. 256 Cunniff, K. 168 Patrick, William J. 442 Dash, S. 202 Pink, F. X. 285 Davidson, L. A. 141 Porter, John L. 66 Deal, Bruce E. 36 Puotinen, D. A. 431 Donovan, R. P. 123 Roddan, Allison 302 Dumin, D. J. 79 Schumann, P. A., Jr. 234 Evans, R. A. 123 Severin, P. J. 224 Faust, J. W., Jr. 436 Simpson, J. 87 Gibbon, C. F. 21 Soper, R. B. 412 Gibbons, J. F. 141 Stover, H. L. 273 Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Gupta, D. C. 66, 285 Van Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hanes, M. H. 87 Vizir, Vitali 302 Harp, R. S. 273 Wang, P. 285 Herman, David S. 365 White, Marvin H. 365 Howard, J. K. 313 Yeh, T. H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |         |                         |      |

| Chawla, B. R. 182 Millea, M. F. 156 Chou, S. L. 141 Muller, S. 168 Cox, W. P. 51 Niehaus, W. C. 256 Cunniff, K. 168 Patrick, William J. 442 Dash, S. 202 Pink, F. X. 285 Davidson, L. A. 141 Porter, John L. 66 Deal, Bruce E. 36 Puotinen, D. A. 431 Donovan, R. P. 123 Roddan, Allison 302 Dumin, D. J. 79 Schumann, P. A., Jr. 234 Evans, R. A. 123 Severin, P. J. 224 Faust, J. W., Jr. 436 Simpson, J. 87 Gibbon, C. F. 21 Soper, R. B. 412 Gibbons, J. F. 141 Stover, H. L. 273 Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Gupta, D. C. 66, 285 Van Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hanes, M. H. 87 Vizir, Vitali 302 Harp, R. S. 273 Wang, P. 285 Herman, David S. 365 White, Marvin H. 365 Howard, J. K. 313 Yeh, T. H. 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |         |                         |      |

| Chou, S. L. 141 Muller, S. 168  Cox, W. P. 51 Niehaus, W. C. 256  Cunniff, K. 168 Patrick, William J. 442  Dash, S. 202 Pink, F. X. 285  Davidson, L. A. 141 Porter, John L. 66  Deal, Bruce E. 36 Puotinen, D. A. 431  Donovan, R. P. 123 Roddan, Allison 302  Dumin, D. J. 79 Schumann, P. A., Jr. 234  Evans, R. A. 123 Severin, P. J. 224  Faust, J. W., Jr. 436 Simpson, J. 87  Gibbon, C. F. 21 Soper, R. B. 412  Gibbons, J. F. 141 Stover, H. L. 273  Gordon, B. J. 273 Thomas, D. G. 3  Greig, W. 168 Tucker, R. N. 223  Gupta, D. C. 66, 285 Van Gelder, W. 256  Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409  Hanes, M. H. 87 Vizir, Vitali 302  Harp, R. S. 273 Wang, P. 285  Herman, David S. 365 White, Marvin H. 365  Howard, J. K. 313 Yeh, T. H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |         |                         |      |

| Cox, W. P.       51       Niehaus, W. C.       256         Cunniff, K.       168       Patrick, William J.       442         Dash, S.       202       Pink, F. X.       285         Davidson, L. A.       141       Porter, John L.       66         Deal, Bruce E.       36       Puotinen, D. A.       431         Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313 <t< td=""><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |         |                         |      |

| Cunniff, K.       168       Patrick, William J.       442         Dash, S.       202       Pink, F. X.       285         Davidson, L. A.       141       Porter, John L.       66         Deal, Bruce E.       36       Puotinen, D. A.       431         Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313       Yeh, T. H.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |         |                         |      |

| Dash, S.       202       Pink, F. X.       285         Davidson, L. A.       141       Porter, John L.       66         Deal, Bruce E.       36       Puotinen, D. A.       431         Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Hanes, M. H.       87       Vizir, Vitali       302         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313       Yeh, T. H.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |         |                         |      |

| Davidson, L. A.       141       Porter, John L.       66         Deal, Bruce E.       36       Puotinen, D. A.       431         Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Hanes, M. H.       87       Vizir, Vitali       302         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313       Yeh, T. H.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |         |                         |      |

| Deal, Bruce E.       36       Puotinen, D. A.       431         Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313       Yeh, T. H.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |         |                         |      |

| Donovan, R. P.       123       Roddan, Allison       302         Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Hanes, M. H.       87       Vizir, Vitali       302         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313       Yeh, T. H.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |         |                         |      |

| Dumin, D. J.       79       Schumann, P. A., Jr.       234         Evans, R. A.       123       Severin, P. J.       224         Faust, J. W., Jr.       436       Simpson, J.       87         Gibbon, C. F.       21       Soper, R. B.       412         Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Hanes, M. H.       87       Vizir, Vitali       302         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313       Yeh, T. H.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |         | · ·                     |      |

| Evans, R. A.  123  Severin, P. J.  224  Faust, J. W., Jr.  436  Simpson, J.  87  Gibbon, C. F.  21  Soper, R. B.  412  Gibbons, J. F.  141  Stover, H. L.  273  Gordon, B. J.  Greig, W.  168  Tucker, R. N.  223  Gupta, D. C.  66, 285  Van Gelder, W.  256  Hammond, M. L.  51  Vieweg-Gutberlet, F. G.  409  Hanes, M. H.  87  Vizir, Vitali  302  Harp, R. S.  485  Herman, David S.  365  White, Marvin H.  365  Howard, J. K.  111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Donovan, R. P.    |         | Roddan, Allison         |      |

| Faust, J. W., Jr. 436 Simpson, J. 87 Gibbon, C. F. 21 Soper, R. B. 412 Gibbons, J. F. 141 Stover, H. L. 273 Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Gupta, D. C. 66, 285 Van Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hanes, M. H. 87 Vizir, Vitali 302 Harp, R. S. 273 Wang, P. 285 Herman, David S. 365 White, Marvin H. 365 Howard, J. K. 313 Yeh, T. H. 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Dumin, D. J.      | 79      | Schumann, P. A., Jr.    | 234  |

| Gibbon, C. F. 21 Soper, R. B. 412 Gibbons, J. F. 141 Stover, H. L. 273 Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Gupta, D. C. 66, 285 Van Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hanes, M. H. 87 Vizir, Vitali 302 Harp, R. S. 273 Wang, P. 285 Herman, David S. 365 White, Marvin H. 365 Howard, J. K. 313 Yeh, T. H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Evans, R. A.      | 123     | Severin, P. J.          | 224  |

| Gibbons, J. F.       141       Stover, H. L.       273         Gordon, B. J.       273       Thomas, D. G.       3         Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Hanes, M. H.       87       Vizir, Vitali       302         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313       Yeh, T. H.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Faust, J. W., Jr. | 436     | Simpson, J.             | 87   |

| Gordon, B. J. 273 Thomas, D. G. 3 Greig, W. 168 Tucker, R. N. 223 Gupta, D. C. 66, 285 Van Gelder, W. 256 Hammond, M. L. 51 Vieweg-Gutberlet, F. G. 409 Hanes, M. H. 87 Vizir, Vitali 302 Harp, R. S. 273 Wang, P. 285 Herman, David S. 365 White, Marvin H. 365 Howard, J. K. 313 Yeh, T. H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Gibbon, C. F.     | 21      | Soper, R. B.            | 412  |

| Greig, W.       168       Tucker, R. N.       223         Gupta, D. C.       66, 285       Van Gelder, W.       256         Hammond, M. L.       51       Vieweg-Gutberlet, F. G.       409         Hanes, M. H.       87       Vizir, Vitali       302         Harp, R. S.       273       Wang, P.       285         Herman, David S.       365       White, Marvin H.       365         Howard, J. K.       313       Yeh, T. H.       111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Gibbons, J. F.    | 141     | Stover, H. L.           | 273  |