# NBS SPECIAL PUBLICATION 400-66

U.S. DEPARTMENT OF COMMERCE / National Bureau of Standards

NBS PUBLICATIONS

## Semiconductor Measurement Technology:

The Design, Testing, and Analysis of a Comprehensive Test Pattern for Measuring CMOS/SOS Process Performance and Control

QC: 100 .U57 No.400-66 1981 c. 2 0 \* 9 2 5 \*

#### NATIONAL BUREAU OF STANDARDS

The National Bureau of Standards' was established by an act of Congress on March 3, 1901. The Bureau's overall goal is to strengthen and advance the Nation's science and technology and facilitate their effective application for public benefit. To this end, the Bureau conducts research and provides: (1) a basis for the Nation's physical measurement system, (2) scientific and technological services for industry and government, (3) a technical basis for equity in trade, and (4) technical services to promote public safety. The Bureau's technical work is performed by the National Measurement Laboratory, the National Engineering Laboratory, and the Institute for Computer Sciences and Technology.

THE NATIONAL MEASUREMENT LABORATORY provides the national system of physical and chemical and materials measurement; coordinates the system with measurement systems of other nations and furnishes essential services leading to accurate and uniform physical and chemical measurement throughout the Nation's scientific community, industry, and commerce; conducts materials research leading to improved methods of measurement, standards, and data on the properties of materials needed by industry, commerce, educational institutions, and Government; provides advisory and research services to other Government agencies; develops, produces, and distributes Standard Reference Materials; and provides calibration services. The Laboratory consists of the following centers:

Absolute Physical Quantities<sup>2</sup> — Radiation Research — Thermodynamics and Molecular Science — Analytical Chemistry — Materials Science.

THE NATIONAL ENGINEERING LABORATORY provides technology and technical services to the public and private sectors to address national needs and to solve national problems; conducts research in engineering and applied science in support of these efforts; builds and maintains competence in the necessary disciplines required to carry out this research and technical service; develops engineering data and measurement capabilities; provides engineering measurement traceability services; develops test methods and proposes engineering standards and code changes; develops and proposes new engineering practices; and develops and improves mechanisms to transfer results of its research to the ultimate user. The Laboratory consists of the following centers:

Applied Mathematics — Electronics and Electrical Engineering<sup>2</sup> — Mechanical Engineering and Process Technology<sup>2</sup> — Building Technology — Fire Research — Consumer Product Technology — Field Methods.

**THE INSTITUTE FOR COMPUTER SCIENCES AND TECHNOLOGY** conducts research and provides scientific and technical services to aid Federal agencies in the selection, acquisition, application, and use of computer technology to improve effectiveness and economy in Government operations in accordance with Public Law 89-306 (40 U.S.C. 759), relevant Executive Orders, and other directives; carries out this mission by managing the Federal Information Processing Standards Program, developing Federal ADP standards guidelines, and managing Federal participation in ADP voluntary standardization activities; provides scientific and technological advisory services and assistance to Federal agencies; and provides the technical foundation for computer-related policies of the Federal Government. The Institute consists of the following centers:

Programming Science and Technology - Computer Systems Engineering.

<sup>1</sup>Headquarters and Laboratories at Gaithersburg, MD, unless otherwise noted; mailing address Washington, DC 20234. <sup>2</sup>Some divisions within the center are located at Boulder, CO 80303. Semiconductor Measurement Technology:

OF STANDARDS LIBRARY

AUG 2 0 1981

## The Design, Testing, and Analysis of a Comprehensive Test Pattern for Measuring CMOS/SOS Process Performance and Control

Loren W. Linholm

Electron Devices Division Center for Electronics and Electrical Engineering National Engineering Laboratory National Bureau of Standards Washington, DC 20234

Sponsored by: U.S. Air Force Air Force Wright Aeronautical Laboratories Wright Patterson AFB, OH 45433 and Defense Nuclear Agency Washington, DC 20305

U.S. DEPARTMENT OF COMMERCE, Malcolm Baldrige, Secretary NATIONAL BUREAU OF STANDARDS, Ernest Ambler, Director

Issued August 1981

### Library of Congress Catalog Card Number: 81-600078

National Bureau of Standards Special Publication 400-66 Nat. Bur. Stand. (U.S.), Spec. Publ. 400-66, 148 pages (Aug. 1981) CODEN: XNBSAV

#### U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1981

For sale by the Superintendent of Documents, U.S. Government Printing Office, Washington, D.C. 20402 Price \$5.50

(Add 25 percent for other than U.S. mailing)

#### Page

| Abst | tract . | • •                                        | ••                                                  | •••                          | •••                          | •                                          | •                                    | •                           | •                                     | • •                                  | •                    | •                          | •                  | •                             | •                    | •                        | •              | •                | •  | •   | ٠   | ٠ | • | ٠                | •                | •                | ٠                | •                | 1                                                  |

|------|---------|--------------------------------------------|-----------------------------------------------------|------------------------------|------------------------------|--------------------------------------------|--------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|----------------------|----------------------------|--------------------|-------------------------------|----------------------|--------------------------|----------------|------------------|----|-----|-----|---|---|------------------|------------------|------------------|------------------|------------------|----------------------------------------------------|

| 1.   | Introd  | luct:                                      | ion                                                 | ••                           | •••                          | •                                          | •                                    | •                           | •                                     | •                                    | •                    | •                          | •                  | •                             | •                    | •                        | •              | •                | •  | •   | •   | ٠ | • | •                | •                | •                | •                | •                | 1                                                  |

| 2.   | Approa  | ach                                        | • •                                                 | ••                           | ••                           | •                                          | •                                    | •                           | •                                     | •                                    | •                    | •                          | •                  | •                             | •                    | •                        | •              | •                | •  | •   | •   | • | • | •                | •                | •                | •                | •                | 2                                                  |

| 3.   |         | rest                                       | Pat                                                 | Desc<br>tern<br>tern         | NB                           | s-1                                        | 6                                    | •                           | •                                     | •                                    | •                    | •                          | •                  | •                             | •                    | •                        | •              | •                | •  | •   | •   | • | • | •                | •                | •                | •                | •                | 2<br>2<br>7                                        |

| 4.   |         | leasu                                      | ırem                                                | asur<br>nent<br>.cal         | Sys                          | ten                                        | n D                                  | es                          | cr:                                   | ipt                                  | tī                   | on                         |                    | •                             | •                    | •                        | •              | •                | •  | •   | •   | • | • | •                | •                | •                | •                | •                | 7<br>7<br>10                                       |

| 5.   | 5.1.1   | Proce<br>Lot<br>Int<br>Lot<br>Rando<br>Ran | ess<br>t-to<br>traw<br>t-to<br>tral<br>om F<br>ndom | Para<br>-Lot<br>afer<br>-Lot | Co<br>Co<br>p-<br>Para<br>Te | er<br>nta<br>nta<br>Cha<br>met<br>st<br>Fa | Pa<br>act<br>act<br>inn<br>cer<br>St | tto<br>Re<br>el<br>Va<br>ru | eri<br>es:<br>Tl<br>ar:<br>ctu<br>Sti | n<br>ist<br>ist<br>hre<br>iat<br>ure | ta<br>ta<br>es<br>ti | nc<br>nc<br>ho<br>on<br>Ev | •<br>e<br>ld<br>al | •<br>Va<br>V<br>•<br>ua<br>(R | ri<br>ri<br>ol<br>ti | •<br>at<br>ta<br>•<br>on | io<br>io<br>ge | •<br>n<br>•<br>• | ar | :ia |     |   | • | •<br>•<br>•<br>• | •<br>•<br>•<br>• | •<br>•<br>•<br>• | •<br>•<br>•<br>• | •<br>•<br>•<br>• | 11<br>11<br>13<br>13<br>16<br>21<br>23<br>24<br>34 |

| 6.   |         | Proce                                      | ess                                                 | Para<br>'ault                | met                          | er                                         | Pa                                   | tt                          | erı                                   | n -                                  | •                    | •                          | •                  | •                             | •                    | •                        | •              | •                | •  | •   | •   | • | • | •                | •                | •                | •                | •                | 38<br>38<br>40                                     |

| Ackı | nowledg | gment                                      | t•                                                  | •••                          | •••                          | •                                          | •                                    | •                           | •                                     | •                                    | •                    | •                          | •                  | •                             | •                    | •                        | •              | •                | •  | •   | •   | • | • | •                | •                | •                | •                | •                | 41                                                 |

| Refe | erences | 5 •                                        | •••                                                 | •••                          | •••                          | •                                          | •                                    | •                           | •                                     | •                                    | •                    | •                          | •                  | •                             | •                    | •                        | •              | •                | •  | •   | •   | • | • | •                | •                | •                | •                | •                | 41                                                 |

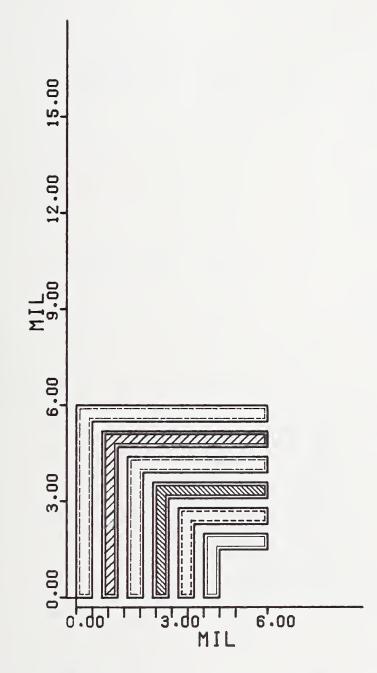

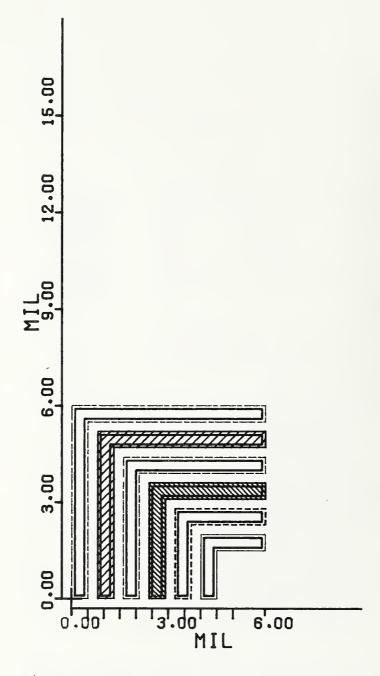

| Арре | endix A | A - 1                                      | NBS-                                                | 16 a                         | ind                          | NBS                                        | 5-2                                  | 6 '                         | Γoj                                   | ро                                   | 10                   | gi                         | ca                 | 1                             | De                   | si                       | .gn            | R                | ul | .es | ;   | • | • | •                | •                | •                | •                | •                | 42                                                 |

| Appe | endix H | 3 – 1                                      | NBS-                                                | • <b>1</b> 6 a               | ind                          | NBS                                        | 5-2                                  | 6 '                         | Te                                    | st                                   | S                    | tr                         | uc                 | tu                            | re                   | D                        | )es            | cr               | iŗ | oti | .or | ı | • | •                | •                | •                | •                | •                | 58                                                 |

| Appe | endix ( |                                            |                                                     | atic<br>16 F                 |                              |                                            |                                      |                             |                                       |                                      |                      |                            |                    |                               |                      |                          |                |                  |    |     |     |   |   |                  |                  |                  | •                | •                | 93                                                 |

| Appe | endix I |                                            |                                                     | ical<br>dati                 |                              |                                            |                                      |                             |                                       |                                      |                      |                            |                    |                               |                      |                          |                |                  |    |     |     |   |   |                  |                  |                  |                  | •                | 112                                                |

#### List of Figures

Page

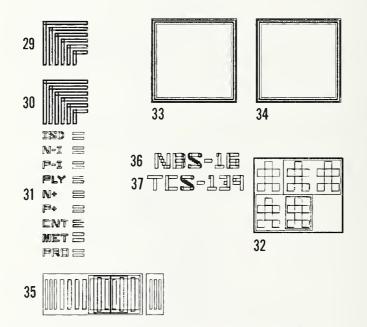

| 1.  | Test pattern NBS-16 functional layout                                                                                                                                  | 3  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

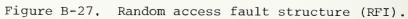

| 2.  | Computer-generated plot of test pattern NBS-16                                                                                                                         | 5  |

| 3.  | Computer-generated plot of test pattern NBS-26                                                                                                                         | 8  |

| 4.  | Block diagram of computer-controlled electrical test system                                                                                                            | 9  |

| 5.  | Typical computer-generated gray-scale wafer map showing test site location and intrawafer parameter variation                                                          | 12 |

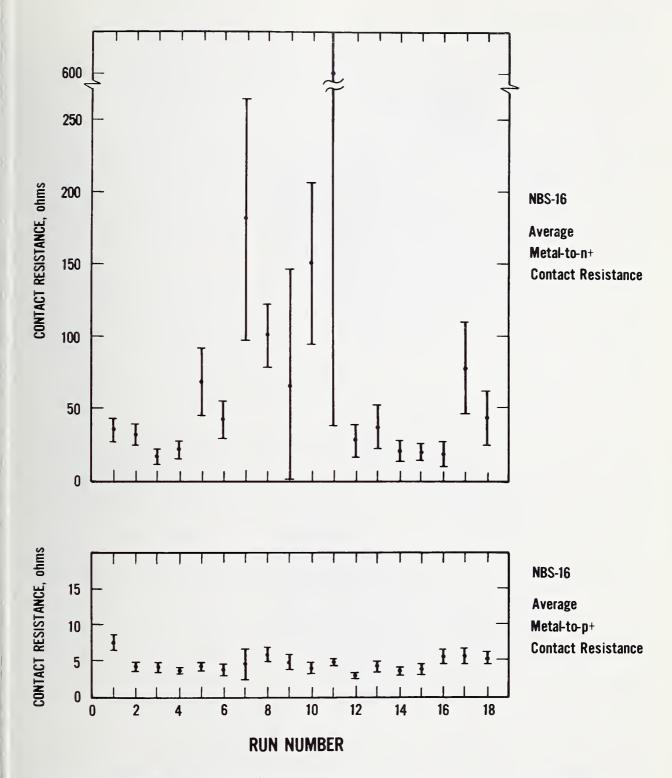

| 6.  | Average metal-to- $n^+$ contact resistance, $\Omega$ , versus lot number and average metal-to- $p^+$ contact resistance, $\Omega$ , versus lot number .                | 15 |

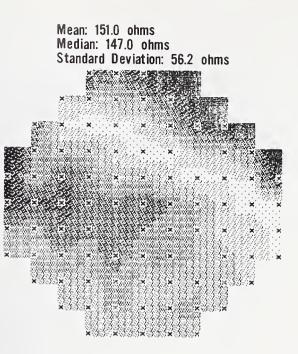

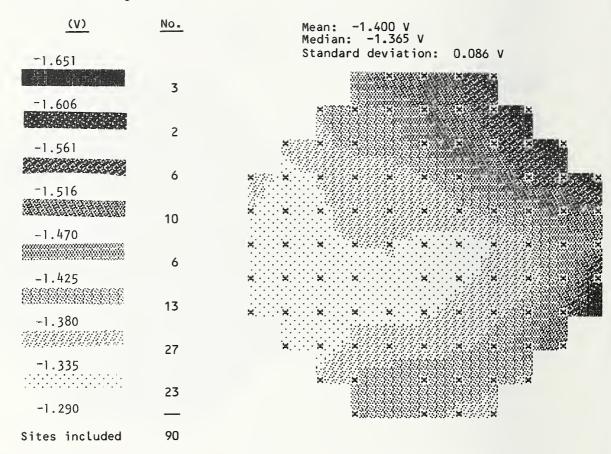

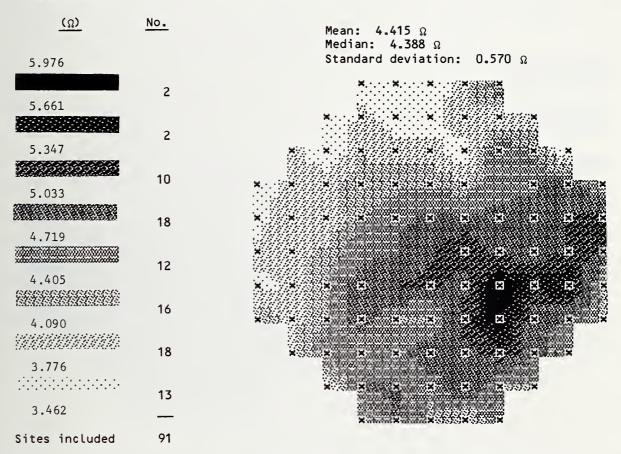

| 7.  | Wafer maps of metal-to- $n^+$ contact resistance at 87 test sites and $n^+$ sheet resistance at 90 test sites for NBS-16 PVW A10                                       | 17 |

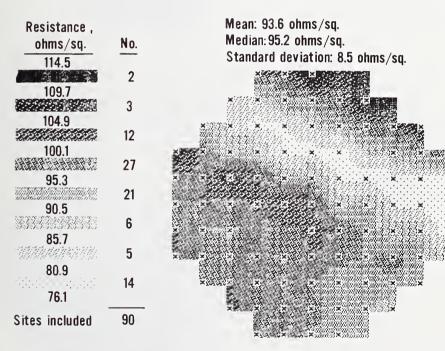

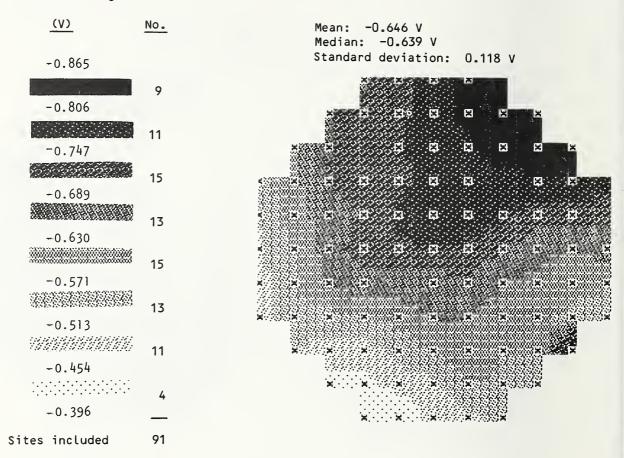

| 8.  | Wafer maps of metal-to- $n^+$ contact resistance at 91 test sites and $n^+$ sheet resistance at 95 test sites for NBS-16 PVW A9                                        | 18 |

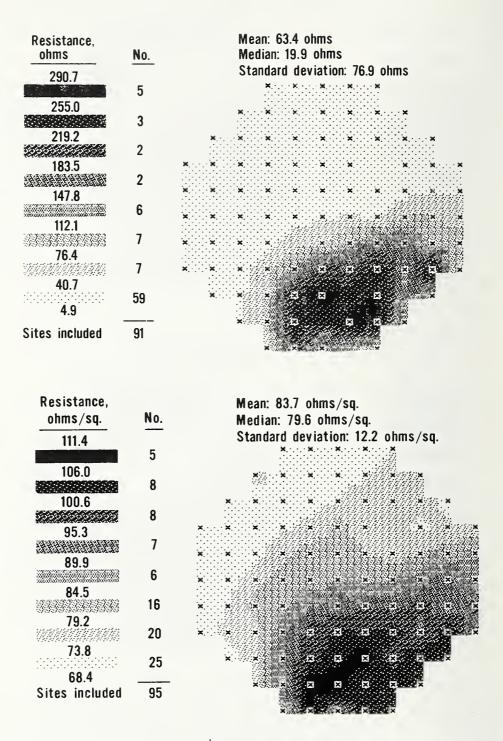

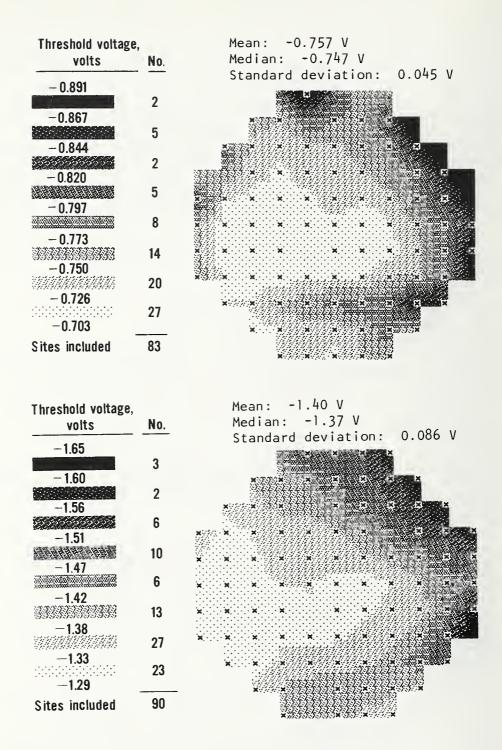

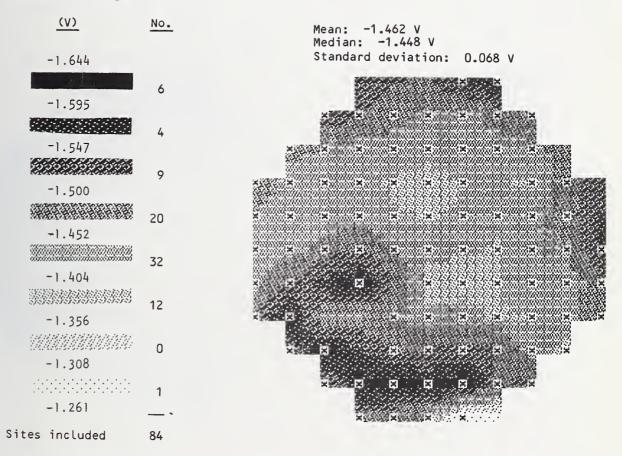

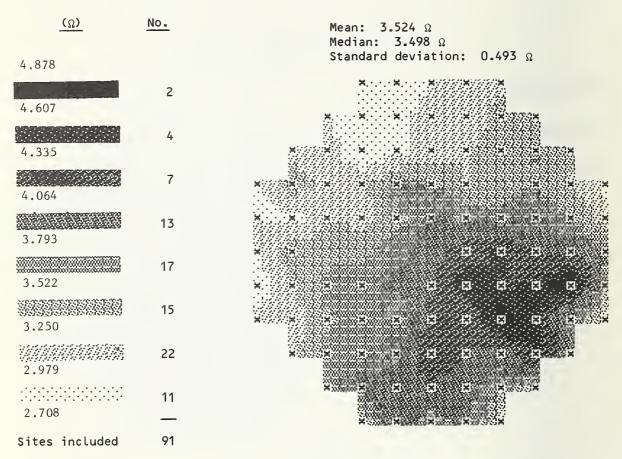

| 9.  | Wafer maps of $p$ -channel threshold voltage at 83 test sites for PVW A16 and PVW A11                                                                                  | 20 |

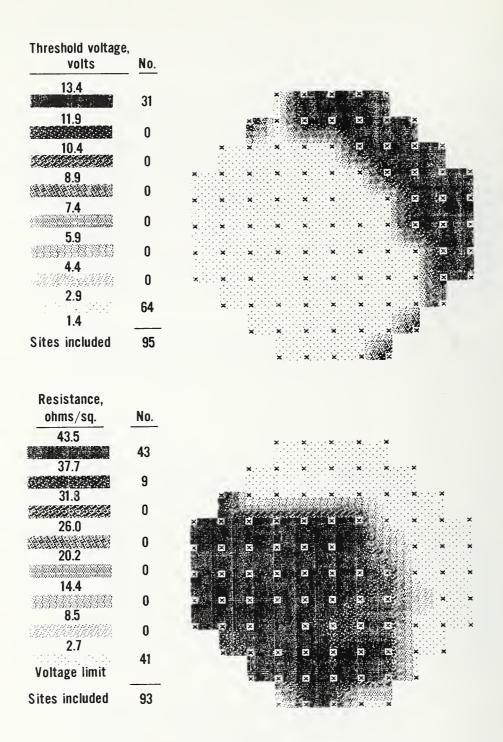

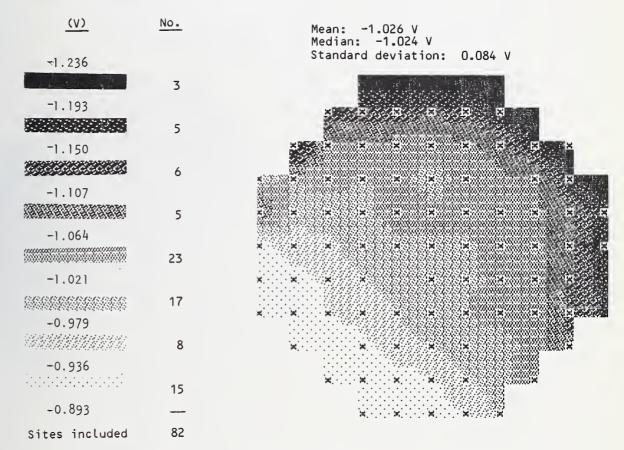

| 10. | Wafer maps showing location of nonfunctional $n$ -channel MOSFETs and $n^+$ sheet resistor test structures for NBS-26 PVW B4                                           | 22 |

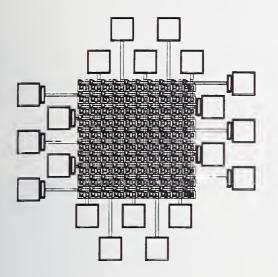

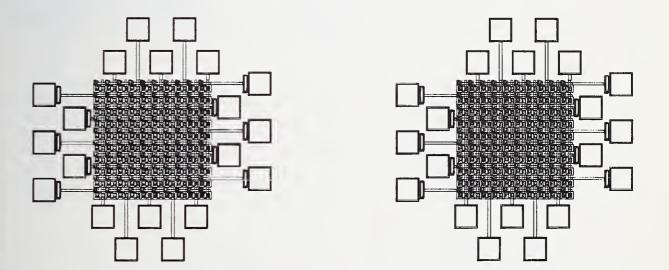

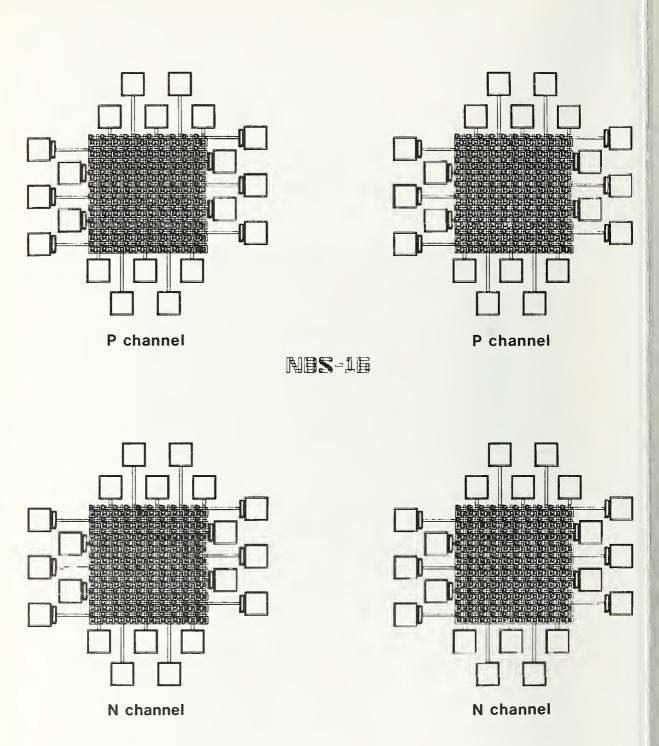

| 11. | Random access fault structure, RFI, contained on one NBS-16/26<br>test pattern                                                                                         | 25 |

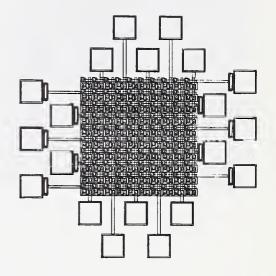

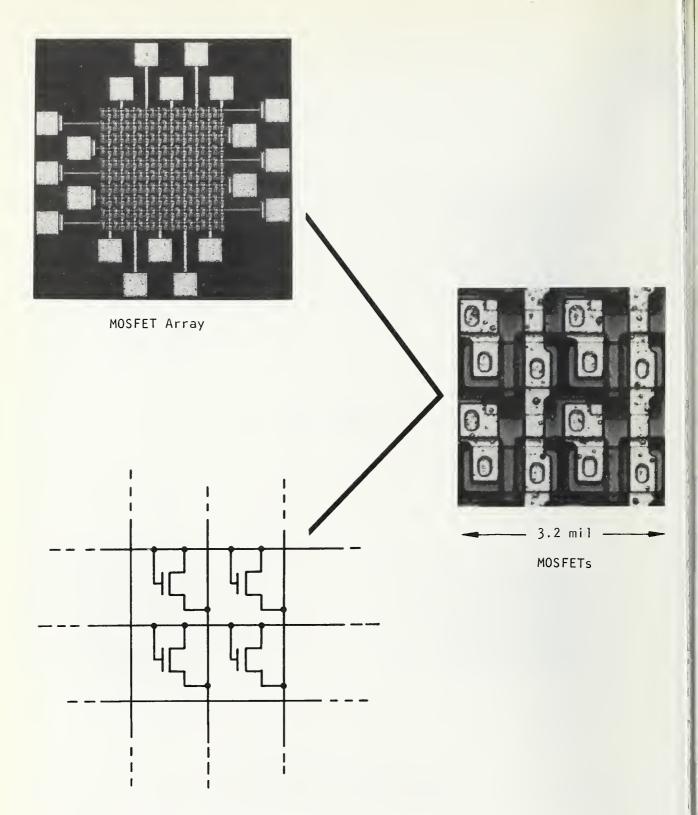

| 12. | One random access fault structure RFI, showing a micrograph of a two-by-two section of MOSFETs and a schematic of the electrical interconnect                          | 26 |

|     |                                                                                                                                                                        |    |

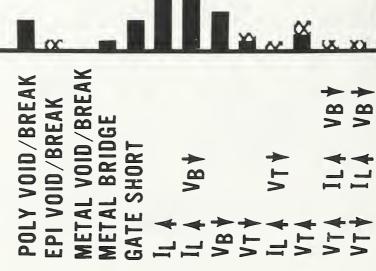

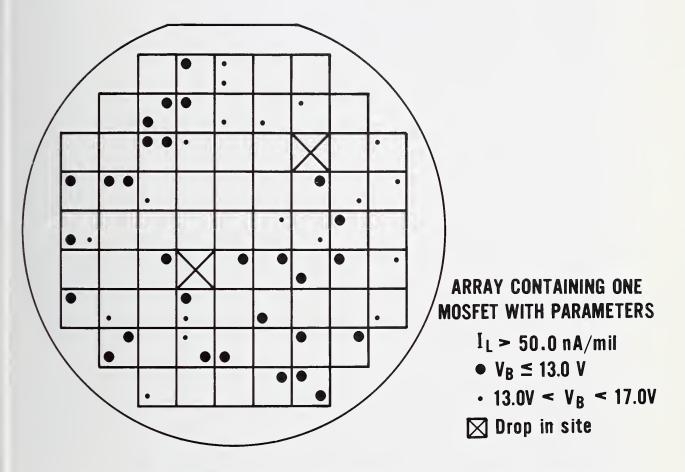

| 13. | Test results for one RFI array from NBS-16 PVW A1                                                                                                                      | 28 |

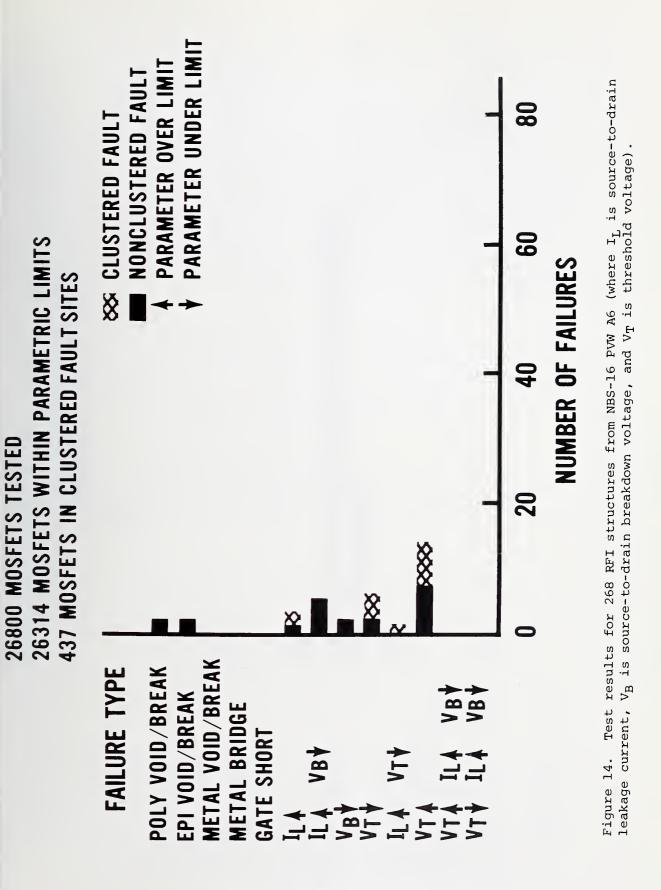

| 14. | Test results for 268 RFI structures from NBS-16 PVW A6                                                                                                                 | 29 |

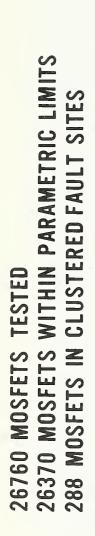

| 15. | Test results for 268 RFI structures from NBS-16 PVW A1                                                                                                                 | 30 |

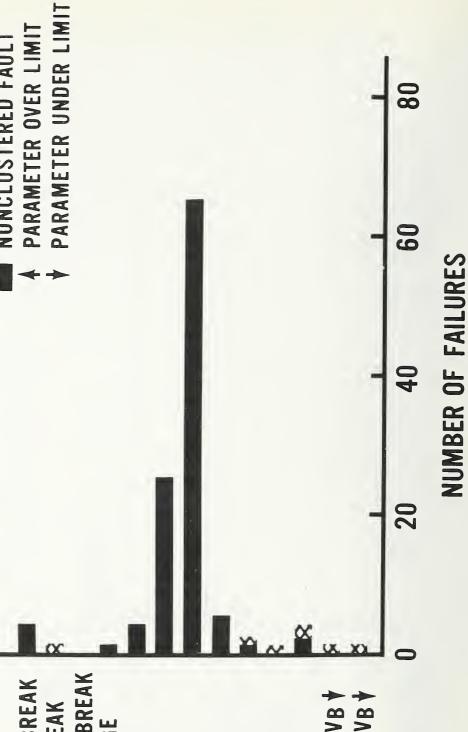

| 16. | Histogram of breakdown voltage, V <sub>B</sub> , volts, with devices with<br>a source-to-drain leakage current greater than 50 nA/mil gate<br>length for NBS-16 PVW A1 | 32 |

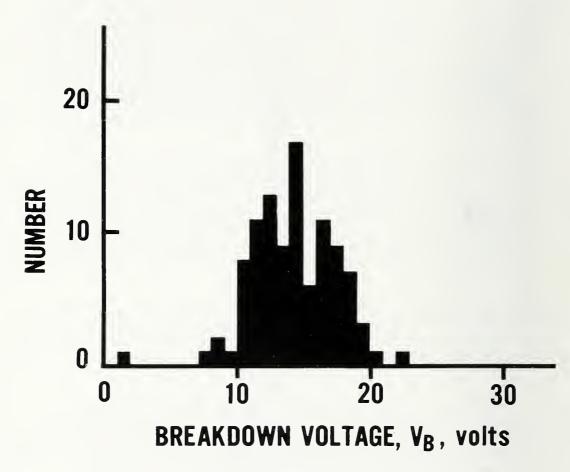

| 17. | Failure map showing approximate location of RFI structures containing MOSFETs with high source-to-drain current leakage                                                | 33 |

List of Figures (continued)

|     |                                                                                                                                               | Page |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| 18. | Gate dielectric integrity array, RFII                                                                                                         | 35   |  |  |  |  |

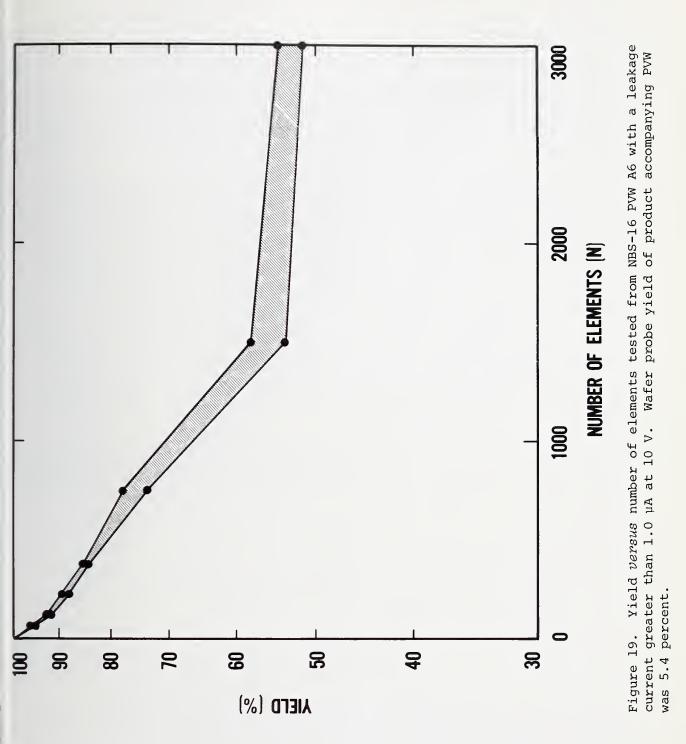

| 19. | Yield <i>versus</i> number of elements tested from NBS-16 PVW A6 with a leakage current greater than 1.0 $\mu$ A at 10 V                      | 37   |  |  |  |  |

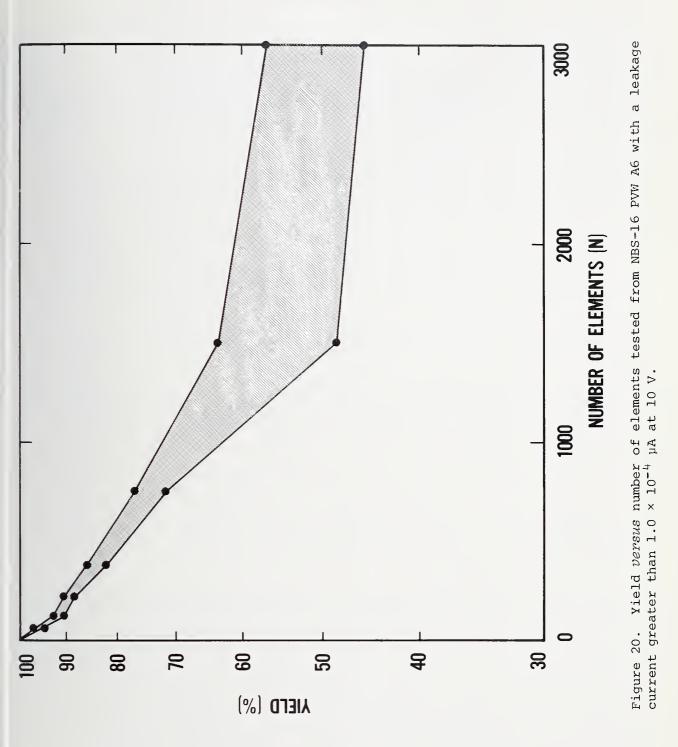

| 20. | . Yield versus number of elements tested from NBS-16 PVW A6 with a leakage current greater than 1.0 $\times$ 10 <sup>-4</sup> $\mu A$ at 10 V |      |  |  |  |  |

|     | List of Tables                                                                                                                                |      |  |  |  |  |

| 1.  | Device Types on NBS-16                                                                                                                        | 4    |  |  |  |  |

| 2.  | Photomask Levels                                                                                                                              | 6    |  |  |  |  |

| 3.  | List of Structures Evaluated on Process Parameter Patterns                                                                                    | 14   |  |  |  |  |

Semiconductor Measurement Technology: The Design, Testing, and Analysis of a Comprehensive Test Pattern for Measuring CMOS/SOS Process Performance and Control

by

Loren W. Linholm Electron Devices Division National Bureau of Standards Washington, DC 20234

A Process Validation Wafer (PVW) is a wafer containing only test patterns. One PVW accompanies a product lot during the fabrication process. Test patterns NBS-16 and NBS-26 are designed to be used on PVWs. They contain both process parameter test structures and random fault test structures. Eighteen NBS-16 PVWs were fabricated in a radiation-hardened silicon-gate CMOS/SOS process. These PVWs were tested on a high-speed computer-controlled dc test system. Test results from the process parameter test structures were used to establish the baseline electrical parameters for each product lot and to produce an eight-level gray-scale wafer map for these parameters. Based on correlations of selected wafer maps, it was possible to identify specific yield-related process problems otherwise unknown to the manufacturer or user.

Test results from two random fault test structures were used to establish a statistically significant data base for identifying and evaluating major yield-limiting fault mechanisms in the process. Test results from a developmental random access fault structure and a gate dielectric integrity array are presented. The results are analyzed for selected PVWs and a major yield-limiting fault mechanism detected. A description of the test pattern and test results, including a drawing of each test structure, recommended test procedure, and design rules, are found in the appendices.

*Key words:* integrated circuits; microelectronics; process validation wafer; random faults; silicon-on-sapphire; test pattern; test structure; yield.

#### 1. INTRODUCTION

With the increasing complexity of integrated circuits, it is becoming more difficult for both the manufacturer and user to fully characterize circuit performance. Functional testing alone is an impractical approach for evaluating complex circuits. As a result, greater emphasis is being placed on results from microelectronic test structures which provide clear and unambiguous test results [1].

The objective of the work covered in this report was to develop process assessment methods which use microelectronic test structures and which can be used by an independent organization to evaluate the electrical characteristics and yield potential of the integrated circuits being manufactured.

1

#### 2. APPROACH

The approach used in meeting the objective of this program was to design, test, and evaluate a test pattern consisting of many well-defined and wellcharacterized test structures together with several developmental test structures. Test pattern NBS-16 was implemented as a process validation wafer (PVW) [2,3], a wafer consisting only of identical test patterns. One PVW was processed as part of each production run at RCA in a developmental program being conducted under Air Force Wright Aeronautical Laboratories (AFWAL) contract. The PVW was subsequently tested and evaluated at NBS. Midway through the program, a modified test pattern, NBS-26, was designed based on the information and experience gained from testing NBS-16.

The test pattern was designed in a collaborative effort by NBS and the Jet Propulsion Laboratory (JPL). Three areas on the test pattern contain structures designed by JPL. These structures were merged with four areas containing NBS-designed structures. Final pattern layout was performed by NBS. Testing and analysis of the structures was to be performed by the respective laboratories. Only the test results and analysis of the NBS structures are included in this report.

An automatic computer-controlled integrated circuit tester and wafer prober were used to determine the dc electrical parameters of selected test structures. Each test pattern on a wafer was probed and electrical results recorded on a line printer and floppy disc. Statistical analysis and wafer mapping of selected electrical parameters which formed a statistically significant data base were used to evaluate the process.

3. TEST PATTERN DESCRIPTION

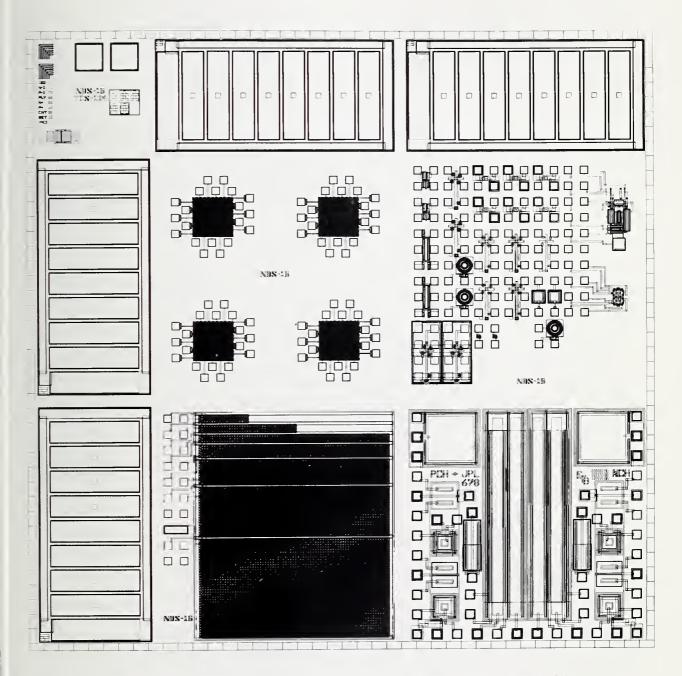

3.1 Test Pattern NBS-16

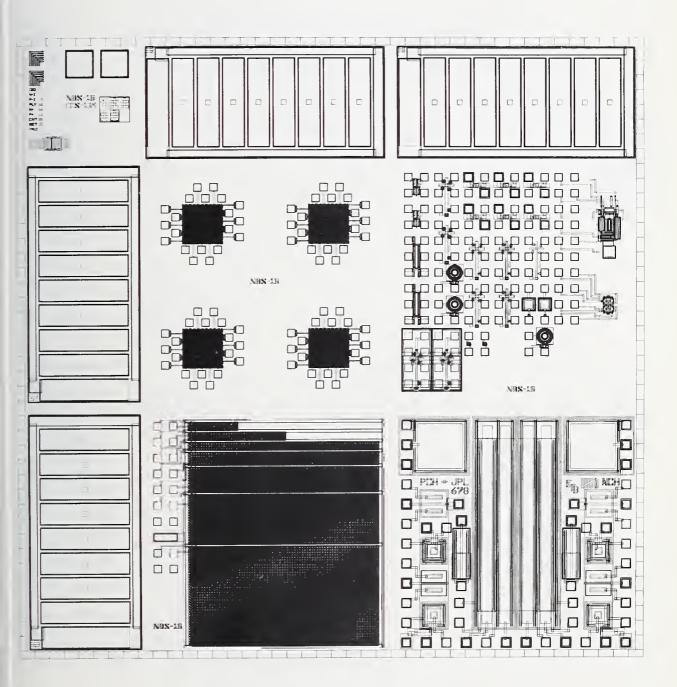

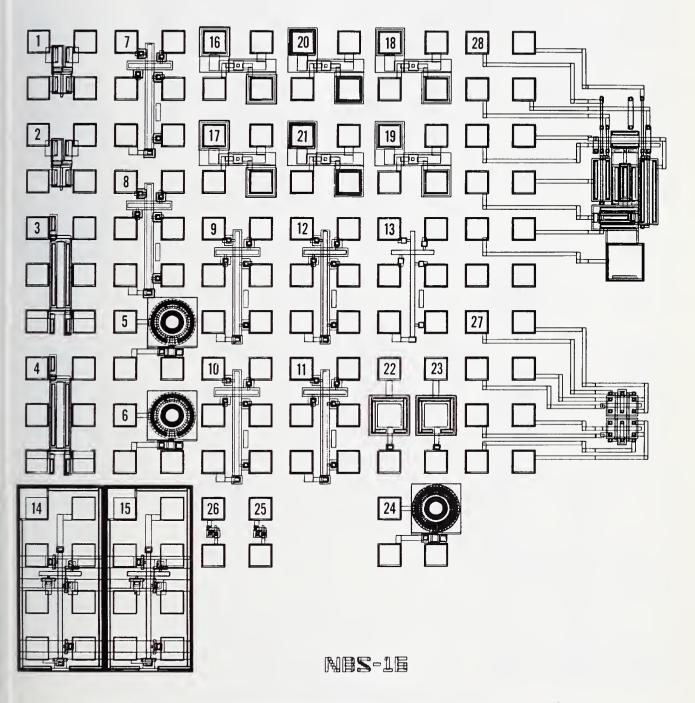

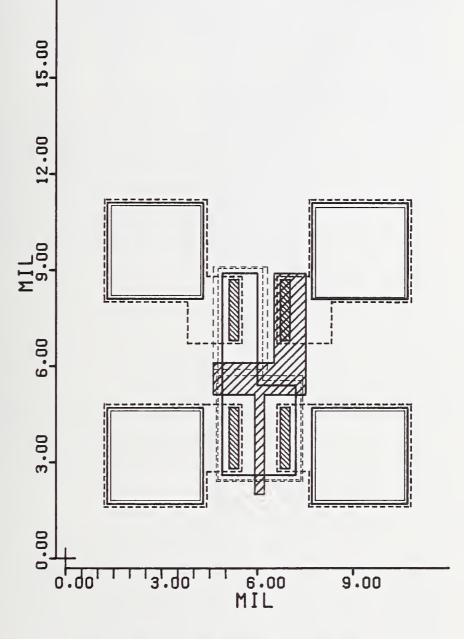

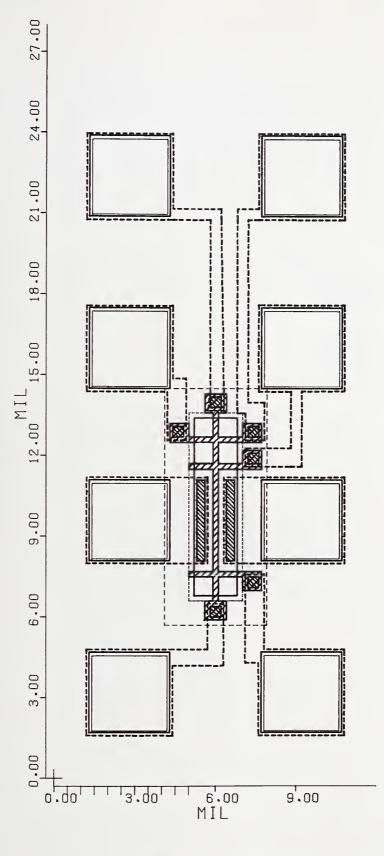

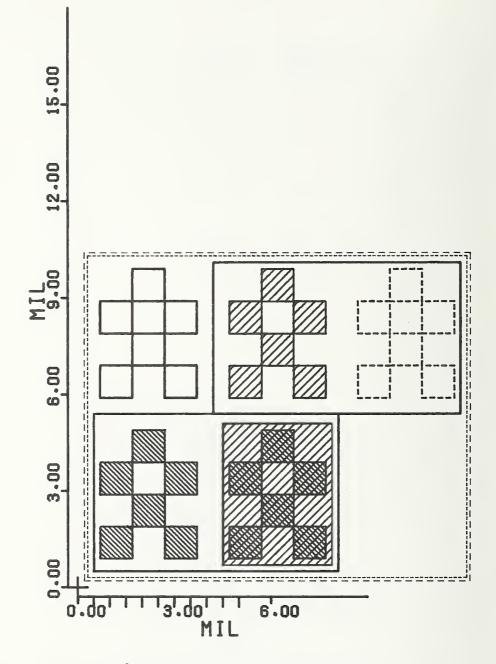

NBS-16 is a square test pattern 250 mil (6.35 mm) on a side. It is divided into seven basic areas as shown in figure 1. Each area can be physically separated, if desired. The functions of each individual area are listed in table 1. A computer-generated plot of NBS-16 is shown in figure 2.

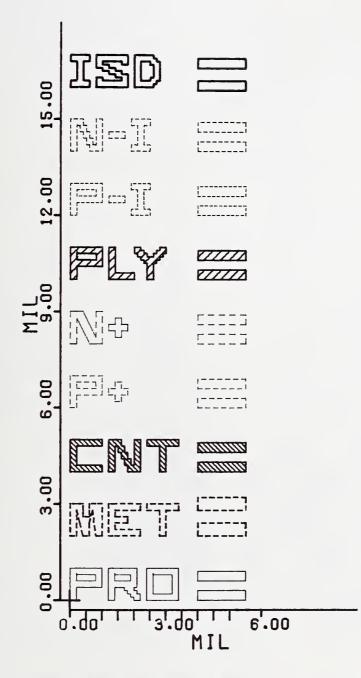

NBS-16 was fabricated in a radiation-hardened, silicon gate CMOS/SOS process. RCA uses a seven-level mask set for their radiation-hardened process. The process [4] has nine photolithography steps\* (two masks are used twice). In the standard RCA process, the N-I mask is used for the  $n^-$  and  $p^+$  implants and the P-I mask used for the  $p^-$  and  $n^+$  implants. A list of the topological design rules and tolerances employed in designing the test pattern can be found in Appendix A. In this appendix as in this report, the terms polysilicon and poly are used interchangeably as are episilicon, epi, epi island, and island.

For optimum flexibility, the test pattern mask set contains nine levels as listed in table 2. This allows for  $n^+$  into  $n^-$  and  $p^+$  into  $p^-$  implants. It does not require any additional lithography processing and is fully

<sup>\*</sup>During the program, the *n*<sup>-</sup> photolithography step and accompanying *n*<sup>-</sup> implant were dropped, reducing the number of steps to eight.

| II.<br>Physical<br>Analysis<br>Pattern<br>(NBS)                | VI.<br>Oxide Breakdown Pat<br>(JPL)                         | ttern, p <sup>-</sup> Substrate             |

|----------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------|

| Breakdown Pattern,<br>strate (JPL)                             | III.<br>Random Access<br>Fault Structure,<br>RFI<br>(NBS)   | I.<br>Process Parameter<br>Pattern<br>(NBS) |

| VII.<br>VII.<br>Oxide Breakdown<br>n <sup>-</sup> Substrate (J | IV.<br>Gate Dielectric<br>Integrity Array,<br>RFII<br>(NBS) | V.<br>Process Parameter<br>Pattern<br>(JPL) |

Figure 1. Test pattern NBS-16 functional layout.

|      | Area                                              | Types of Devices                                                                                                |

|------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1.   | Process Parameter<br>Pattern (NBS)                | MOSFETs, cross-bridge sheet<br>resistors, contact resis-<br>tors, capacitors, RCA Gate<br>Universal Array Cells |

| II.  | Physical Analysis<br>Pattern (NBS)                | Level designators, alignment<br>marks, ion beam areas, sur-<br>face profilometer, etch<br>structure             |

| III. | Random Access Fault<br>Structure, RFI (NBS)       | p- and $n-$ channel MOSFETs                                                                                     |

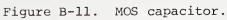

| IV.  | Gate Dielectric<br>Integrity Array, RFII<br>(NBS) | Capacitors                                                                                                      |

| ۷.   | Process Parameter<br>Pattern (JPL)                | MOSFETs, capacitors, resis-<br>tors                                                                             |

| VI.  | Oxide Breakdown<br>Pattern (JPL)                  | Capacitor array, $p^-$ substrate                                                                                |

| VII. | Oxide Breakdown<br>Pattern (JPL)                  | Capacitor array, $n^-$ substrate                                                                                |

Table 1. Device Types on NBS-16.

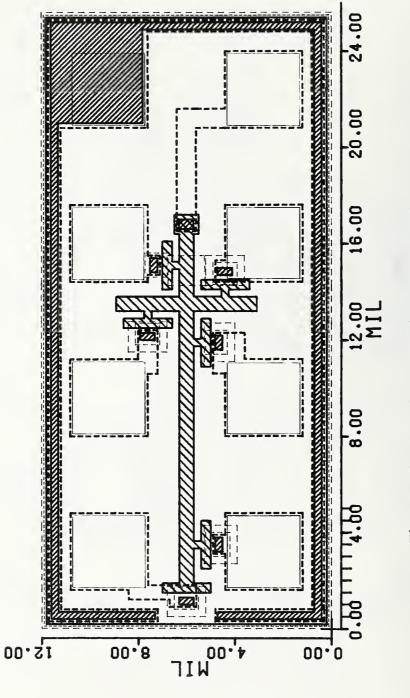

Figure 2. Computer-generated plot of test pattern NBS-16.

| Process<br>Step | Function                      | Mask<br>Designato: |

|-----------------|-------------------------------|--------------------|

| 1.              | Island Definition             | ISD                |

| 2.              | <i>n</i> <sup>-</sup> Implant | N-I                |

| 3.              | $p^-$ Implant                 | P-I                |

| 4.              | Poly Definition               | PLY                |

| 5.              | n <sup>+</sup> Implant        | N <sup>+</sup>     |

| б.              | $p^+$ Implant                 | P+                 |

| 7.              | Contact                       | CNT                |

| 8.              | Metal Definition              | MET                |

| 9.              | Passivation                   | PRO                |

Table 2. Photomask Levels.

compatible with most commercial CMOS/SOS processes. The working photomasks were fabricated by a computer-controlled optical pattern generator at RCA.

The PVW was fabricated on 3-in. (76.2-mm) diameter silicon-on-sapphire wafers. Ninety-five of the 97 sites available on the PVW are used for NBS-16 test patterns. A detailed description of the test structures included on NBS-16, as well as the function, location, test method, and layout, is provided in Appendix B. A pattern designed by the manufacturer is located in the two remaining sites. This pattern includes a ring oscillator circuit and MOSFETs with varying gate lengths.

One PVW accompanied each product lot during fabrication. Upon completion, the wafer was tested in order to determine the value of critical electrical process parameters. These parameters were then statistically analyzed to identify correlations between selected parameters and the performance of the process lot. A total of 18 NBS-16 PVWs have been manufactured from 17 different process lots. In one instance, two PVW wafers accompanied the same product lot.

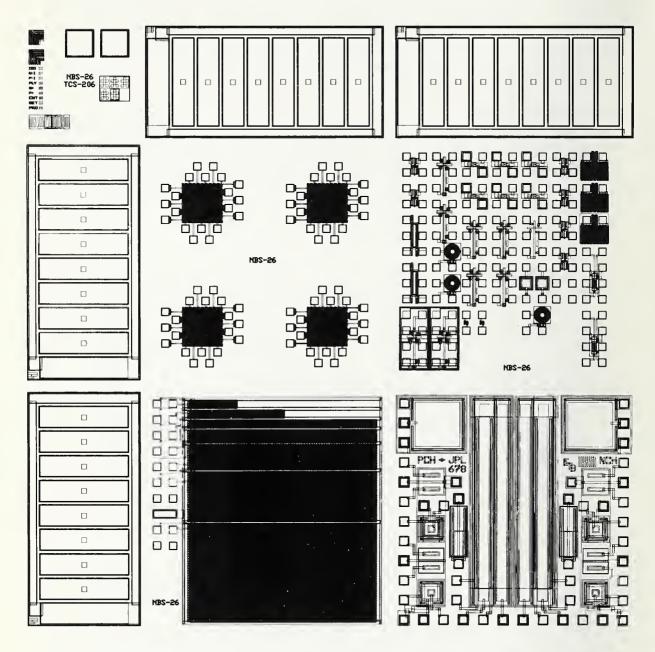

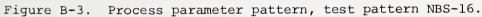

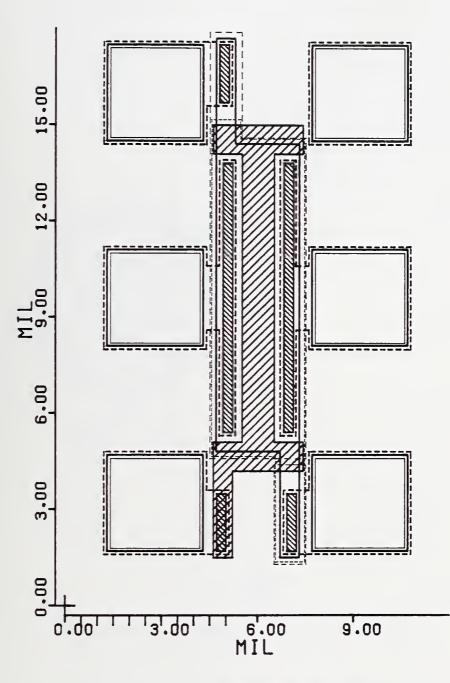

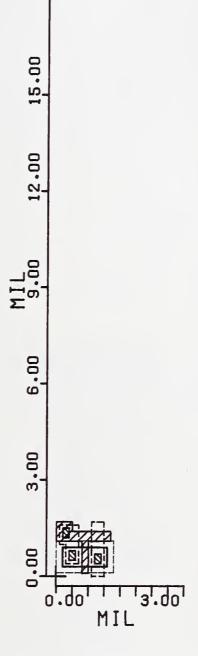

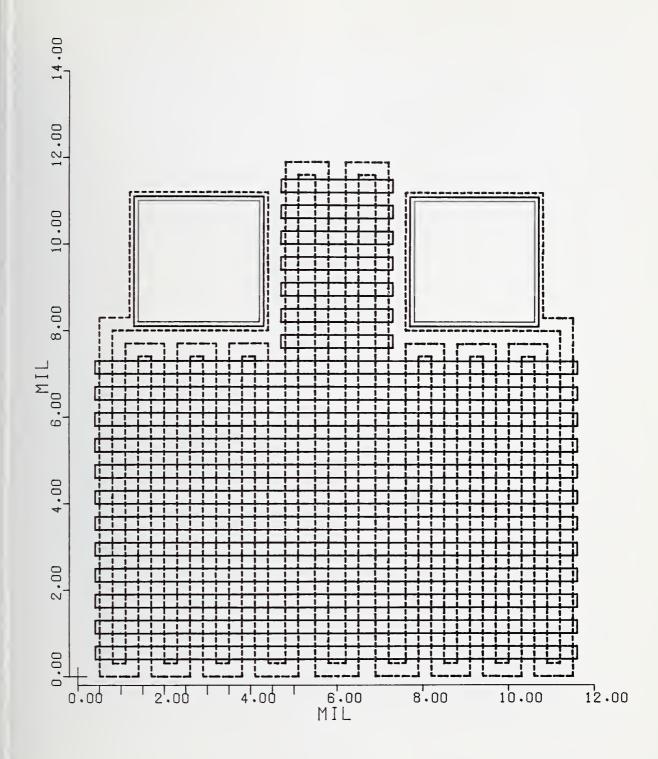

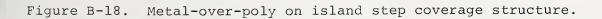

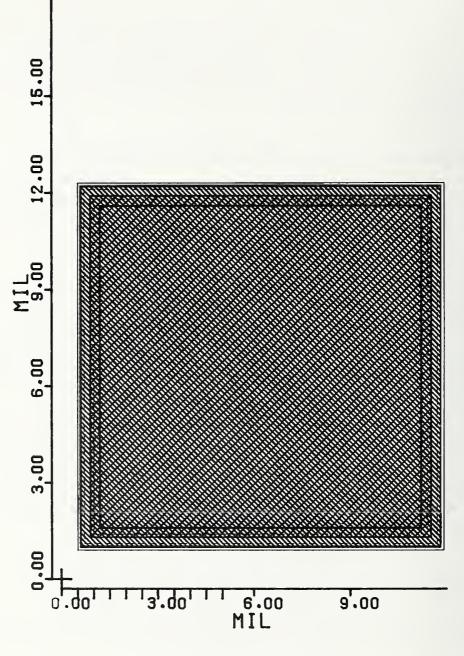

#### 3.2 Test Pattern NBS-26

NBS-26 is identical to test pattern NBS-16 except for modifications to the process parameter pattern. A computer-generated plot of NBS-26 is shown in figure 3. Two test structures (no. 27, internal cell from RCA Gate Universal Array (GUA), and no. 28, input/output cell with input protection from RCA GUA) found on NBS-16 were omitted. In their location test structures consisting of p- and n-channel MOSFETs with 0.20-mil (5.08-µm) and 0.15-mil (3.81-µm) gate lengths, metal step coverage structures, and developmental MOSFET/cross-bridge sheet resistor test structures were added. These structures are also described in Appendix B. Eleven wafers containing NBS-26 test patterns were fabricated and tested. All 11 wafers were fabricated in the same lot and were used as a check of the functionality of the photomask set. At the time of this report, no NBS-26 test patterns had been fabricated as PVWs accompanying product wafer lots.

#### 4. ELECTRICAL MEASUREMENTS AND ANALYSIS TECHNIQUES

#### 4.1 Measurement System Description

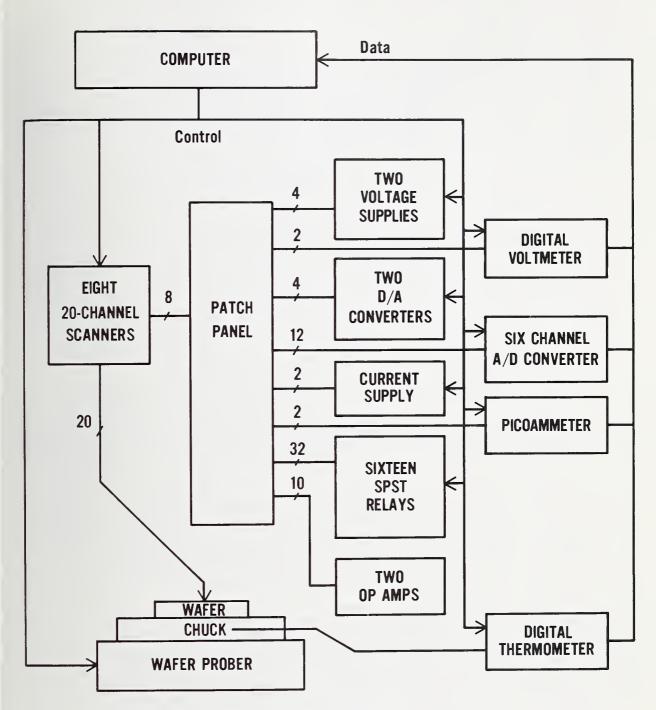

The measurement system used to test the PVWs consists of a minicomputer and associated electrical test equipment. A block diagram of the measurement system is shown in figure 4. The minicomputer is configured with 352 kilobytes of memory, two 10-megabyte disc drives, two floppy disc drives, a 9-track dual density magnetic tape drive, a system console, several CRT and hard-copy terminals, a line printer, a digital plotter, and a multiuser operating system. The test equipment consists of an automatic wafer prober which can be programmed in English or metric units; a current supply with  $1-\mu A$  resolution and compliance voltage programmable up to 100 V; two voltage supplies with  $1-\mu V$  resolution and operating modes which provide either high precision or high speed readings; a digital picoammeter with  $1-\mu A$  resolution; 16 single-pole, single-throw dry reed relays; and eight 20-channel scanners, all digitally programmable and operating under computer control.

$\overline{7}$

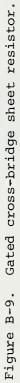

Figure 3. Computer-generated plot of test pattern NBS-26.

Figure 4. Block diagram of computer-controlled electrical test system.

The software to control these instruments consists of a set of assembly language subprograms, one to control each instrument; several assembly language subroutines for mathematical operations such as conversion from binary coded decimal to floating point format, status checking, and error handling; and a driver within the operating system. To activate an instrument, the user calls the appropriate subprogram from a FORTRAN program using a CALL statement. The instruments can also be controlled from programs written in BASIC. An interactive mode is available wherein the operator can command all instruments from a terminal. This is useful in developing and debugging software and in determining appropriate applied voltage or current levels for automated testing.

In a typical measurement, data are acquired from selected structures at each test site on a wafer, and the test results are logged to the line printer and recorded on a floppy disc. Testing time is determined by the data acquisition rate and the total number of sites tested. The data acquisition rate is generally limited by the response time of the test instrument which is usually run in a high precision or filtered mode. Typical measurement times for the digital voltmeter operating in the filtered mode are about one-half second per measurement; for the digital picoammeter, about eight seconds. When measurement precision and accuracy are not critical, the measurement time can be greatly reduced by operating instruments in an unfiltered mode.

#### 4.2 Statistical Analysis Techniques

Once data are obtained, it is important to transfer this information into a form which can be readily interpreted by the user or manufacturer. Data analysis programs were developed to allow for the rapid determination of statistically significant parameters and to characterize their spatial variation over the wafer for further process analysis.

The program developed, called STAT2, allows one to determine the maximum, minimum, mean, and median values, the sample standard deviation ( $\sigma$ ), and the percent standard deviation of each parameter. A 50-character histograph can be produced to permit the user to see how the data are distributed between the minimum and maximum values. A value N can be selected such that all points farther than N times the sample standard deviation from the mean can be identified.

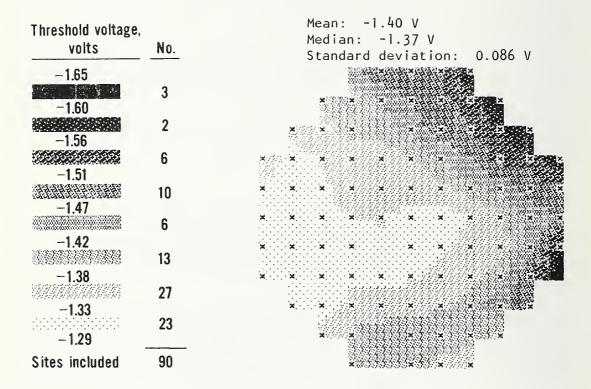

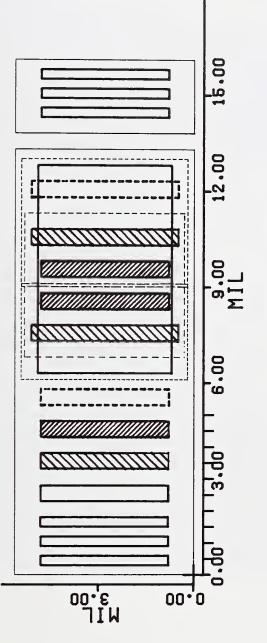

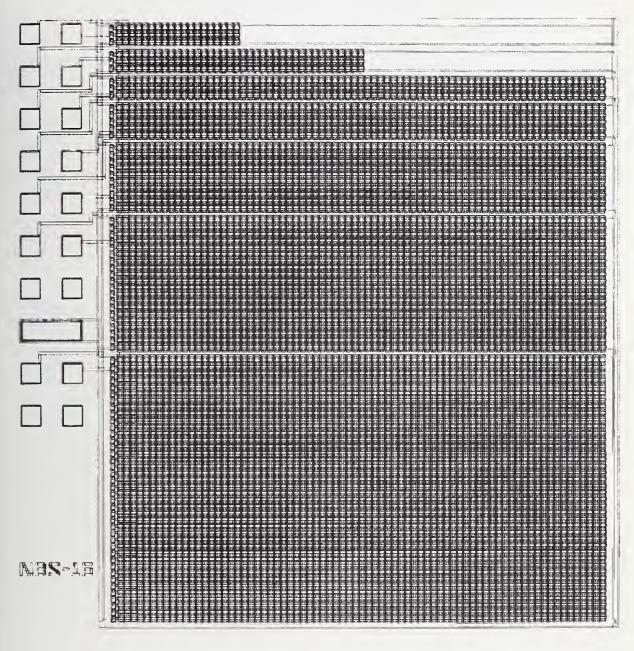

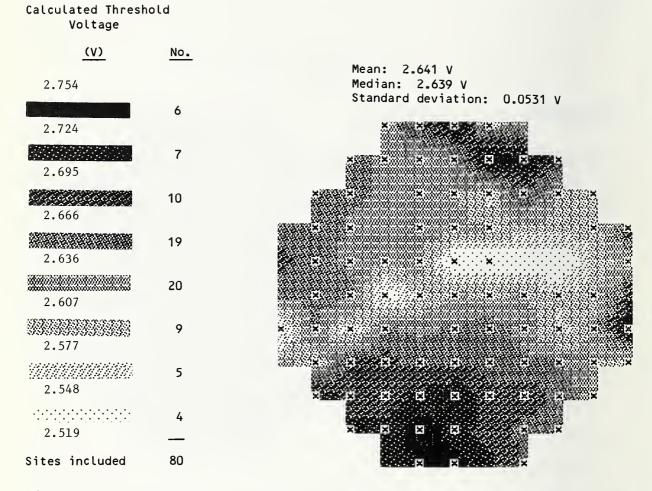

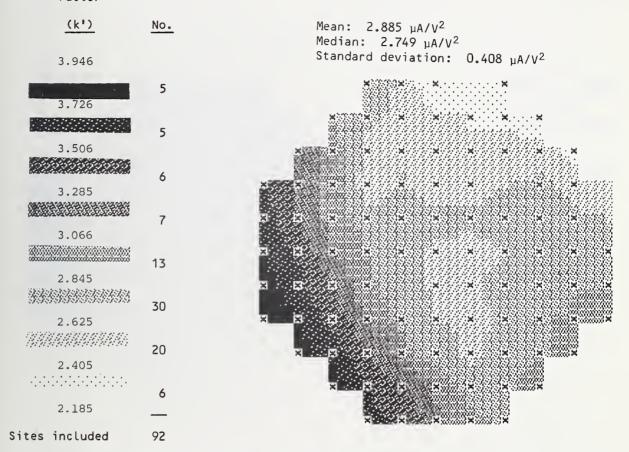

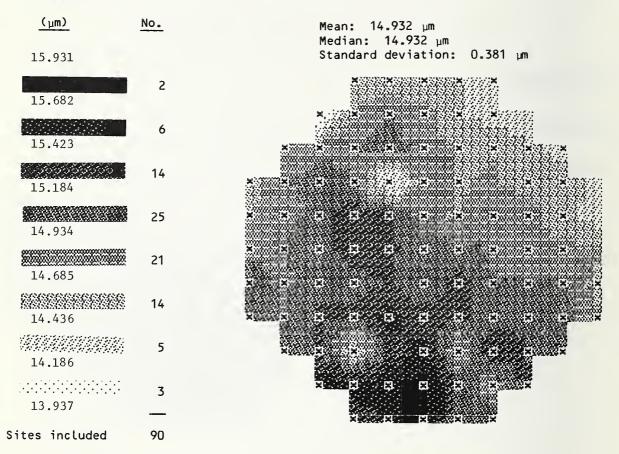

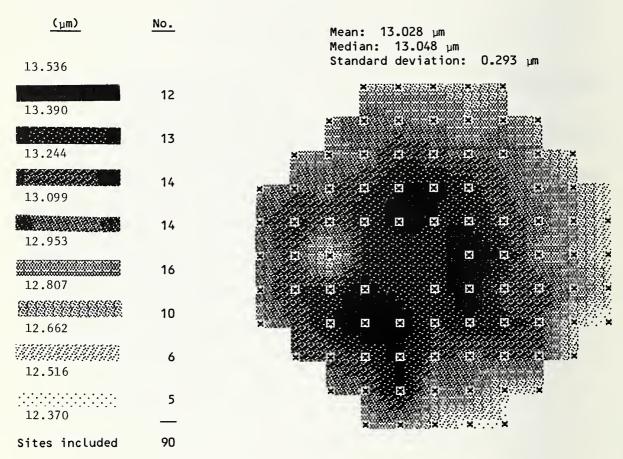

For this work, all parameters measured except for leakage current were assumed to have a Gaussian distribution. In order to separate and identify devices which had failed and remove them from the data set from which meaningful statistical analysis could be performed, it was necessary to specify an exclusion criterion. For this work a device parameter was considered not to be representative of the baseline process if the parameter was outside a  $\pm 3\sigma$ limit about the mean value for that parameter. On the average, for a population of 95 independent samples, the expected number of points that would fall outside this limit is between 0 and 1. This limit was considered a reasonable basis for identifying and separating data from the original population. When such data were present, the data were excluded from the population and the mean recomputed. This process was repeated until no points outside a  $\pm 3\sigma$ bound were found. This data base was then used to produce an eight-level gray-scale wafer map as shown in figure 5. For this figure, each "×" represents the location of a measured structure. Averaging techniques were used to determine the shading for sites excluded from the data population or locations not measured. The magnitude of each of eight levels is determined initially by simple division of the parameter range between maximum and minimum values. In order to produce wafer maps which represent parameter variations over a predetermined range of interest, the upper bound of the highest level and the lower bound of the lowest level can be varied by the operator. When the bounds are varied, a "+" is used to denote the location of a structure with a parameter magnitude greater than the highest level of the upper bound, and a "-" is used to denote the location of a structure with a parameter the lower bound of the lowest level.

#### 5. EVALUATION

#### 5.1 Process Parameter Pattern

In order to control a developmental integrated circuit process, a process engineer must:

- (a) identify which parameters accurately predict or determine the degree of process control;

- (b) establish the value and range, etc., of these parameters for a given process lot; and

- (c) determine how these values vary across an integrated circuit die, across a wafer, from wafer to wafer, and from lot to lot.

Test results must be obtained and interpreted in a timely fashion in order to be used for correcting or improving the process. A PVW containing appropriate process parameter test structures can be used to obtain test results which provide:

- (a) a statistically significant estimate of the value and range of critical process parameters;

- (b) the variation in these parameters as a function of wafer location; and

- (c) the lot-to-lot variation in critical parameters.

As will be shown later, the spatial variation of critical parameters can be used to establish correlations between different parameters and allow identification and evaluation of wafer processing problems. In some instances the spatial variation of certain parameters can be used to infer the variability of parameters which cannot otherwise be determined by test structures or test methods that are available.

For this work, the process parameter patterns on 18 NBS-16 PVWs (wafers A1 through A18) from 17 different lots were evaluated. Wafers A16 and A18 were processed in the same product lot. The process parameter patterns from one entire lot of 11 NBS-26 test patterns (wafers B1 through B11) were also evaluated.

11

Figure 5. Typical computer-generated (eight-level) gray-scale wafer map showing test site location and intrawafer parameter variation.

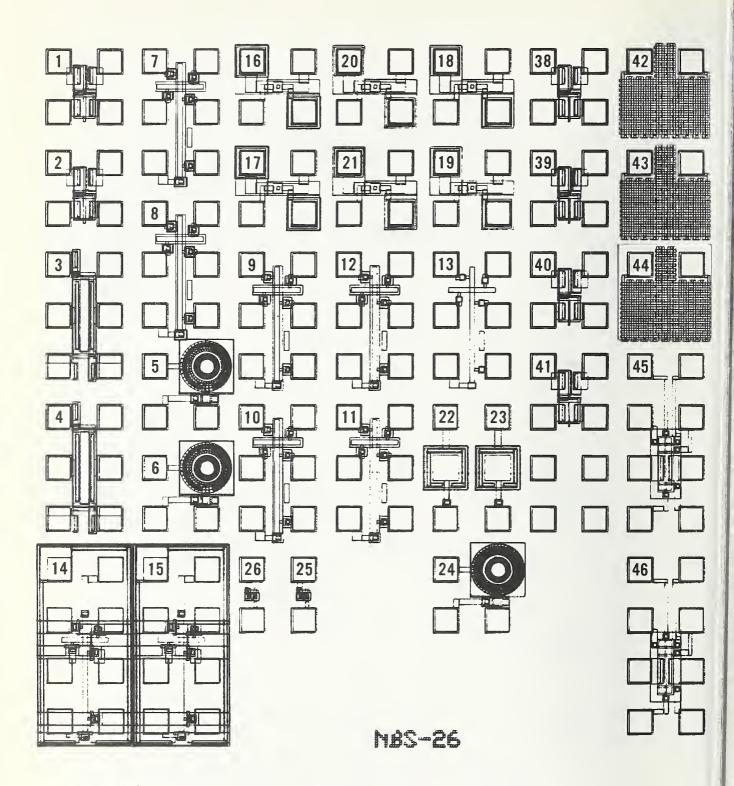

The process parameter pattern included on NBS-16 in Area I is a square approximately 100 mil (2.54 mm) on a side and contains 28 test structures laid out in 2 by N probe-pad arrays [5]. The 2 by N probe pad array allows for the use of one common probe card for wafer probing. It also allows great ease and flexibility in test pattern design. For the process parameter pattern on NBS-16, N varies between 10 and 14 depending on the column. Testing was performed using a 2 by 10 probe card. The pattern on NBS-26 is of similar size and probe-pad arrangement and contains 35 test structures. The process parameter pattern for NBS-16 is shown in Appendix B, figure B-3, and for NBS-26 in Appendix B, figure B-4. A description of each test structure and corresponding test method employed in this study can also be found in this Appendix.

The test structures that were selected for inclusion in the process parameter pattern were those that were judged to provide the maximum number of useful process parameters within the available space on the test die and to minimize the testing constraints imposed by the automatic testing system. The test structures listed in table 3 were those which were evaluated to determine the baseline electrical characteristics of the process. Additional developmental structures were also included on the patterns. Test results from the process parameter pattern were obtained using the automatic wafer prober and data analysis techniques previously described. The parameters measured, described in Appendix B, were selected to provide information of sufficient accuracy while minimizing the testing time and test equipment utilization.

#### 5.1.1 Lot-to-Lot Contact Resistance Variation

The lot-to-lot variation in critical parameters can be used to monitor the degree of process control. Plots of the lot-to-lot variation in the average metal-to- $n^+$  contact resistance (Device no. 19) and the average metal-to- $p^+$  contact resistance (Device no. 18) are shown in figure 6. Data presented are from PVWs A1 through A18. Each point plotted represents the average resistance of approximately 95 test structure measurements on each PVW. Since the contact resistor test structure [6] is a four-terminal Kelvin-type structure with current taps separated from voltage taps, the effects of probe-to-probe-pad contact resistance or the series resistance of the epi layer or metal layers connecting the probe pads to the voltage taps do not affect the measurement.

The test results indicate a wide range in the metal-to- $n^+$  contact resistance from lot to lot. Since little variation is observed in metal-to- $p^+$ contact resistance and because both contact resistors are adjacent devices, and the contact window is defined in the same photolithographic process for both structures, variations or problems with contact window photolithography, etching, and subsequent thermal processing are not suspected. The magnitude of the variations in metal-to- $n^+$  contact resistance indicates problems associated with other aspects of process control.

#### 5.1.2 Intrawafer Contact Resistance Variation

Further information relating to the lot-to-lot contact resistance variation can be obtained by looking at the intrawafer variation in these parameters and establishing correlations with other process parameters. Wafer maps of

| ucture<br>No. | Description                                           |  |  |  |  |  |

|---------------|-------------------------------------------------------|--|--|--|--|--|

| 1.            | p-channel four five-terminal MOSFET                   |  |  |  |  |  |

| 2.            | n-channel four five-terminal MOSFET                   |  |  |  |  |  |

| 3.            | n-channel five-terminal MOSFET                        |  |  |  |  |  |

| 4.            | p-channel five-terminal MOSFET                        |  |  |  |  |  |

| 9.            | $p^+$ cross-bridge sheet resistor                     |  |  |  |  |  |

| 10.           | n <sup>+</sup> cross-bridge sheet resistor            |  |  |  |  |  |

| 11.           | $p^+$ doped poly cross-bridge sheet resistor          |  |  |  |  |  |

| 12.           | n <sup>+</sup> doped poly cross-bridge sheet resistor |  |  |  |  |  |

| 13.           | Metal cross-bridge sheet resistor                     |  |  |  |  |  |

| 18.           | Metal to $p^+$ contact resistor                       |  |  |  |  |  |

| 19.           | Metal to $n^+$ contact resistor                       |  |  |  |  |  |

| 20.           | Metal to $p^+$ doped poly contact resistor            |  |  |  |  |  |

| 21.           | Metal to $n^+$ doped poly contact resistor            |  |  |  |  |  |

| 22.           | <i>p</i> -type MOS capacitor                          |  |  |  |  |  |

| 23.           | <i>n</i> -type MOS capacitor                          |  |  |  |  |  |

Table 3. List of Structures Evaluated on Process Parameter Patterns.

Figure 6. Average metal-to- $n^+$  contact resistance,  $\Omega$ , *versus* lot number and average metal-to- $p^+$  contact resistance,  $\Omega$ , *versus* lot number. Data presented show the variation in the electrical parameters over a time interval of approximately two years.

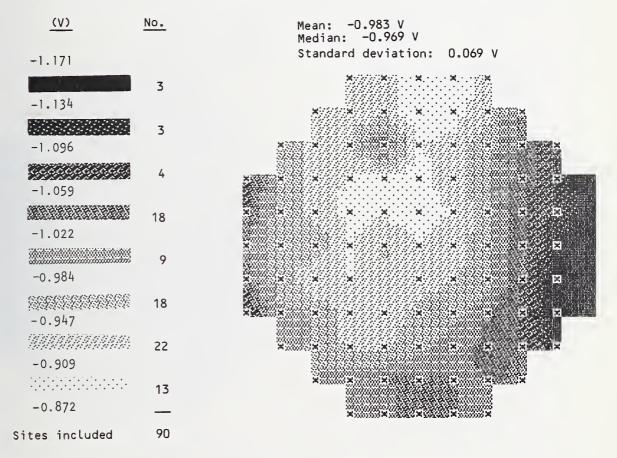

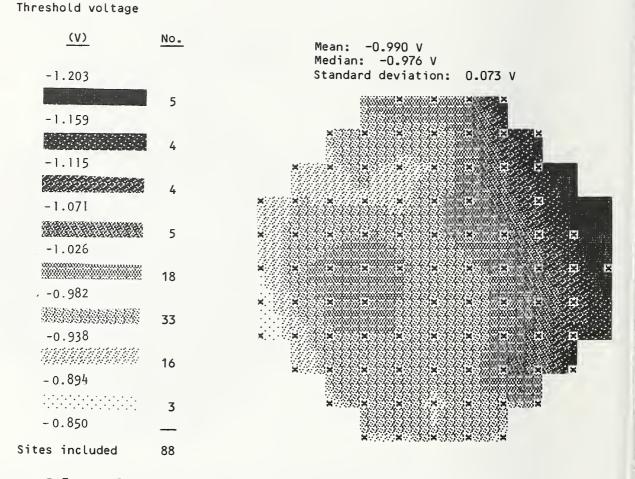

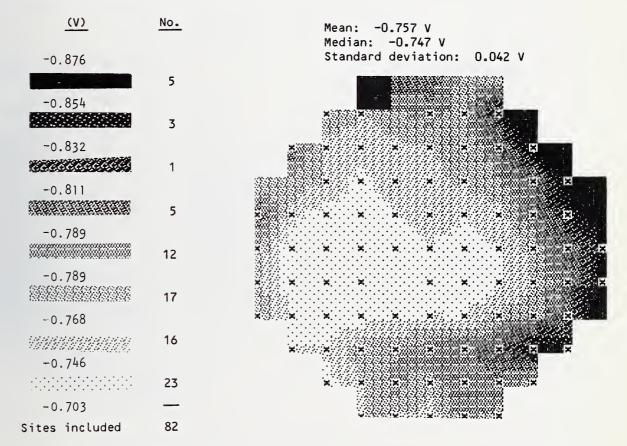

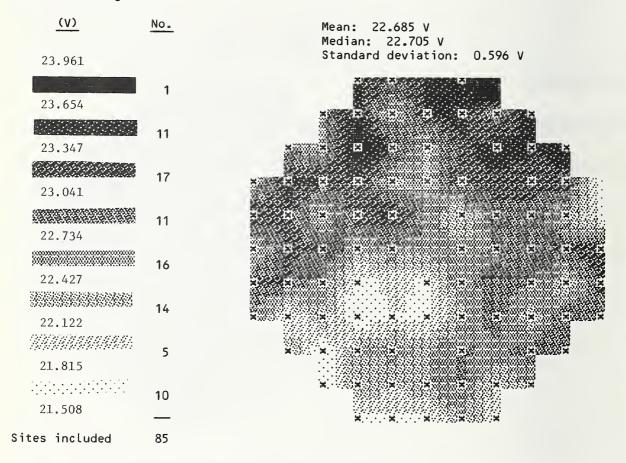

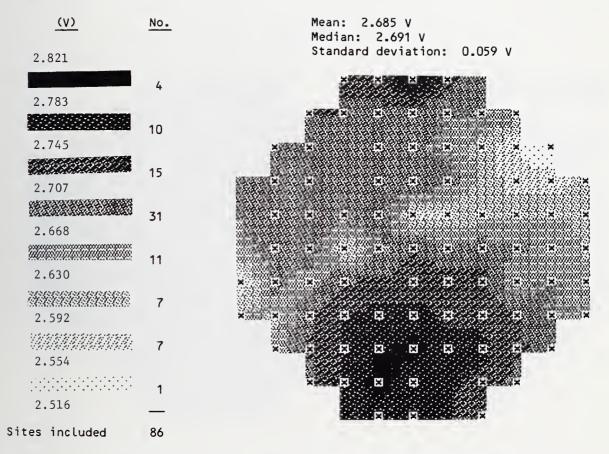

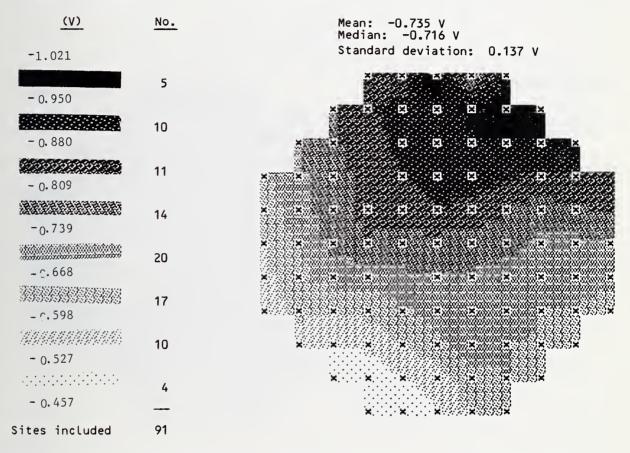

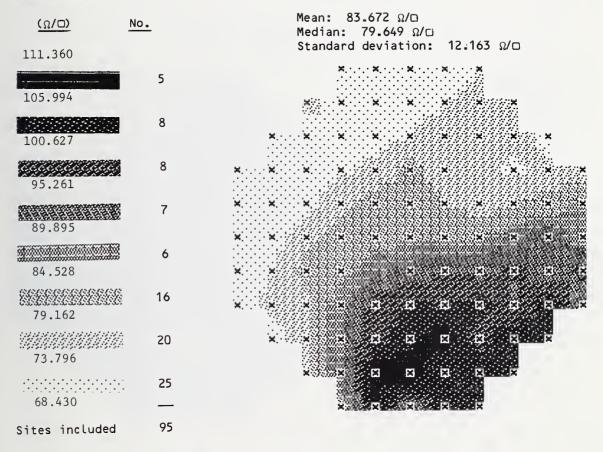

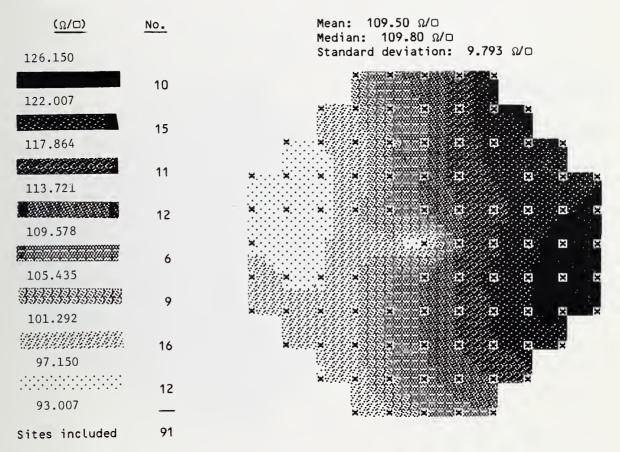

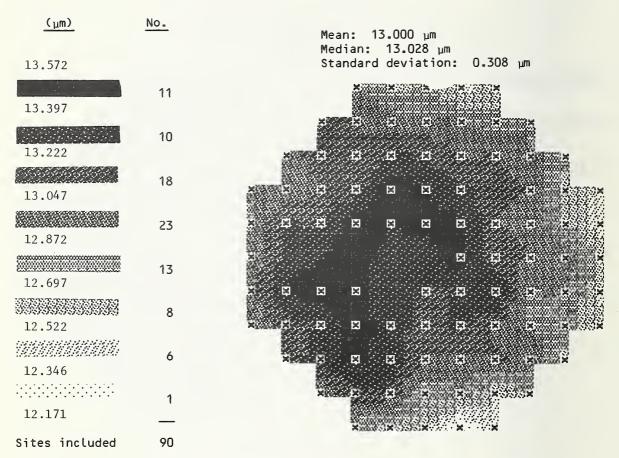

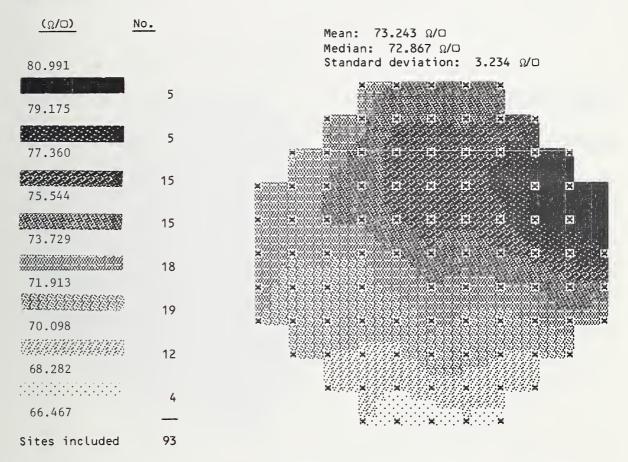

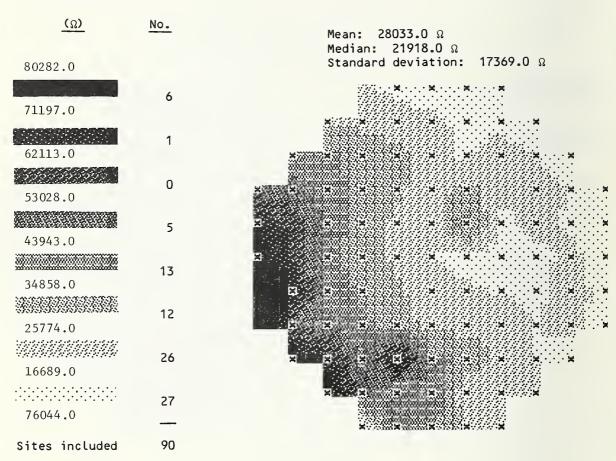

metal-to- $n^+$  contact resistance and  $n^+$  sheet resistance for the PVWs accompanying lots A10 and A9 are shown in figures 7 and 8, respectively. For lot A10, both the mean and median values of metal-to- $n^+$  contact resistance and of  $n^+$  sheet resistance are approximately equal. The approximate correlation of the map pair in figure 7 suggests that the high metal-to- $n^+$  contact resistance is a function of sheet resistance or phosphorus concentration.

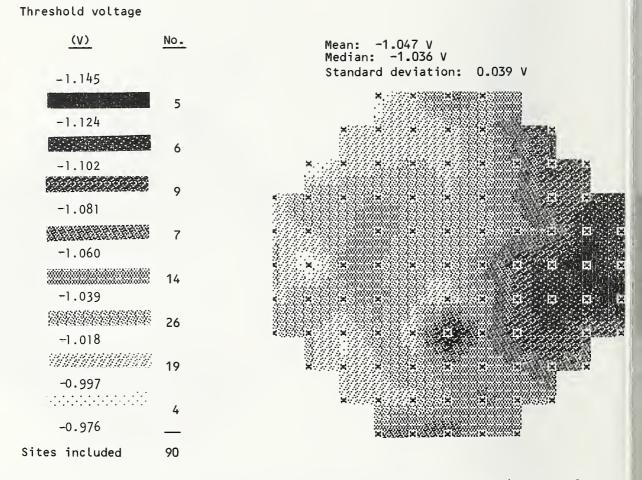

For lot A9, as shown in figure 8, there is a large difference between the mean and median values for metal-to- $n^+$  contact resistance. Approximately two-thirds of the metal-to- $n^+$  contact resistance structures measured had a resistance below 40.7  $\Omega$ . The remaining structures with a resistance higher than this value are grouped in the lower right portion of the PVW. The shading scale used both in this illustration and in figure 7 was determined by dividing the range between the lowest and highest parameters obtained into eight segments of equal magnitude.

The accompanying  $n^+$  sheet resistance data have approximately equal mean and median values suggesting a more symmetrical distribution of measured parameters. Here, the wafer map was produced by adjusting the minimum bound of the parameter shading range so that approximately the same number of points would be included for the first seven levels as for the first seven levels of the metal-to- $n^+$  contact resistance map. Values of  $n^+$  sheet resistance falling below this bound are represented by the lightest gray tone. As can be seen in figure 8, the highest metal-to- $n^+$  contact resistance occurs in the regions of highest  $n^+$  sheet resistance.

The sheet resistance of the measured structures was controlled by a two-stage phosphorus implant. The first implant was intended to dope the majority of the epi island region. The second was intended to increase the dopant concentration at the island surface in order to decrease contact resistance in source and drain regions. Both implants were made through a gate oxide which covered the epi island.

Subsequent capacitance measurements on the p-type MOS capacitor (Device no. 21) on the PVW from lot A9 indicated that the gate oxide thickness was greatest in the areas of lowest phosphorus concentration.

Based on this wafer map correlation, it was concluded that due to variations in the gate oxide thickness which were unaccounted for in the process design, the peak of the phosphorus implant varied between the silicon and silicon dioxide depending upon the oxide thickness. This caused significant variations in the amount of phosphorus reaching the silicon surface during the implant and caused the observed variation in metal-to- $n^+$  contact resistance.

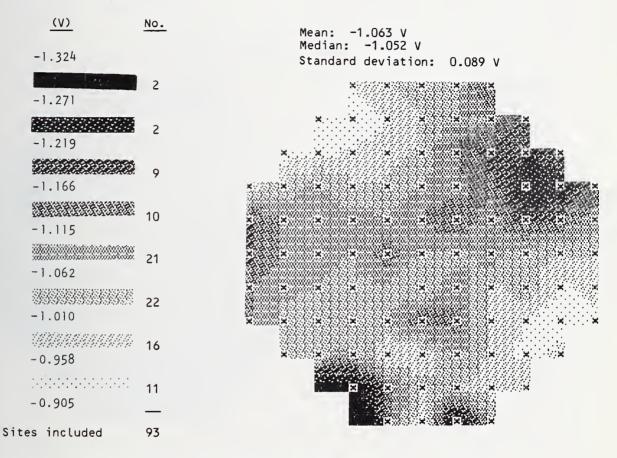

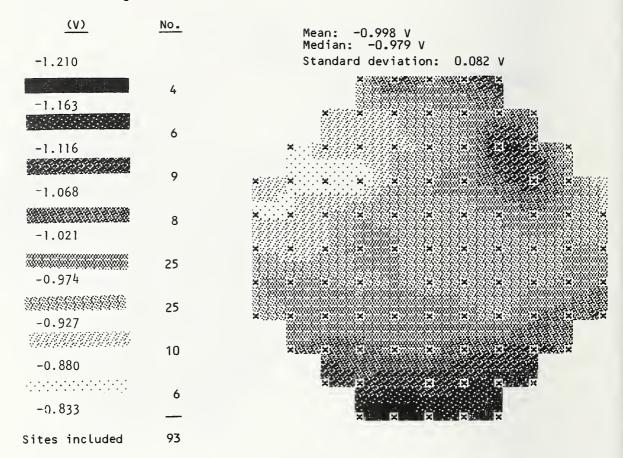

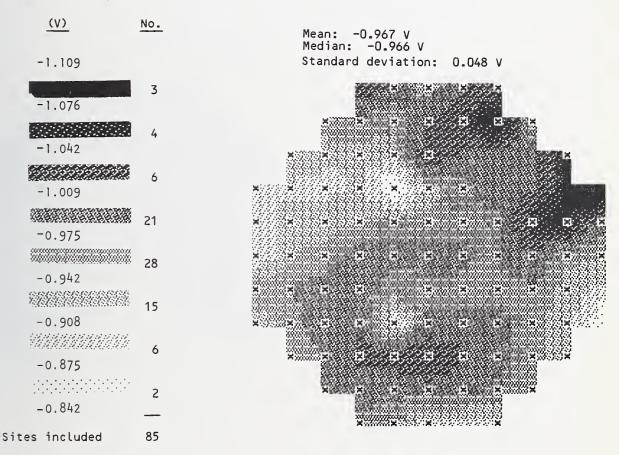

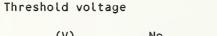

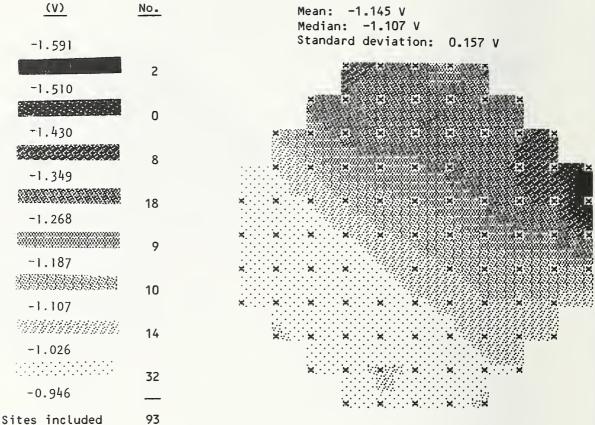

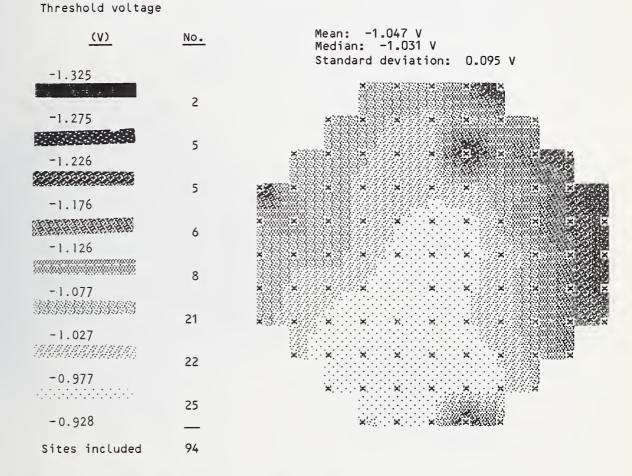

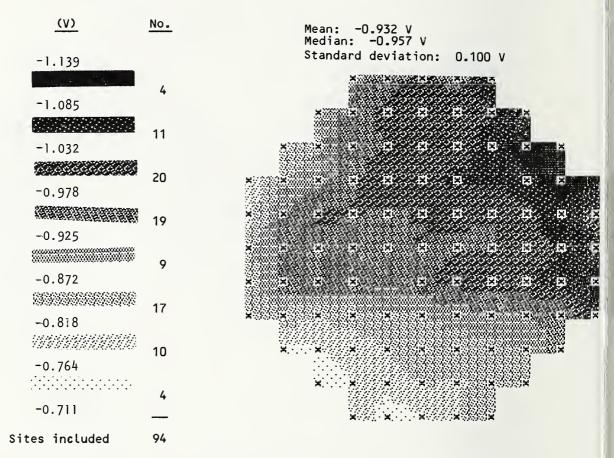

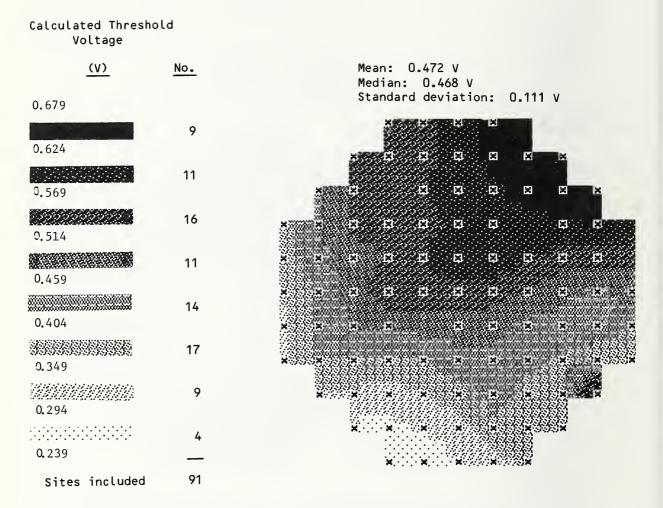

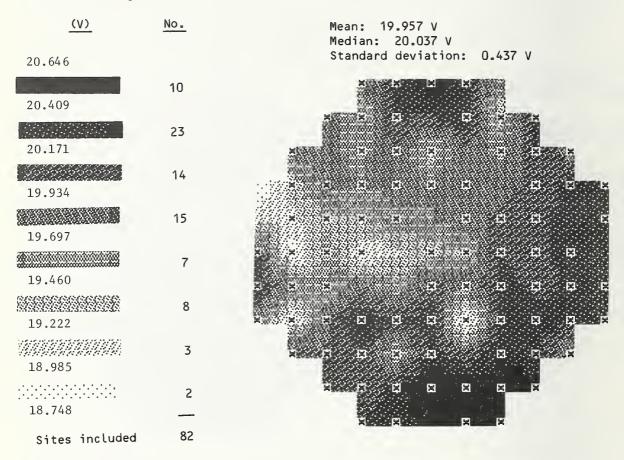

5.1.3 Lot-to-Lot p-Channel Threshold Voltage Variation

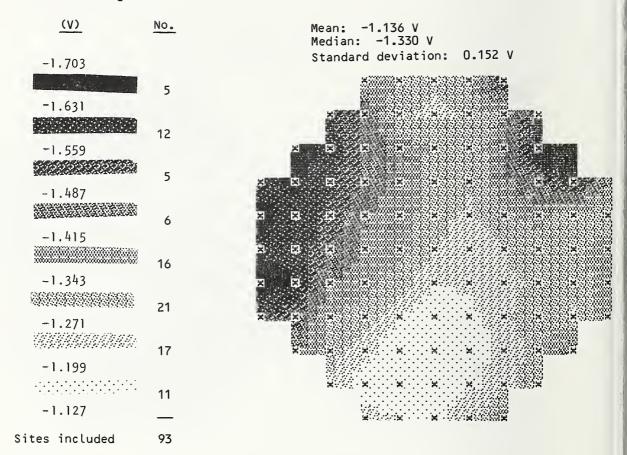

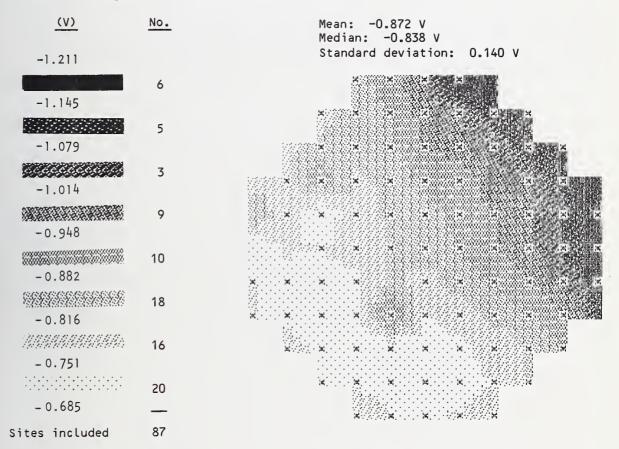

Wafer maps for one-parameter, p-channel threshold voltage of Device no. 1, for all 18 PVWs produced, are reproduced in Appendix C. These results are illustrative of how a single parameter can vary across a wafer and from lot to lot. The data presented are the p-channel threshold voltage of Device no. 1.

| Resistance,<br>ohms | No. |

|---------------------|-----|

| 314.4               | _   |

|                     | 1   |

| 281.3               |     |

|                     | 5   |

| 248.3               | -   |

|                     | 5   |

| 215.3               | 10  |

| 102.2               | 12  |

| 182.3               | 18  |

| 149.2               | 10  |

| 14J.2               | 25  |

| 116.2               | ZJ  |

| 110.2               | 11  |

| 83.2                |     |

| 03.2                | 10  |

| 50.1                | 10  |

| Sites included      | 87  |

|                     | 07  |

Figure 7. Wafer maps of metal-to- $n^+$  contact resistance (top) at 87 test sites and  $n^+$  sheet resistance (bottom) at 90 test sites for NBS-16 PVW AlO. In both maps, the scale or gray-tone boundaries were selected such that the upper bound of the darkest gray tone was the largest resistance value, and the lower bound of the lightest gray tone was the smallest resistance value. The "×" symbols on the maps represent the locations of nondefective test sites. Test results from these sites were used to calculate mean, median, and standard deviation and also to produce the wafer map.

Figure 8. Wafer maps of metal-to- $n^+$  contact resistance (top) at 91 test sites and  $n^+$  sheet resistance (bottom) at 95 test sites for NBS-16 PVW A9.

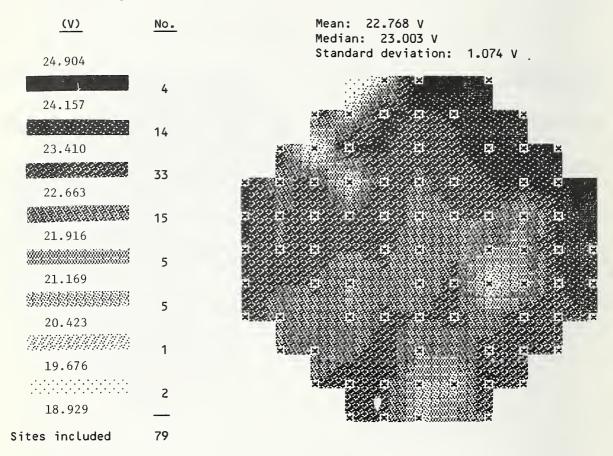

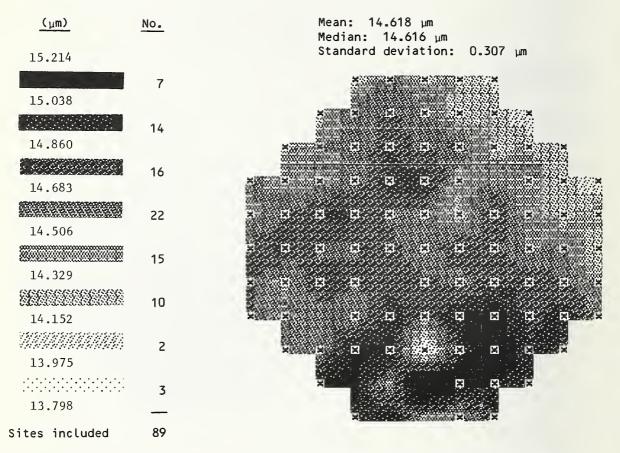

Two of these wafer maps of p-channel threshold voltage are shown in figure 9. As can be seen, a general similarity in the two maps exists with higher valued parameters located in the upper right of the map and lower valued parameters located in the lower left. A majority of the 18 wafer maps in Appendix C contain this general pattern. This suggests that usually the p-channel threshold voltage is affected by processes in which the wafers are all similarly oriented with respect to the wafer flat.

There are two areas in the fabrication in which wafers are processed with the wafer flat location remaining the same: photolithography and epitaxial growth. In general, threshold voltage variation correlating with a lithography variation is not expected for MOSFETs of the size (0.3 mil, 8  $\mu$ m) being tested. Variations in linewidth of poly, epi, and metal can be found in the appropriate wafer maps in Appendix D which contains a complete set of wafer maps and statistical data. No correlation with threshold voltage was observed.

A simple expression for the threshold voltage of a p-channel silicon gate MOSFET is [7,8]:\*

$$V_{T} = \phi_{SS} + \phi_{B} - \frac{Q_{OX}}{C_{OX}} - \frac{Q_{B}}{C_{OX}} .$$

(1)

where  $\phi_{ss}$  = effective work function of the silicon-oxide-silicon system,  $\phi_B$  = total band bending at the onset of strong inversion,  $Q_{ox}$  = total surface state charge located at the silicon-silicon dioxide interface,  $Q_B$  = charge contribution of the substrate depletion region, and  $C_{ox}$  = the gate oxide capacitance.

In general,  $\phi_{SS}$  is a function of the gate electrode material, polysilicon. The sum of both  $\phi_{SS}$  and  $\phi_B$  is approximately constant for a given gate electrode technology.  $C_{OX}$  for the most part varies with changes in the gate oxide thickness.

The main factors affecting the variation in  $Q_{OX}$  are substrate crystal orientation, oxidation conditions, and subsequent thermal processing.  $Q_B$  is given by

$$Q_{\rm B} = \left(2\varepsilon_{\rm S} \ q \ N_{\rm D} \ \left[-\phi_{\rm B}\right]\right)^{1/2} , \qquad (2)$$

where  $\varepsilon_s$  = the permittivity of silicon, N<sub>D</sub> = the substrate dopant concentration, and q = the electronic charge.

Thus, Q<sub>B</sub> varies mainly with changes in the substrate dopant concentration.

Dopant concentration for the  $n^-$  islands is determined in the epitaxial growth process. No other epi island doping is intentionally performed. For this process, the wafer flat location relative to the gas injector within the

<sup>\*</sup> The cited references provide a more detailed description of the parameters affecting the threshold voltage.

Figure 9. Wafer maps of p-channel threshold voltage at 83 test sites for PVW Al6 (top) and PVW All (bottom).

epitaxial reactor is both the same for each wafer and the same from lot to lot. A pancake type of vertical reactor was used with a rotating susceptor. During the epitaxial growth process, if depletion of the dopant species were to occur across the susceptor, a systematic variation in the epi island dopant concentration across each wafer would occur.

Other factors which influence threshold voltage, such as  $Q_{\rm OX}$  and  $C_{\rm OX}$ , are governed by gate oxide growth, anneal, sinter, and poly deposition, processes which are performed with uncontrolled wafer flat orientation. If these processes were the major factors governing the variation in *p*-channel threshold voltage, similar variations in the *n*-channel threshold voltage would also be observed. Lot-to-lot variation in *p*-channel threshold voltage as a function of variation in  $Q_{\rm OX}$  or  $C_{\rm OX}$  is not anticipated because of the uncontrolled wafer orientation during the processes which affect these parameters. This observation is further supported by the lack of any correlation between *p*-channel and *n*-channel wafer maps for the same PVW. These test results suggest that the dominant source of variation in *p*-channel threshold voltage is the variation in epi island dopant concentration. The observed variation is consistent with the expected dopant variation introduced during epitaxial growth.

There are no test structures or test methods available from which the *n*-island concentration can be directly determined. By determining the variation of threshold voltage across the wafer and from wafer to wafer, it was possible to identify processing techniques which affected the control and variability of this critical quantity.

#### 5.1.4 Intralot Parameter Variation

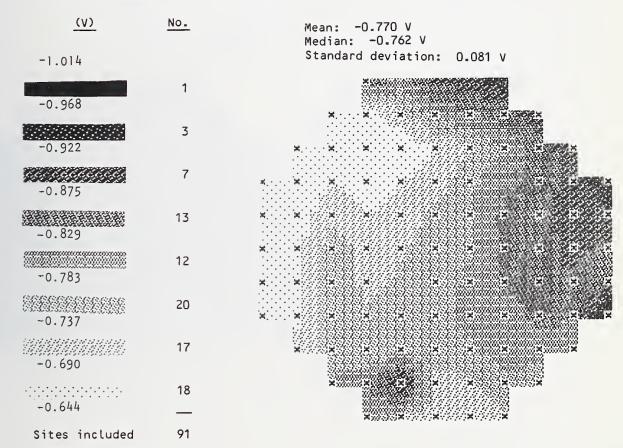

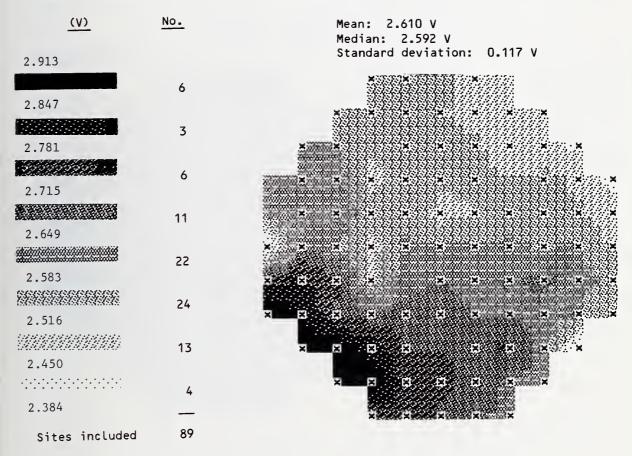

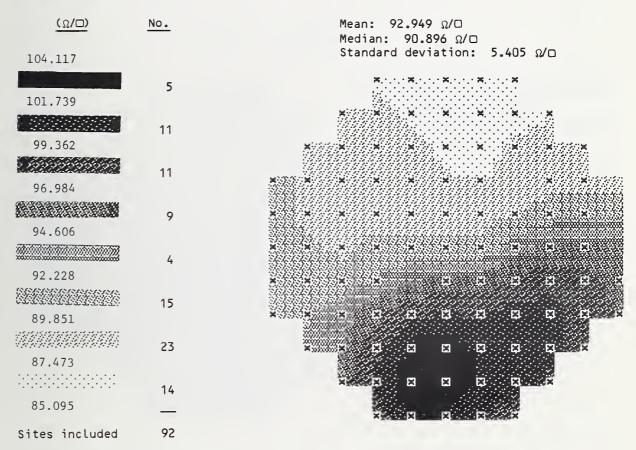

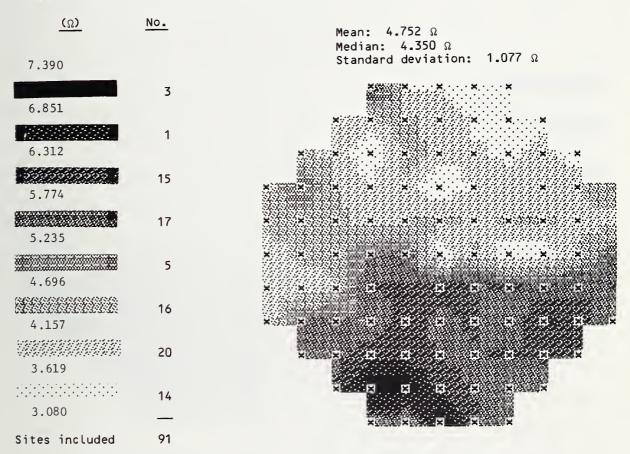

One 11-wafer lot of NBS-26 test patterns was produced in order to qualify the functionality of the mask set for NBS-26. Test results from the process parameter pattern indicated the presence of functional MOSFETs on three of the 11 wafers produced. Analysis of electrical tests on the remaining wafers indicated the absence of electrical contact between the device being tested and the wafer prober. Further analysis indicated that the metal cross-bridge sheet resistors (Device no. 13) on all 11 wafers were functioning properly and providing expected test results. These results indicate that adequate probe-to-probe-pad contact is being made and that the electrical problems being encountered are associated with the contact windows between metal and all other conductive layers. From visual inspection, it was determined that the contact window lithography step had been performed. The presence of a contact window problem was confirmed by test results from one of the PVWs containing functional devices.

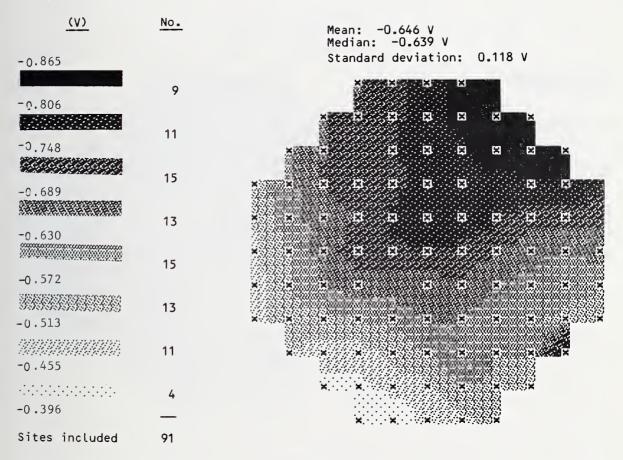

Figure 10 contains wafer maps of *n*-channel threshold voltage and  $n^+$  sheet resistance for PVW B4. The threshold voltage wafer map indicates that nonfunctional MOSFETs are clustered in the upper right portion of the map. Voltages exceeding 12 V for this measurement indicate that the voltage limit for the programmable current supply was reached due to an open circuit in the structure under test. Similarly, the  $n^+$  sheet resistance shows the location of nonfunctioning cross-bridge resistors. Test results from the crossbridge sheet resistors in the upper right portion of the PVW show that a voltage limit had again been reached. (For the van der Pauw sheet resistance

21

Figure 10. Wafer maps showing location of nonfunctional n-channel MOSFETs (top) and  $n^+$  sheet resistor test structures (bottom) for NBS-26 PVW B4.

measurement, a current is forced through two adjacent taps of the structure, and voltage is measured at the two remaining taps. Sheet resistance is then calculated from the voltage measured for a fixed current in the structure. When electrical contact is not made to the structure, no voltage is measured between the voltage taps, and the calculated sheet resistance is approximately zero.)

Based on these data, it was possible for the manufacturer to isolate the source of the processing problem to that portion of the process between contact window lithography and metallization deposition. Further evaluation by the manufacturer revealed that a change in a premetallization chemical cleaning procedure had occurred and that contamination was being introduced during one of the wafer drying steps.

#### 5.2 Random Fault Test Structure Evaluation

A random fault test structure is a microelectronic structure which can be electrically tested in order to determine the density of certain types of faults associated with the fabrication process [9]. These structures usually consist of arrays of identical elements connected electrically in a series, parallel, or addressable configuration. Two types of developmental random fault test structures were included on NBS-16 and NBS-26.

The purpose of using a random fault test structure on a test pattern is to provide the user and manufacturer with a tool which can be used to assess the yield potential and identify the principal yield detractors associated with the process being used. For the manufacturer, test results can be used to identify, quantify, and correct yield-limiting processes in the fabrication process. For the user, test results can be used to monitor the manufacturer's performance with time, rate the performance of multiple manufacturers, or accept or reject products.

Several factors must be considered before selecting and using a random fault test structure. Briefly, they are:

- (a) What type of structure should be used? If the structure selected does not provide information about principal fault mechanisms in the process, test results and analysis will be of little use in improving yield.

- (b) What size should the structure be? If a series or parallel type of array is used and the array size is too large, all arrays will probably contain at least one fault. On the other hand, if the array size is too small, a single array has a high probability of containing no faults. If a large number of small arrays is employed, testing time and probing difficulties increase. The array size for a single structure must be selected such that enough faults will be detected that some form of statistical analysis can be performed.

- (c) Is the fault detected the intended fault? If a structure were used to detect dielectric faults in capacitor arrays and serious metallization bridging between interconnect lines from probe pads to the

capacitors occurred, a fault would be detected, but the identity of the fault would be incorrect.

- (d) Is the fault detected a singular fault or a clustered fault? If, for instance, a continuity test is performed for a metallization interconnect and test results indicate a break, is the break at one location? Two? Ten?...

- (e) What degree of testing complexity and time is required to obtain meaningful information? If the time required to test and evaluate the structure is too great to provide timely information to the fabricator, the structure will be of little value.

One of the two random fault structures included on NBS-16 and NBS-26 is a new type of developmental fault structure which can both provide information on a variety of faults common to MOSFET devices and in general determine the location of the faults. The other structure, an MOS capacitor array, is a more conventional parallel array intended to determine the occurrence of gate dielectric failure at the epi island edge.

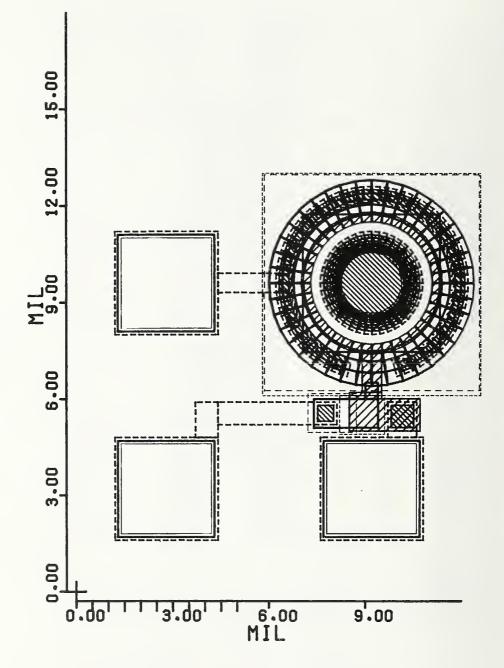

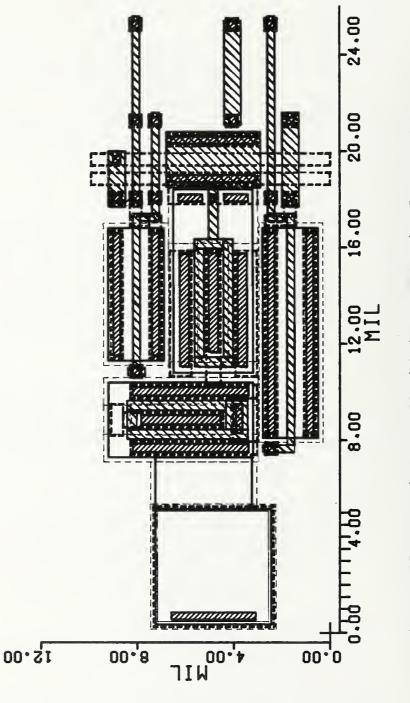

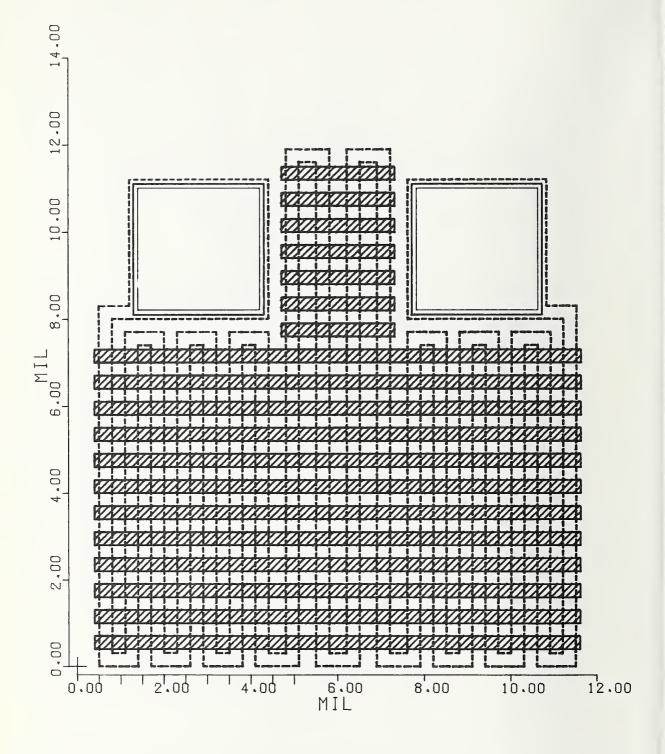

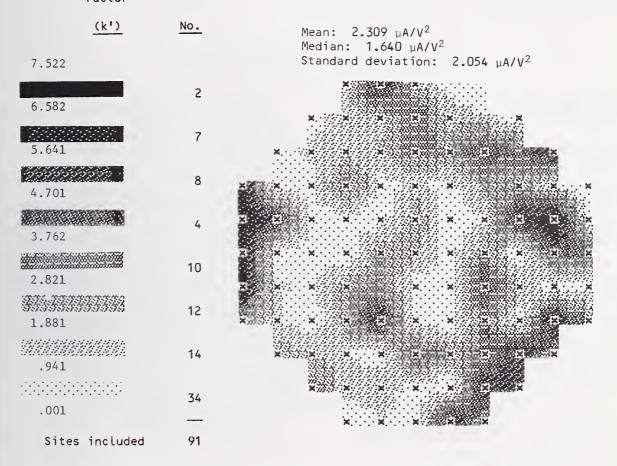

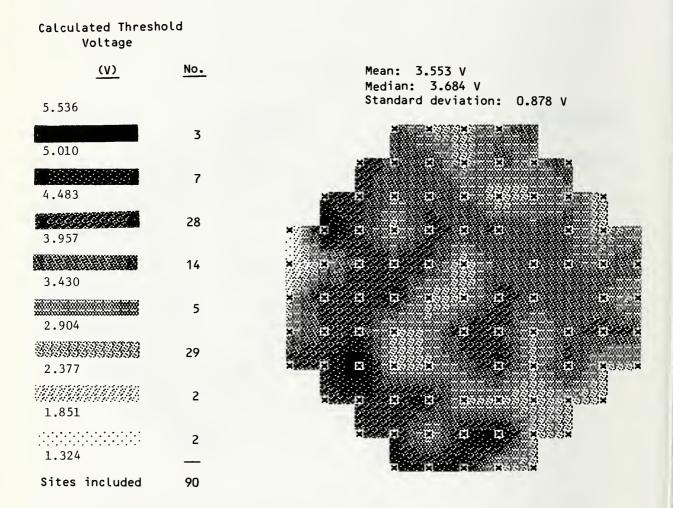

#### 5.2.1 Random Access Fault Structure (RFI)

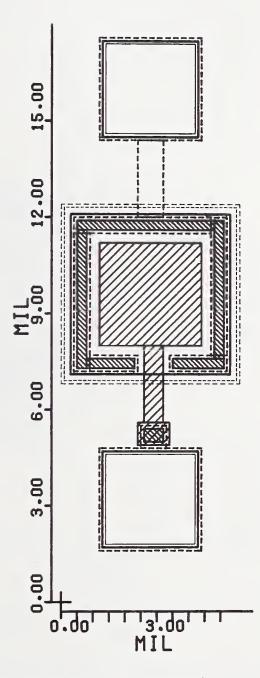

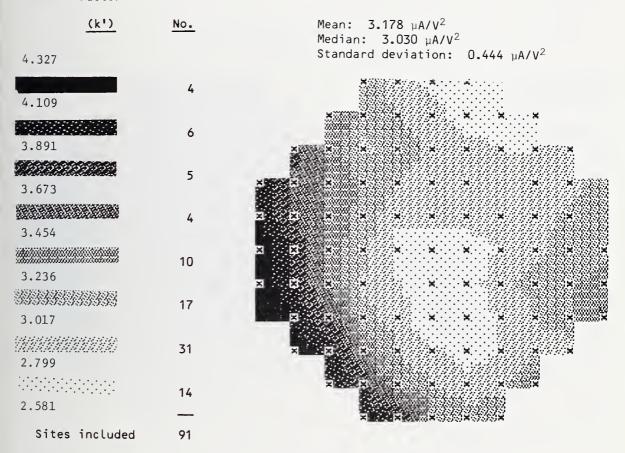

The purpose of including this type of structure on NBS-16 and NBS-26 was to develop a general purpose random fault structure which can be used to detect, identify, and evaluate faults common to MOSFET structures without foreknowledge of dominant fault type or fault density. The structure is a random access structure which allows one to identify different fault types and determine the exact location of the fault for further analysis. One can determine if the fault is singular or clustered and also obtain parametric electrical data which can be used in further analysis. In Area III, each NBS-16 test pattern contains four of the random access fault structures, shown in figure 11. The top two are p-channel; the bottom two are n-channel. Each structure contains a 10 by 10 array of minimum geometry MOSFETs. There are 400 MOSFETs per pattern and thus a total of 38,000 MOSFETs on the 95 sites of each PVW. Within each array, each MOSFET has the gate electrically tied to drain. The devices are arranged in rows and columns similar to a diode matrix. Each MOSFET is isolated from its neighbor and can be individually addressed by selecting the appropriate row and column probe pads as shown in figure 12. The vertical columns are made of metal, the rows of polysilicon. Each MOSFET has a gate size of 0.2 by 0.6 mil (5.1 by 15.2  $\mu$ m). Testing is accomplished in two phases with the automatic computer-controlled test system. The first phase, a row-to-row and column-to-column integrity test, is to establish whether there is electrical conductivity between adjacent rows or columns. If the structure passes this test, each MOSFET is individually tested to determine the threshold voltage measured at 1-µA source-to-drain current, the source-to-drain breakdown voltage measured at 10-pA source-todrain current, and the source-to-drain leakage current measured with the gate and drain grounded and source held at 10 V. These data and site location are recorded.

To evaluate the data, failure criteria must first be established. For this work, two criteria were recommended by the manufacturer as limits which, if exceeded, would result in circuit failure. They are:

NBS-16

Figure 11. Random access fault structure, RFI, contained on one NBS-16/26 test pattern. Top, two arrays *p*-channel MOSFETs; bottom, two arrays *n*-channel MOSFETs.

Electrical Interconnect

Figure 12. One random access fault structure RFI, showing a micrograph of a two-by-two section of MOSFETs and a schematic of the electrical interconnect.

- (a) a source-to-drain leakage current greater than 50 nA/mil (2 nA/ $\mu m$ ) gate width, and

- (b) a source-to-drain breakdown voltage less than 17 V or greater than 30 V. (This upper limit was an arbitrary bound to enable one to determine when the voltage compliance limit of the current supply was reached.)

A third criterion was also used. A MOSFET was considered to have failed if the threshold voltage was above or below a preselected bound. This bound can be determined from circuit simulation programs or past experience. Since no data were available from these sources on which more precise bounds could be established, the following criterion was used:

(c) A MOSFET was considered to have failed if the threshold voltage was outside the four-sigma limit where sigma is the sample standard deviation of the data from test results of discrete MOSFETs tested in the process parameter pattern. The threshold voltage data sample was assumed to follow a Gaussian distribution, and data falling outside this distribution were considered to be failures. For a population of approximately 25,000 independent samples, only a single valid datum was expected to fall outside this limit.

Figure 13 is a graphical presentation of the outcome of the test results of one array. By analyzing the test results and comparing the outcome of individual sites to the nearest neighbors, the exact fault location and the category of fault type can be determined. Examples of this are shown in figure 13. Visual inspection was used to confirm the indicated break in metallization and the dielectric gate short. By testing a large number of these arrays, a variety of different electrical fault types can be identified. These fault types can be separated into two basic groups: physical faults and parametric faults.

Physical faults are those which produce a definite physical failure which directly results in circuit failure. Examples are: poly, metal, or epi voids or breaks; poly, metal, or epi bridges; contact window opens; gate dielectric shorts; and poly or metal step coverage breaks. A parametric fault or parametric variation outside a predetermined bound may or may not produce a circuit failure. Examples of parametric failures are a high source-to-drain leakage current or low source-to-drain breakdown voltage. Failures caused by either physical or parametric faults may or not be visible.

Test results from the random access fault structure on PVWs accompanying product lots A6 and A1 are shown in figures 14 and 15, respectively. For these two lots, the product being manufactured consisted of a circuit containing about 5,000 transistors. PVW A6 accompanied a product lot which had a wafer probe yield nine times greater than the product lot accompanying PVW A1. Test results from test patterns on the interior 67 sites within the PVW are presented.

The detection of fault location is important because it provides information about how the faults are distributed over the area being tested. For a given number of faults, a nonuniform fault distribution generally results in a

FOR ONE ARRAY **RANDOM FAULT MEMORY-LIKE** STRUCTURE RESULTS TEST

- PARAMETERS WITHIN NORMAL LIMITS \*

- **OPEN CIRCUIT** ပ္ပ

- SHORT CIRCUIT SC

- PROBE PAD LOCATION

Test results for one RFI array from NBS-16 PVW Al. Figure 13.

30

Test results for 268 RFI structures from NBS-16 PVW Al (where  $I_{\rm L}$  is source-to-drain leakage current,  $V_B$  is source-to-drain breakdown voltage, and  $V_T$  is threshold voltage). Figure 15.

higher potential product yield as all of the faults tend to be located in a relatively few product sites. A more uniform fault distribution generally results in more product sites containing a fault and therefore a lower product yield. A more detailed description of the effects of fault distribution on product yield can be found elsewhere [10].

A fault is clustered when two or more adjacent transistor failures of the same or similar type are detected within an array. When this occurs, the entire cluster is counted as one clustered fault. As may be seen in figure 14, information on both clustered and nonclustered faults for PVW A6 is presented; however, few failures of either category were detected. Data for both p- and n-channel MOSFETs are plotted together. Based on these test results, it was possible to eliminate certain failure mechanisms as the principal cause of yield degradation. For example, no gate-to-source shorts were detected. Also, metallization coverage can be considered good. To test 26,800 MOSFETs required that 107,200 metallization steps be covered. Further testing at higher current levels confirmed the electrical quality of the step coverage.

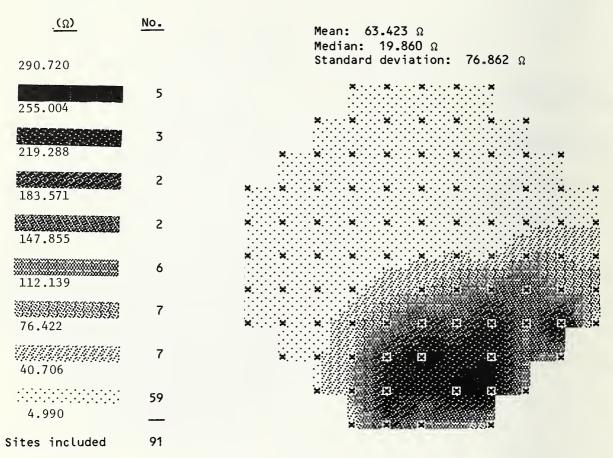

Test results from PVW A1 indicate the presence of a major yield-limiting fault type. The dominant fault detected is a nonclustered, parametric type fault. Eighty-seven out of 26,700 MOSFETs evaluated had a source-to-drain breakdown voltage or both a source-to-drain leakage current and breakdown voltage which fell outside one or more of the previously described failure criteria. Since the number of faults detected was approximately the same for both *p*- and *n*-channel MOSFETs, test results for both types are plotted together.

A histogram of breakdown voltage for all devices with a source-to-drain leakage current greater than the failure criterion is shown in figure 16. The distribution is peaked at about 14 to 15 V. In most cases, leakage current was much greater than the 50 nA/mil (2 nA/ $\mu$ m) of gate width failure criterion.

Because the location of each fault was known, selected MOSFETs were inspected; however, no visible defects were observed. When individually tested, the MOSFETs exhibited noisy soft breakdown characteristics. Figure 17 is a wafer map showing the approximate location of the faults that were detected by this technique.

This type of failure seems to be run-dependent, since test results from PVW A6 do not indicate a large number of these faults. At this time, further physical analysis is required to determine the exact nature and physical cause of this defect.

To summarize, by using a random access fault structure, it was possible to identify a yield-limiting fault which was unknown to the manufacturer and user at the time of test structure design and selection. The location of each fault could easily be determined from the test results. The dominant fault encountered had electrical characteristics with lower-than-normal source-to-drain breakdown voltage, with a mean of approximately 14 V, a source-to-drain leakage current greater than 50 nA/mil (2 nA/µm) of gate

Figure 16. Histogram of breakdown voltage,  $V_{\rm B},$  volts, with devices with a source-to-drain leakage current greater than 50 nA/mil (2 nA/µm) gate length for NBS-16 PVW Al.

Figure 17. Failure map showing approximate location of RFI structures containing MOSFETs with high source-to-drain current leakage. width, and was not clustered. Also, no visible defects were observed at each fault location.

The random access fault structure is important for two reasons. First, it has been demonstrated that test results can be used to identify the exact location of each fault. Further electrical or physical analysis can then be undertaken. Second, the random access fault structure is able to identify different fault types. In one example, a major fault was detected that had not been previously anticipated; this fault would not have been detected from the other test structures included on the pattern. The random access fault structure was able to provide test results that allowed the determination of the relative fault density and relative ranking of different fault types. The user and manufacturer can use this structure as a tool to identify the major yield-limiting process problems affecting their process.

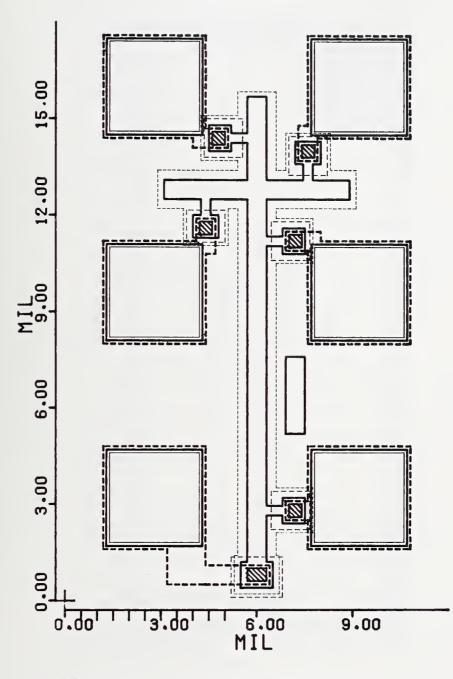

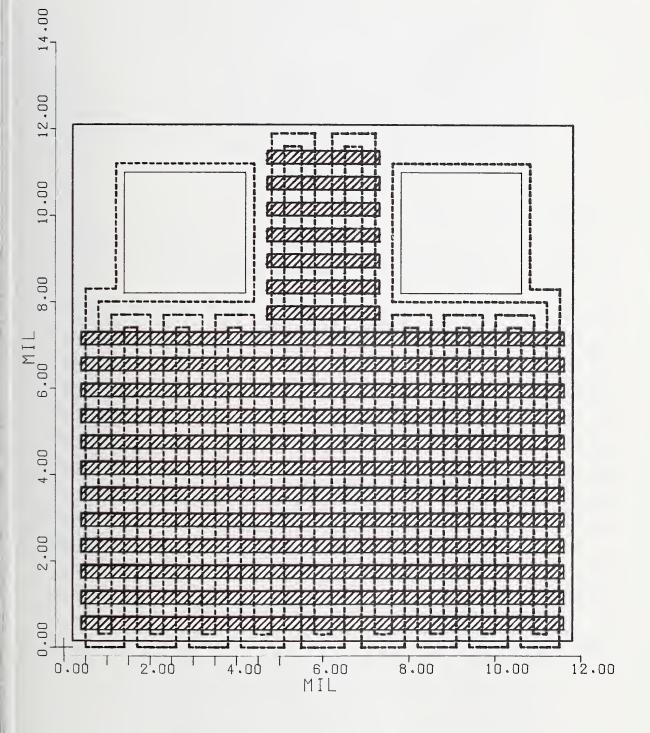

5.2.2 Gate Dielectric Integrity Array (RFII)

The purpose of including this type of random fault test structure on NBS-16 and NBS-26 was to develop and evaluate a structure which could be used to analyze one particular type of physical and electrical defect common to MOS-FETs made in an SOS technology, namely, gate dielectric leakage from poly-toepi island occurring through the gate oxide at the epi-island edge. The structure was designed such that metal-to-poly and metal-to-epi leakage could also be detected.

The approach taken was to design a parallel array type of random fault test structure consisting of subarrays of identical capacitor elements. Each subarray was then electrically tested and the results compared to a failure criterion. From these results, the yield (the ratio of the number of good subarrays to the total number of subarrays tested) could be determined for each subarray size. Similar types of structures have been described by others [9].

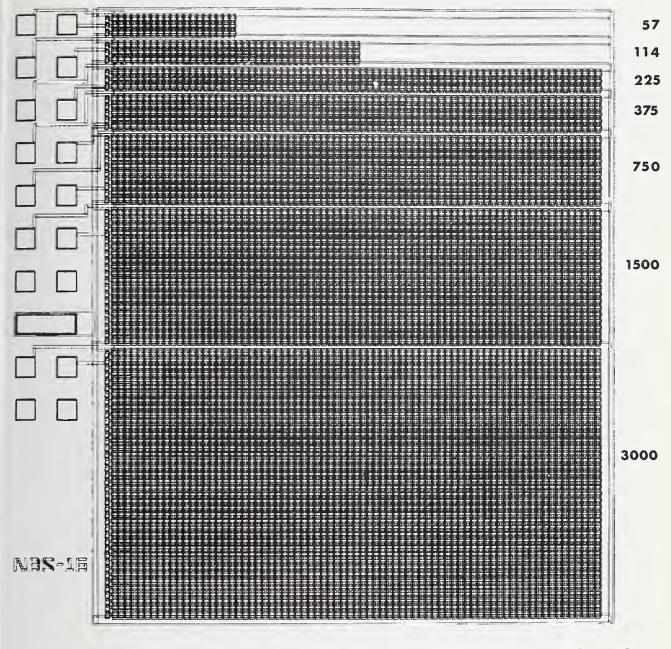

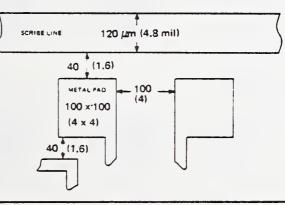

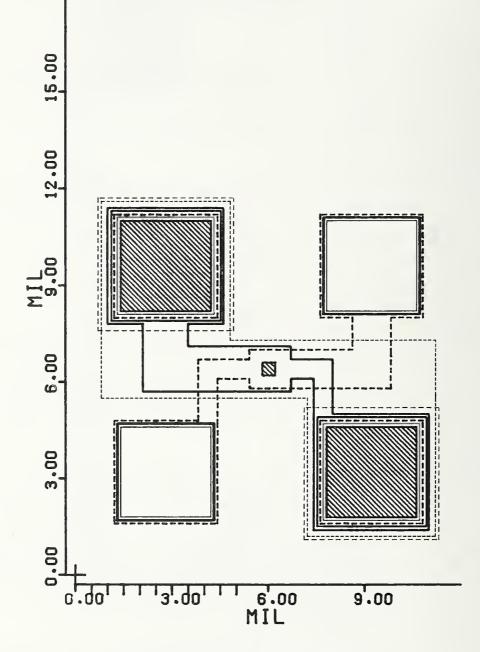

The gate dielectric integrity array, RFII, is shown in figure 18. The structure occupies Area IV of the test pattern. It contains capacitor arrays which can be used to detect poly-to-epi leakage caused by dielectric defects in the gate oxide. It can also be used to measure photolithography-induced defects or dielectric defects in the field oxide by detecting leakage between metal-to-poly and metal-to-epi levels. The structure is comprised of five layers on a sapphire substrate:  $n^-$  epitaxial silicon; gate oxide;  $p^+$  polysilicon; field oxide; and aluminum metallization. The poly lines are grouped to form seven subarrays with 57, 114, 225, 375, 750, 1500, and 3000 crossovers. The polysilicon and metallization in each subarray are each connected to a single probe pad; all of the epi lines in all of the subarrays are electrically common and connected to a single probe pad.

The size of the entire structure and the sizes of the subarrays were selected as an arbitrary compromise between maximizing the number of elements (capacitors) from which a statistically significant data base can be obtained and minimizing the overall size of the structure to one that could be reasonably included within the test pattern. There are 95 RFII structures on each PVW. Each structure is in a 100-mil (2.54-mm) square and can be probed by means of a 2 by 10 probe card.

Figure 18. Gate dielectric integrity array, RFII. The number of elements for each subarray is listed at the right.

For each structure, a probe-to-probe-pad continuity is first made on the two common probe pads shown in figure 18. The use of only one set of common probe pads for determining electrical continuity places a limitation on the overall usefulness of the test structure as designed. Double probe pads for each subarray would ensure that electrical continuity is established and that a test result indicating no current leakage is the result of the oxide integrity of the subarray being tested and not probe-to-probe-pad misalignment. Use of double probe pads does increase the area required for the test structure and the time required for automatic testing.

For the present structure, however, if continuity is established at the two common probe pads, it is necessary to assume that probe-to-probe-pad continuity exists for the entire 2 by 10 probe-pad array. Each subarray is then individually tested by applying 10 V between the poly and epi contacts and measuring any detectable leakage current. Similar testing procedures are also followed to determine leakage between metal-to-poly and metal-to-epi subarrays. Also, a series of tests is performed to determine the leakage between the electrical nodes of the different subarrays. Data are recorded on a floppy disc for later evaluation.

The primary advantage of using this type of structure is that the time required to test a large number of elements is very small since large parallel arrays can be tested by one or two measurements. The structure is also useful in that it addresses primarily one type of fault.

The primary disadvantage of using this type of structure is in evaluating the test results obtained and in determining meaningful statistical results. One reason for this is that the structure cannot identify the occurrence of more than one fault in a particular subarray. However, the two major sources of difficulty are: (1) defining the magnitude of leakage current necessary to consider the subarray to have failed and (2) separating electrical interferences between adjacent subarrays occurring from the presence of unintended faults.

Test results from RFII structures on the PVW accompanying lot A6 are shown in figure 19. The yield of the structure is plotted as a function of the number of elements tested. Any array with a leakage greater than 1.0  $\mu$ A was considered to have failed.

The bands accompanying the curve are the uncertainty of the measurement introduced by interferences caused by the test structure. An example of a typical interference is the occurrence of an unintended fault causing electrical communication between two adjacent subarrays. A typical example of this type of unintended fault is a poly bridge or a metallization bridge electrically linking two subarrays. When an unintended fault is detected for a subarray pair and an intended fault is detected for that combination, an uncertainty arises as to which subarray contained the fault or if both subarrays contained a fault. The upper and lower bounds of the curves in figure 18 represent the highest yield and lowest yield, respectively, that can be determined from test results where unintended faults are present.

Lowering the leakage current failure threshold criterion greatly increases the uncertainty associated with evaluating the test results. As can be seen

in figure 20, if the failure threshold is lowered to  $10^{-4}~\mu A,$  the uncertainty bands increase.

Test results from RFII do allow for some basis of yield evaluation. If the yield *versus* number of elements, N, were extrapolated to an N of 5000 in figure 19, the resultant yield predicted would be considerably greater than the product yield measured. Given the accuracy of the test structure measurements and accompanying uncertainty, this suggests that the principal source of yield degradation is not breakdown of the dielectric layers which separate the episilicon, polysilicon, and metallization.

In order to improve the accuracy of these results, the structure should be redesigned with greater separation between subarrays. This would reduce the possibility of metal or poly bridging between subarrays. Also, the structure should be designed such that only one fault type can be detected. For instance, a structure intended to detect poly-to-epi faults should consist of poly-over-gate-oxide-over-epi layers only. The absence of metal will remove the possibility of electrical interferences by combined metal-to-epi and These steps will increase the area required for a metal-to-poly shorts. structure and eliminate the possibility of detecting metal-to-poly and metalto-epi faults. Also, the use of double probe pads for the entire structure will ensure that probe-to-probe-pad continuity is established for each subarray. To establish a more meaningful correlation between the test results from RFII and product yield, a precise estimate of the poly-to-epi leakage current required to cause circuit failure must be available. This estimate must come from circuit modeling work.

Use of random fault test structures consisting of parallel or series arrays of identical elements can be a valuable method of acquiring test results from a statistically significant data base from which yield estimates can be made. Testing time and equipment are minimal. Care must be taken in structure design and selection to ensure that:

- (a) the occurrence of unintended faults is minimized or that they can readily be identified,

- (b) well-defined failure criteria exist, and

- (c) the fault being detected represents a dominant fault mechanism occurring in the process.

#### 6. CONCLUSIONS

#### 6.1 Process Parameter Pattern

In order to be able to characterize the performance of integrated circuits, it is necessary to determine first the baseline electrical parameters of the process. The data presented show that significant variations in these parameters can occur across a wafer and from wafer lot to wafer lot. In order to obtain reasonable estimates of these parameters, it is <u>insufficient</u> merely to measure two or three test structures per wafer, as is often done, and expect an accurate result. A large sample of test sites must be available in order to make a statistically significant estimate of the desired parameter.