Computer Systems Technology

U.S. DEPARTMENT OF COMMERCE Technology Administration National Institute of Standards and Technology

# NIST Workshop on the Computer Interface to Flat Panel Displays

Editors:

Mark P. Williamson,

William E. Burr,

John W. Roberts

1994

he National Institute of Standards and Technology was established in 1988 by Congress to "assist industry in the development of technology . . . needed to improve product quality, to modernize manufacturing processes, to ensure product reliability . . . and to facilitate rapid commercialization . . . of products based on new scientific discoveries."

NIST, originally founded as the National Bureau of Standards in 1901, works to strengthen U.S. industry's competitiveness; advance science and engineering; and improve public health, safety, and the environment. One of the agency's basic functions is to develop, maintain, and retain custody of the national standards of measurement, and provide the means and methods for comparing standards used in science, engineering, manufacturing, commerce, industry, and education with the standards adopted or recognized by the Federal Government.

As an agency of the U.S. Commerce Department's Technology Administration, NIST conducts basic and applied research in the physical sciences and engineering and performs related services. The Institute does generic and precompetitive work on new and advanced technologies. NIST's research facilities are located at Gaithersburg, MD 20899, and at Boulder, CO 80303. Major technical operating units and their principal activities are listed below. For more information contact the Public Inquiries Desk, 301-975-3058.

## **Technology Services**

- Manufacturing Technology Centers Program

- Standards Services

- Technology Commercialization

- Measurement Services

- · Technology Evaluation and Assessment

- Information Services

# **Electronics and Electrical Engineering Laboratory**

- Microelectronics

- · Law Enforcement Standards

- Electricity

- Semiconductor Electronics

- Electromagnetic Fields<sup>1</sup>

- Electromagnetic Technology<sup>1</sup>

# Chemical Science and Technology Laboratory

- Biotechnology

- Chemical Engineering<sup>1</sup>

- · Chemical Kinetics and Thermodynamics

- Inorganic Analytical Research

- Organic Analytical Research

- Process Measurements

- Surface and Microanalysis Science

- Thermophysics<sup>2</sup>

## **Physics Laboratory**

- Electron and Optical Physics

- Atomic Physics

- · Molecular Physics

- Radiometric Physics

- · Quantum Metrology

- Ionizing Radiation

- Time and Frequency<sup>1</sup>

- Quantum Physics<sup>1</sup>

## Manufacturing Engineering Laboratory

- Precision Engineering

- Automated Production Technology

- Robot Systems

- Factory Automation

- Fabrication Technology

# Materials Science and Engineering Laboratory

- Intelligent Processing of Materials

- Ceramics

- Materials Reliability<sup>1</sup>

- Polymers

- Metallurgy

- Reactor Radiation

# **Building and Fire Research Laboratory**

- Structures

- Building Materials

- Building Environment

- Fire Science and Engineering

- Fire Measurement and Research

# **Computer Systems Laboratory**

- Information Systems Engineering

- Systems and Software Technology

- Computer Security

- Systems and Network Architecture

- Advanced Systems

# Computing and Applied Mathematics Laboratory

- Applied and Computational Mathematics<sup>2</sup>

- Statistical Engineering<sup>2</sup>

- Scientific Computing Environments<sup>2</sup>

- Computer Services<sup>2</sup>

- Computer Systems and Communications<sup>2</sup>

- Information Systems

<sup>&</sup>lt;sup>1</sup>At Boulder, CO 80303.

<sup>&</sup>lt;sup>2</sup>Some elements at Boulder, CO 80303.

# NIST Workshop on the Computer Interface to Flat Panel Displays

January 13–14, 1994; San Jose Hilton and Towers; San Jose, California

Editors:

Mark P. Williamson, William E. Burr, John W. Roberts

Advanced Systems Division Computer Systems Laboratory National Institute of Standards and Technology Gaithersburg, MD 20899-0001

August 1994

U.S. Department of Commerce Ronald H. Brown, Secretary

**Technology Administration**Mary L. Good, Under Secretary for Technology

National Institute of Standards and Technology Arati Prabhakar, Director

## **Reports on Computer Systems Technology**

The National Institute of Standards and Technology (NIST) has a unique responsibility for computer systems technology within the Federal government. NIST's Computer Systems Laboratory (CSL) develops standards and guidelines, provides technical assistance, and conducts research for computers and related telecommunications systems to achieve more effective utilization of Federal information technology resources. CSL's responsibilities include development of technical, management, physical, and administrative standards and guidelines for the cost-effective security and privacy of sensitive unclassified information processed in Federal computers. CSL assists agencies in developing security plans and in improving computer security awareness training. This Special Publication 500 series reports CSL research and guidelines to Federal agencies as well as to organizations in industry, government, and academia.

National Institute of Standards and Technology Special Publication 500-219

Natl. Inst. Stand. Technol. Spec. Publ. 500-219, 227 pages (Aug. 1994)

CODEN: NSPUE2

U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1994

## Disclaimer

The views expressed by the participants of this workshop are the opinions of the individuals. Their views do not reflect NIST policy or agreement. Proprietary names and model numbers are cited solely for clarity and do not imply a recommendation or criticism

# Acknowledgments

Special thanks are due to all the participants of the workshop. NIST greatly appreciates the time, guidance, and assistance provided by Dr. David Lee of Xerox PARC, Mr. Scott Vouri of Binar Graphics, Mr. Mark Singer of Cirrus Logic, Dr. Paul Alt of IBM Corporation, Mr. Thomas Credelle of Apple Computer, and Mr. Anders Frisk of ICL Personal Systems.

# Contents

| Α.  | Preface                                                                                                                     |

|-----|-----------------------------------------------------------------------------------------------------------------------------|

| В.  | Summary                                                                                                                     |

| C.  | Minutes                                                                                                                     |

| 1.  | Workshop Agenda                                                                                                             |

| 2.  | List of Attendees                                                                                                           |

| 3.  | Opening Remarks Mark P. Williamson, NIST                                                                                    |

| 4.  | NIST's Advanced Technology Program Mr. Thomas Leedy, NIST                                                                   |

| 5.  | Issues in Interfacing Flat-panel Active Matrix TFT LCDs Dr. Victor Da Costa, Xerox PARC                                     |

| 6.  | High Performance, Cost-Effective Computer and Video Interfacing to Megapixel AC-PDP Ms. Carol A. Wedding, Photonics Systems |

| 7.  | Sun's Proposal for a Unified Display Interface Mr. Marc Klingelhofer, Sun Microsystems                                      |

| 8.  | I/O Connectors for Video Applications, History, Requirements, and Technology to Meet those Needs                            |

|     | Mr. Gary Manchester, MOLEX, Inc.                                                                                            |

| 9.  | Issues in FPD Interfaces for PC and Workstation Use Mr. Bob Myers, Hewlett-Packard Co.                                      |

| 10. | United States Display Consortium Dr. Bob Pinnel, USDC                                                                       |

| 11. | Issues Related to Interfacing Flat Panel Displays Ms. Jill Seman, Chips and Technologies                                    |

| 12. | High Resolution Color LCD Interface Issues Mr. Sunder Velamuri, Cirrus Logic, Inc.                                          |

| 13. | The Voluntary Standards Process Mr. William Burr, NIST                                                                      |

| 14. | Electronic Industries Association (EIA) Mr. Thomas Mock, EIA                                                                |

|     |                                                                                                                             |

Video Electronics Standards Association (VESA)

Mr. Scott Vouri, Binar Graphics, Inc.

15.

## A. Preface

Television, computers, and telecommunications have been considered largely separate technologies. Today, they are merging to provide a powerful tool for the information age. This merger will provide new capabilities for diverse applications in education, engineering, manufacturing, robotics, entertainment, medicine, defense, security, transportation, business, and government.

Cathode ray tubes (CRTs) are used in current television sets and in most personal computers. They produce light by scanning an electron beam (the "cathode ray") across a phosphor screen to stimulate the emission of light. CRTs have high brightness, good color reproduction, and reasonably wide viewing angles. However, since CRTs are evacuated devices, they must be made from strong materials to withstand the pressure of the atmosphere. The tubes become increasingly difficult to implement in large screen sizes.

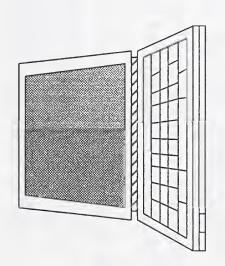

In contrast, emerging flat panel displays (FPDs) are considerably smaller and lighter for a given screen size. FPDs are being integrated into laptop, notebook, and hand-held form factors. In addition, flat panel monitors are becoming commercially available for desktop computers and workstations.

However, FPDs are currently a value added product which requires the development of a unique computer interface for each display. This results in needless expense and integration difficulties for the end-user. In addition, the lack of standards may slow down the implementation of FPD technologies in the market place.

In order to achieve interoperability and flexibility comparable to CRTs, it is necessary to develop logical, electrical, and mechanical standards for the computer interface to FPDs. Further, the wide variety of FPD technologies may require either an advanced computer interface architecture to accommodate the varying requirements of different displays, or a series of standards that address the requirements of different technologies.

FPD technologies have reached a point where it is worthwhile to consider the development of voluntary industry standards for the computer interface. Therefore, the Computer Systems Laboratory (CSL) at NIST sponsored this workshop to bring together flat panel display manufacturers, computer systems manufacturers, graphic controller chip manufacturers, industry and government users, and others who have a material interest.

## B. Summary

On January 13 & 14, 1994, the NIST Workshop on the Computer Interface to Flat Panel Displays was held at the San Jose Hilton and Towers in San Jose, California. The meeting was attended by approximately 55 people from over 40 computer, flat panel display, and graphics controller companies. Representatives from the civilian and military sides of the government were also present.

The objectives of this workshop were: to determine the need for a standard or a series of standards for the computer interface to flat panel displays (FPDs); to identify what types of standards are needed; to identify approaches for developing FPD interface standards; and to obtain a consensus on a coordinated plan for standards development.

The workshop attendees agreed that a standard flat panel display interface for integrated devices is needed. Furthermore, the workshop attendees agreed that efforts should be made to encourage all of the flat panel display manufacturers to participate in these standards activities.

The consensus reached at this workshop resulted in the following action items:

- 1) Form a Video Electronics Standards Association Special Interest Group (VESA SIG) to undertake the development of a standard or a series of standards for the interface between a FPD and its controller. This interface standard will address both active and passive FPDs in integrated devices. It will cover both the electrical and the mechanical (connector) specifications. An organizational meeting will be held on February 9, 1994, at the VESA headquarters with the intention of having a proposal ready to discuss with manufacturers of flat panel displays at the Society for Information Display (SID) meeting in June.

- 2) NIST will seek to inform all materially interested parties, especially the flat panel display manufacturers of the standards plans, and encourage their participation.

- 3) VESA will distribute the February 9, 1994, meeting announcement and agenda.

- 4) The interface for remote FPDs requires additional technical discussions before a standard can be written. Additional workshops on display interfaces and /or technical sessions at the SID Symposium should be explored. In addition, the VESA Monitor Committee invited interested parties to participate in their committee which will be considering interfaces and connectors to desktop and remote FPDs in addition to their cathode ray tube (CRT) interface work.

Dr. Paul Alt of IBM will seek to set up a technical session at future SID meetings to consider these long-term display interface requirements. It is too late to add a technical session on interface topics at SID '94. However, an interface session may be possible for SID '95.

#### C. Minutes

The Workshop began at 12:30 PM on January 13, 1994 at the San Jose Hilton and Towers and continued until 4:00 PM on January 14. The agenda for the Workshop is section (1) and the list of attendees is section (2). Mark Williamson of NIST acted as chairman of the workshop and Bill Burr of NIST was secretary.

Mark Williamson of NIST opened the workshop by introducing the NIST participants and stated the objectives of the workshop:

- Determine the need for a standard or a series of standards for the computer interface to flat panel displays (FPDs).

- Identify what types of flat panel standards are needed.

- Identify approaches for developing FPD standards.

- Obtain a consensus on a coordinated plan for standards development.

Mark Williamson's presentation is section (3).

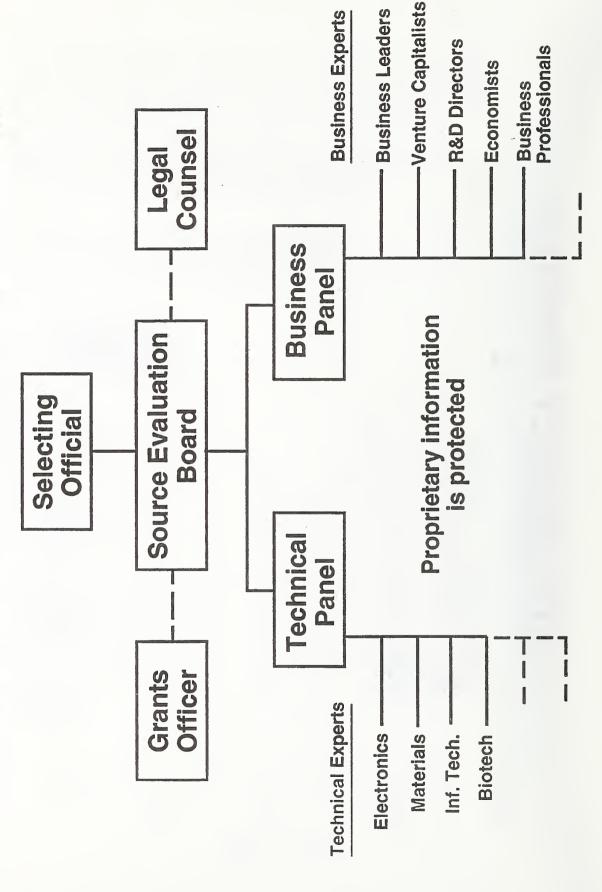

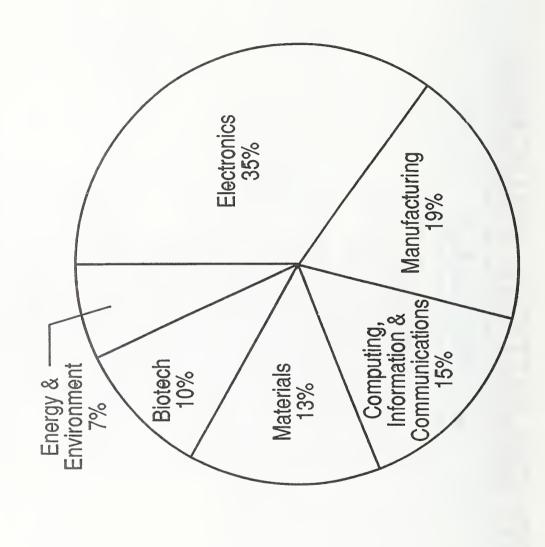

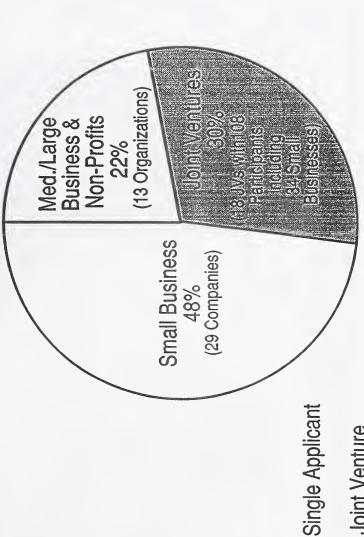

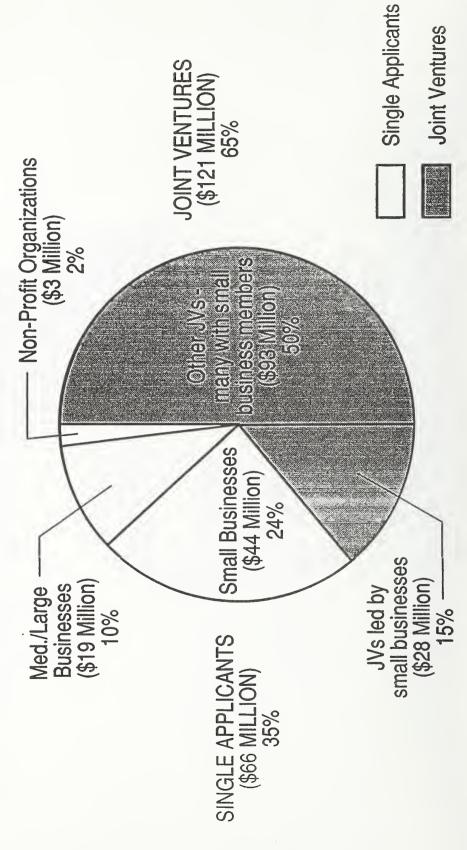

Mr. Thomas Leedy of NIST made a presentation on the NIST Advanced Technology Program (ATP). Mr. Leedy's presentation is section (4). The NIST ATP works with industry to co-fund high-risk technology development programs. Enabling, high-value technologies that promise large or strategic long term benefits to the U.S. economy are emphasized. ATP awards are based on a competition of both the technical and business merit of the proposals. Cost sharing is required: single company awards are limited to \$2M over three years and the government does not pay overhead, while joint ventures (involving at least two companies) may take up to 5 years, and there is no limit on the award, however the ATP funding is limited to less than 50% of the total cost. The ATP has made several awards in the general area of flat panel technology; these are summarized in section (4). In response to a question, Mr. Leedy stated that any firm that is not a "United States-owned company" (i.e., that does not have a majority ownership or control by individuals who are citizens of the United States) may receive an ATP grant if the Secretary of Commerce finds that the company's participation in the Advanced Technology Program would be in the economic interest of the United States, and the Secretary finds that the country in which the company or its parent company is incorporated affords United States-owned companies similar opportunities and adequate and effective protection for intellectual property rights. Further details on these eligibility requirements for foreign-owned corporations are available from the ATP.

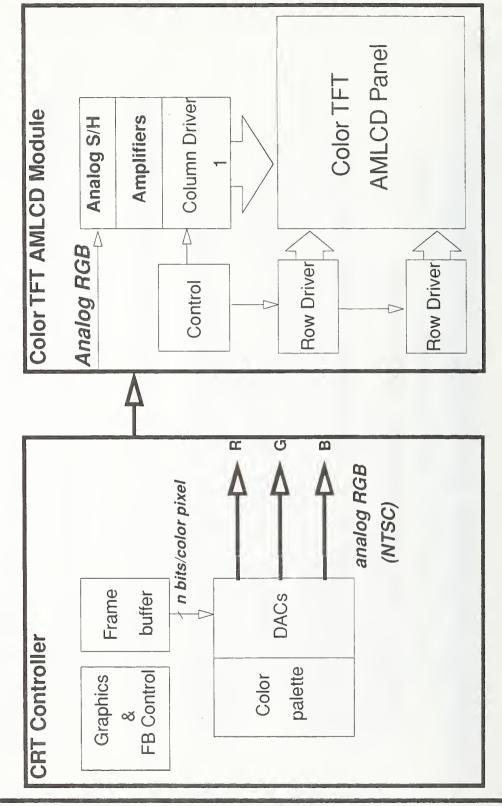

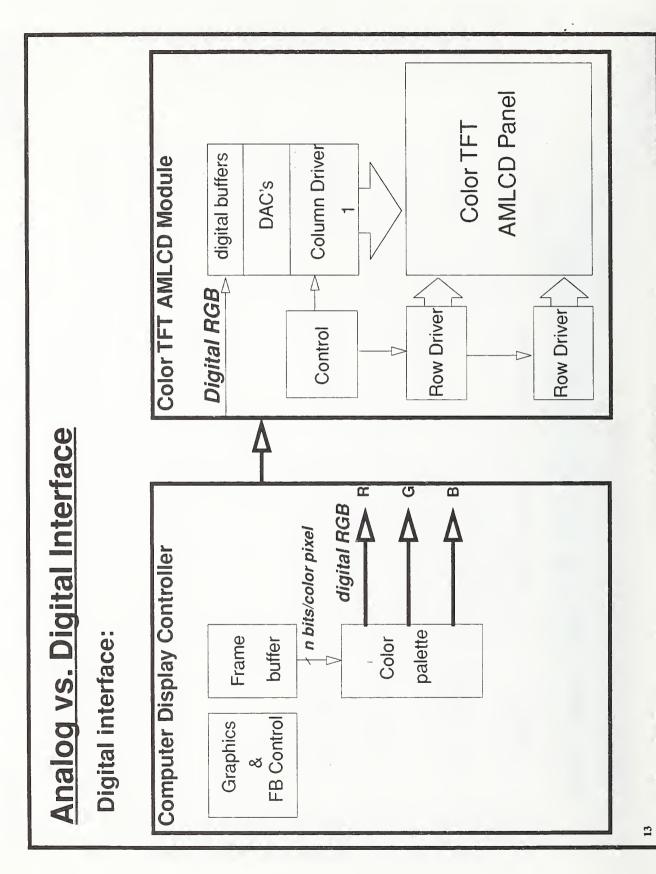

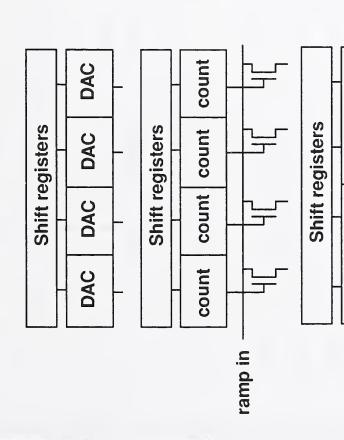

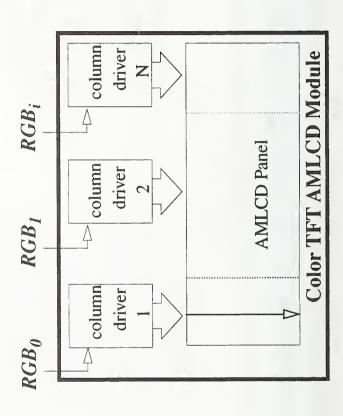

Dr. Victor DaCosta of Xerox Palo Alto Research Center (PARC) presented a discussion of the issues involved in interfacing active matrix FPDs. Dr. DaCosta's presentation is section (5). Dr. DaCosta pointed out two themes that other speakers were to return to:

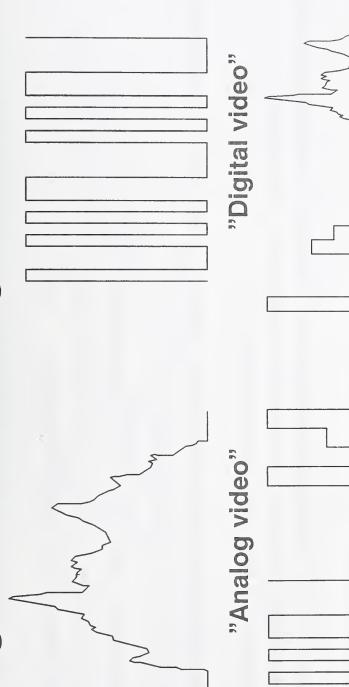

- The cathode ray tubes (CRTs) which have predominated as display devices are strict left to right, top to bottom raster scan devices, while active matrix liquid crystal displays (AMLCDs), like most other flat panel technologies, are row and column oriented. Thus the timing and ordering of signals on CRT oriented interfaces are not well suited for flat panel displays;

- There is no standard interface to the flat panel, and the characteristics of FPDs vary, so each panel requires a highly optimized and customized display adapter in the host computer to handle the specific characteristics of the particular FPD.

Dr. DaCosta identified four issues and problems in driving high resolution AMLCDs:

- Analog vs. digital interface;

- An inherent speed mismatch between the frame buffer output and the panel driver integrated circuit (IC) input;

- Different color filter mosaics;

- Different color/gray level control and correction schemes.

Dr. DaCosta stated that a flat panel interface standard is needed to provide a flexible and consistent interface to a wide range of FPD devices. He further proposed that this could be accomplished by incorporating within the panel electronics a flat panel controller IC that provides a simple and standardized interface to the flat panel by performing all the specific display dependent processing needed for the row and column drivers of the flat panel. That is, the customization should occur in the panel itself, so that there can be a consistent interface. Dr. DaCosta stated that an example of such an AMLCD flat panel controller had been developed by Xerox PARC and would be presented at the ISSC94 conference.

Ms. Carol Wedding of Photonics Systems made a presentation on the interface issues for alternating current plasma display panels (AC-PDPs). Her presentation is section (6). Ms. Wedding began by discussing the requirements for future FPDs. She noted that displays must keep pace with computers and said that displays of at least 1280 by 1024 pixels with at least 256 colors will be required for some applications. She noted that it is basically a CRT-oriented world, and that CRTs generally use an analog raster scan Red, Green, Blue (RGB) interface. All (or at least most) flat panel technologies must interface a digital panel to an analog signal or develop a special card to interface between the host and flat panel display. Photonics has pursued both paths. She summarized the following advantages and disadvantages of analog interfaces:

#### Advantages:

- Nearly universally available;

- Remote displays practical;

- Noise resistant.

#### Disadvantages:

- Added cost of digital in controller to analog in interface to digital in display;

- Cost of phase lock of different clock frequencies in display;

- Bandwidth degradation.

Ms. Wedding noted that a partial solution to the problems with analog interfaces would be to include a dot clock with the RGB signal in the interface, eliminating the need for a phase locked loop (PLL) in the display to recover the clock. She then summarized the advantages and disadvantages of digital display interfaces:

## Advantages:

- Eliminate cost of digital-to-analog (A/D), analog-to-digital (D/A) conversion;

- Eliminate cost of PLL clock recovery;

- Reduce clock jitter.

#### Disadvantages:

- Not presently universal;

- Not noise resistant (or requires a large data bus);

- Very high data rate for 60 Hz or higher frame rate and high resolution displays.

Ms Wedding proposed two possible solutions to the problems with digital display interfaces at high resolutions and frame rates:

- Use an emmiter-coupled logic (ECL) twisted pair interface for its better high frequency electrical characteristics;

- Embed the computer itself on the back of a high resolution FPD.

While Ms. Wedding's talk was concerned primarily with plasma displays, she stated that all FPDs use row and column drivers and load data in column form. She described displays that load gray levels one at a time. However, other participants pointed out that liquid crystal displays (LCD) do not necessarily use gray levels one at a time. Ms. Wedding postulated that a "dream interface" for flat panels, or at least AC-PDPs, would be digital and organized in a row and column architecture, with gray level data processed in separate subplanes. She concluded that by exploiting the similarities of FPDs and discarding the preconceived notion of a CRT interface it should be possible to define a flat panel interface that is cost effective and technically acceptable to a wide variety of flat panel technologies.

Mr. Marc Klingelhofer of Sun Microsystems gave a presentation from the perspective of a workstation vendor. His slides are section (7). Mr. Klingelhofer began by describing the CRT interfaces used with workstations, where unlike the personal computer (PC) market (where the Video Graphics Adapter, VGA, standard provides some order), there is great variation. Workstation CRT interfaces are predominantly analog RGB over coax

with BNC connectors. Various synchronization styles are employed, including Horizontal/Vertical drive or composite synchronization, which may be embedded in the green signal or a separate signal. A plethora of horizontal and vertical resolutions and blanking characteristics are employed. All CRT interfaces, however, scan pixel-by-pixel horizontally, line-by-line vertically.

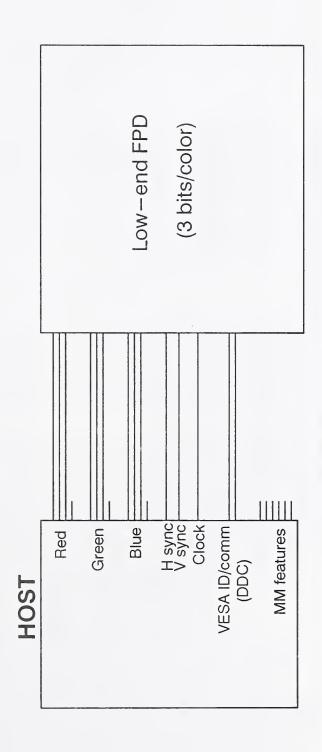

Mr. Klingelhofer went on to describe flat panel and particularly LCD interfaces. LCDs use bit parallel RGB plus clock and control over ribbon cables. Pixel depths per primary color are typically 6 to 8 bits per primary color. Various synchronization and control modes are employed and there are numerous resolutions. They rasterized first in columns then in horizontal rows. He noted that other FPD technologies are even less standardized than LCDs. Mr. Klingelhofer noted the following shortcomings of FPD interfaces:

- The pixel depth is not standardized typically 6 to 8 bits;

- Pixel interleaving, if present, is display dependent;

- The cables must be short (certainly less than 10 m) and bulky, with 40 to 80 signals;

- Clock and control functions are not standardized;

- The row and column rasterization is incompatible with CRTs and most display drivers.

Mr. Klingelhofer also noted the similarities between FPDs and CRTs:

- Both use RGB pixels of 6 to 8 bits per primary;

- Both are two dimensional with a row and column matrix, and each pixel has an "address;"

- Sequences of lines constitute frames, and the frames can be identified.

Mr. Klingelhofer noted an industry trend to high bandwidth digital serial networks, smart displays, self identifying data streams, and scalability so that feature and performance enhancement are easy. He therefore proposed a relatively high level approach to a "unified display interface" that would use serial network technology and could support various display devices, including CRTs and LCDs. He proposed a serial interface, rather than a parallel ribbon cable, that could be scaleable, supporting various display types and resolutions, and be automatically configurable. The physical interface would include standardized copper or optical fiber media, with a fixed low level protocol for clock and bit serialization. The benefits would include common interface circuits, as well as standard connectors and cables, resulting in high volumes and low costs for these components. Moreover, very sophisticated display drivers then could support any standard display type and resolution without cabling or synchronization concerns.

He proposed that there be a standardized sequencing of color information ordering with pixels sent row by row rather than column by column and with fixed headers to identify resolutions and pixel positions. A low-end version of the protocol would be comparable to analog RGB, with pixels sent line-by-line; in this case the display would lock into and

accept incoming data with no handshaking or feedback. A higher level standard protocol would allow the driver to sense the display characteristics and allow the driver to set the resolution according to the application as well as allow the driver to alter display characteristics such as brightness and contrast.

Mr. Klingelhofer concluded by raising two open issues:

- Should such an interface directly support 3-D images rather than only 2-D? Present displays are 2-D and deal with 3-D by showing the projection of a 3-D image on a plane, but perhaps future displays may be 3-D displays;

- Are 8 bits per primary color per pixel enough?

A brief discussion followed Mr. Klingelhofer's talk. Two subjects were discussed: compression and cost. Should such an interface carry compressed data? If so, would the interface include a protocol like an X-terminal? Mr. Klingelhofer was asked what proportion of the cost of the display would be the embedded electronics needed for such an interface. Mr. Klingelhofer responded ,"a lot." Sun is apparently developing such a serial display interface, and may be able to discuss the subject in more detail in the future.

Mr. Gary Manchester of Molex gave a presentation on the future requirements for input/output (I/O) connectors in video applications. Mr. Manchester's presentation is section (8). He began by summarizing the history of video I/O connectors and the D subminiature connector commonly used by the VGA and extended graphics adapter (XGA) standards with CRT displays. In limited markets (e.g., workstations) where performance is an issue, designers have used standard coax systems. Current trends are requirements for smaller connectors with more contacts, low insertion force and yet increased life, perhaps as many as 10000 insertions. High volume consumer markets are developing, so cost becomes a major factor.

Mr. Manchester believes there is a need for a mixed layout connector supporting both coax and unshielded lines in one connector, as well as possibly power lines. The connector must be suitable for low cost manufacturing. Molex is now capable of providing a connector with three or four 75  $\Omega$  coax lines as well as 50 additional signal lines in the same space as a 15 pin VGA connector. With such a connector Mr. Manchester believes that it will be possible to package RGB video coax plus a fourth coax high speed sync line, mouse I/O, battery charger lines, serial port lines, keyboard lines, phone lines, parallel port lines, pen I/O, audio I/O, and a network interface all in one connector at a cost per mated line comparable to currently available I/O connectors.

Standardized connectors are required for such applications since the cost of connectors is very strongly a function of production volume. A standard will also promote the atmosphere to development of suitable connector technologies.

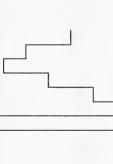

Mr. Bob Myers of Hewlett Packard gave a talk on issues in FPD interfaces of PCs and workstations. His presentation is section (9). Mr. Myers identified a distinction that previous talks had hinted at and that was later amplified on: there are really two FPD applications with potentially two interface standards. Those applications are FPDs in portable computers or other computers that include the display integrated in the same physical package as the video controller, and separate standalone monitor FPDs that may be some distance from the computer. The integrated FPD-video controller interface requires a very short, direct connection and consequently has less concern with Electromagnetic Interference (EMI) issues. The separate monitor interface must support a display removed from the controller by at least 1 m, and preferably should support longer distances. The interconnect EMI performance and signal integrity are therefore a much greater concern. At least the monitor interface must support both FPDs of various technologies and CRTs as well. The current analog video standard is a poor solution for both CRT and FPD monitors. Moreover, High Definition Television (HDTV) will make the standalone monitor FPD a big concern.

Mr. Myers discussed the bandwidth required for high resolution monitors with up to 60 frames per second. HDTV format displays and high resolution workstation displays will require pixel rates on the order of 60 to 130 MHz for flat panels and 160 MHz to more than 200 MHz for CRTs. At 24 bits per pixel that translates to data rates of 180 to 390 Mbytes/s for FPDs and 480 to 600 Mbytes/s for CRTs. Mr. Myers pointed out that as high as these rates are, multilevel coding can reduce the bandwidth needed for "digital" transmission.

Mr. Myers stated that a successful interface must be cost-competitive while allowing compliance with EMI requirements and providing for additional needed features (e.g., display ID, human I/O device connectivity). A successful interface must work within the constraints of existing technologies yet be flexible enough to support different display technologies and formats, including flat panels and CRTs. Mr. Myers said that computer manufacturers cannot afford separate interfaces for both CRTs and flat panels and CRTs will dominate in monitor applications for the foreseeable future.

Although he did not characterize it as a proposal, Mr. Myers outlined his thoughts on a possible common interface. It would have 4 signal lines per color, one of which is capable of analog video or of a binary or a quaternary digital signal, with three other lines capable of four level digital signals. The 12 lines could then provide analog video for CRTs, 4-bit color for simple digital FPDs, or 8 bits per subpixel digital color for high quality FPDs (in this mode all four lines are quaternary). The interface would also include horizontal and vertical sync as well as lines for an identification (ID) standard and probably human I/O and analog audio. The total would be 20 to 24 signal lines plus ground. Each display type would connect only to those outputs it needed, and provide an ID capability to allow the host to configure to the display's needs.

Mr. Myers was questioned about the cost of the multilevel drivers in the host. He felt that the cost would not be great in quantity very large scale integration (VLSI), and observed that every host might not support all features.

Dr. Bill Hale of Wright-Patterson Air Force Base discussed the need for plug and play displays in flight instruments systems and the difficulty commercial display vendors have in doing business with DOD. The greatest opportunities are probably in transport aircraft. Vendors wanting more information on the Air Force needs can call Dr. Hale at (513) 255-8261.

The first day concluded with a question and answer session for the speakers. Mr. Klingelhofer was asked just how much of network protocols he proposed to adopt for displays: just the physical layer or entire packet structures such as Asynchronous Transfer Mode (ATM) frames? He said that Sun is working on such an interface and that there might be a more concrete proposal in the future.

There was a discussion of parallel versus serial interfaces and the needs for relatively long (i.e., 100 m) distances between hosts and displays. What are the applications for such distances? One apparently is parallel processors supporting many users. It was observed that the X-terminal provides a partial solution for the remote intelligent display application.

There was a discussion of costs. An interface standard between the graphics controller and flat panel will add hardware costs to systems. However, there is a considerable cost in the ad hoc engineering required to adapt specific panels with nonstandard interfaces to systems. A part of that cost is not so much monetary as in time to market.

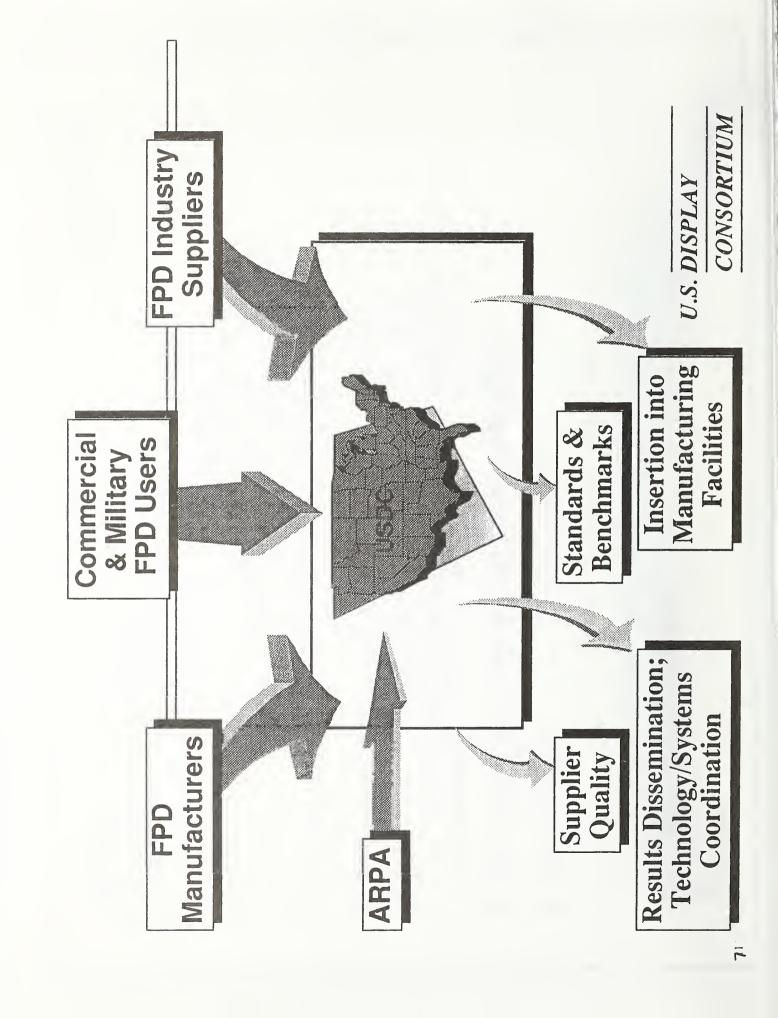

Dr. Bob Pinnel opened the second day of the workshop with a talk on the United States Display Consortium (USDC). Dr. Pinnel's visuals are section (10). The USDC is supported by Advanced Research Projects Agency (ARPA) and based on the premise that the United States must become a leading player in the manufacturing of FPDs to be competitive in future computer and electronic products markets. Manufacturers, suppliers, users and government must cooperate for this to happen. The USDC focuses on developing the U.S. flat panel display infrastructure, particularly the needed manufacturing and equipment expertise. The USDC is an industry-led public/private partnership and a nonprofit, non-manufacturing organization that provides a common platform for FPD manufacturers, developers, their supplier base, and users to develop plans and specifications for next-generation FPD manufacturing equipment and materials.

The USDC focus is on the needs of the wide range of FPD technologies. The USDC follows a vertically integrated approach to include all elements of the FPD food chain from equipment and materials suppliers to systems integrators. Nine Requests for Proposals have been issued, and the first selected involves equipment to do on-axis optoelectrical inspection of assembled FPD cells before attachment of the drive electronics.

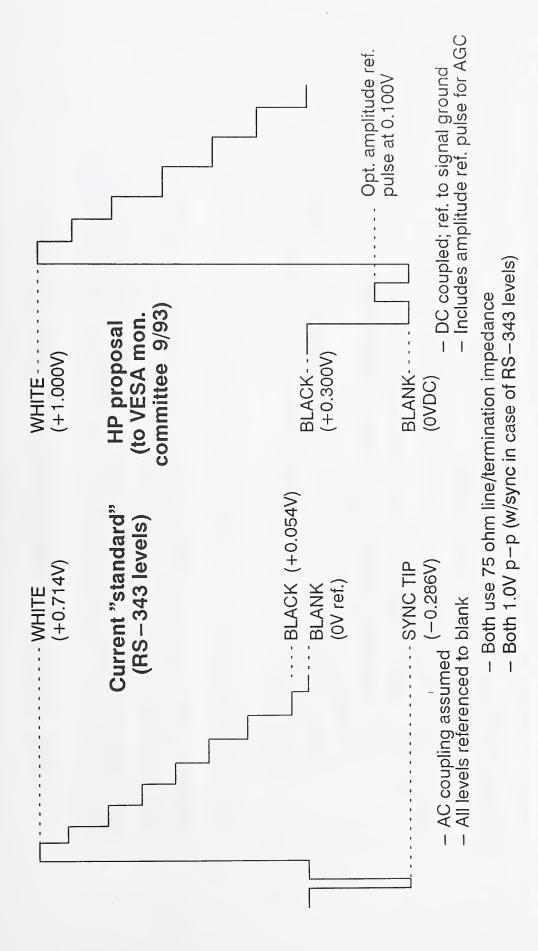

Ms. Jill Seman of Chips and Technologies provided a very informative perspective on the interfaces used in flat panels for PCs. Her presentation is section (11). The VGA resolution of 640x480 is common in FPDs for PCs. Several kinds of displays are used, including dual scan monochrome LCDs, dual scan color passive matrix LCDs, color thin film transistor (TFT) and monochrome plasma and electroluminescent (EL) displays. These differ in the panel characteristics: different interfaces and various problems occur due to the lack of standardization.

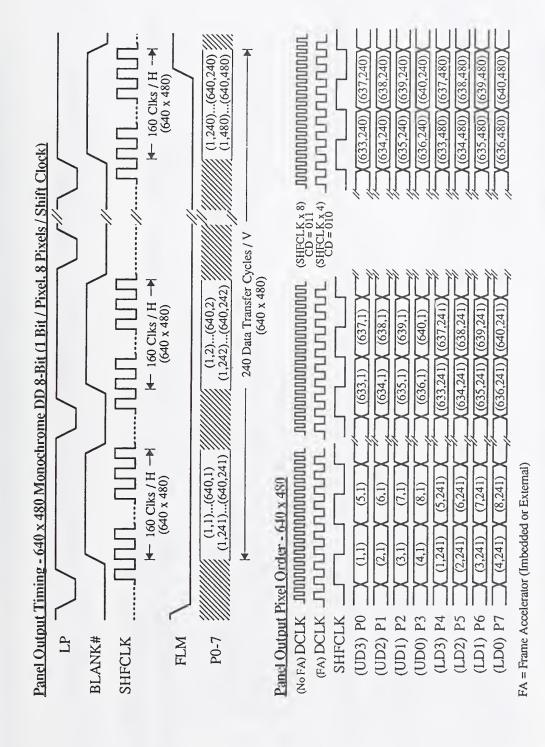

Monochrome dual scan FPDs are the most prevalent displays in the PC market. They use a dual drive scanning scheme that requires data from two separate controller memory locations at the same time. Typically they have 8 data lines for 8 pixels per clock and 3 control signals: horizontal sync (LP), vertical sync (FLM) and Shift Clock (SHFCLK). Two power supply voltages are required. Panel interfaces differ by manufacturer and product. Even products from the same manufacturer and product line may differ. There is no standard cabling scheme and different panels have different connectors and pinouts. There is no standard labeling scheme and LCD voltages differ from panel to panel. There is no standard panel sequencing method and both horizontal and vertical timing differ for every panel.

Color dual scan LCD panels are most prevalent in the mid-range notebook PC market. They also use a dual drive scheme with LP, FLM and SHFCLK control signals. They have 8 or 16 data lines with 2 2/3 or 5 1/3 subpixels per clock, and require two power supply voltages. Interfaces are not standard and have all the same variations as the monochrome LCD displays. In addition clock divide schemes vary from panel to panel.

Color TFT panels are most prevalent in the high-end notebook PC market. They use a single panel, single drive scheme that requires data from one memory location at a time. Four control signals, Horizontal sync (HSYNC), vertical sync (VSYNC), SHFCLK and BLANK are normally used. HSYNC, VSYNC and BLANK timings are similar to a CRT. There may be 9, 12, 18 or 24 data lines with one pixel per clock. Again, two power supply voltages are required. Sharp is the dominant supplier of TFT panels and its interface is something of a de facto standard. However there are no standard cabling schemes, connectors or pinouts, and LCD voltages differ from panel to panel.

Monochrome plasma and EL panel screens are most common in embedded instruments. These are single panels with a single drive scheme. Four control signals, HSYNC, VSYNC, SHFCLK and BLANK are used with 8 data lines and 1, 2, 4 or 8 pixels per clock. Two different power supplies are used. Panel interfaces vary by manufacturer and product, with no standard cabling, connectors or pinouts. Bias voltages vary from panel to panel. There is no standard power sequencing method. Clock divide-by schemes vary and HSYNC and VSYNC timing vary from panel to panel.

Ms. Seman pointed out several challenges for present PC flat panel interfaces. There are both dual and single drive formats, as well as color and monochrome screens with various data formats. Control signals must be programmable, with independent generation of LP,

FLM, SHFCLK and BLANK signals, several divide schemes and different panel power sequencing. Variable voltage supplies are required for different panels. The challenge to controller vendors is how to support multiple panels with one controller design.

Ms. Seman was asked if the variation was product by product or by product line. Ms Seman replied that it is primarily by product line. Mr. Kevin Warren of IBM commented that the details generally don't have to do with the display technology. Rather, there are two reasons for the variations:

- To simplify the displays;

- Customers ask for them.

Ms. Seman was asked whether a standardized interface would make cheaper systems. Ms. Seman replied that a standardized interface would make things a lot easier to understand but would not necessarily result in less expensive controllers. Tim Kriegel of Hewlett Packard expressed the view that the big payoff to a flat panel interface standard would be in reducing the time to market for new products.

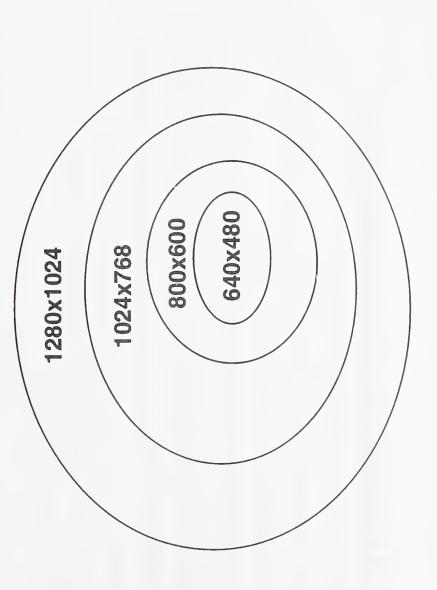

Mr. Sunder Velamuri of Cirrus Logic made a presentation on high resolution color LCD interface issues. His presentation is section (12). Mr. Velamuri pointed out that expanding applications are going to require much higher resolution displays than the currently common 640x480 VGA displays. He expressed the view that a standard would concentrate on active matrix displays, since the passive matrix market is relatively mature and is a "minefield" of idiosyncrasies. He sees three distinct market segments for color TFT LCDs:

- Personal Digital Assistants (PDAs) with resolutions of 640x480 or 320x240 and less than 8" diagonals;

- Notebook computers with resolutions of 800x600 or 640x480 and a 256k color palette;

- Monitors and workstation laptops with resolutions of 1280x1024 or 1024x768 and a 16.7M color palette.

Key issues for high resolution TFT LCDs include color uniformity and consistency, a color matching capability and the ability to have RGB color correction. In addition, the module form factor (thickness, weight and display area), power consumption, refresh rates, and cost are also key issues. A panel interface standard must have:

- Minimal EMI generation;

- A minimum number of data lines;

- Upward/downward expandability,

- Minimal power dissipation, the ability to drive cables of lengths greater than 3 feet;

- Appropriate hooks for multimedia;

- Expandability (i.e., 640x480, 800x600, 1024x768, 1280 x 1024, etc.).

Multimedia must be supported, including full motion video and existing video standards. The bezel width must be minimal to have a large screen and the cost impact of this cannot be large.

Mr. Velamuri outlined several interface options:

- A CRT-like panel interface with analog RGB, HSYNC and VSYNC. Gamma correction would be in the analog domain and display quality optimization would require multiple external devices to condition devices to provide opposite output voltage polarities on adjacent pixels. Among the disadvantages to this approach are the need for a high frequency PLL to recover the dot clock, cost and power dissipation and the number of ICs required;

- An analog interface that includes the dot clock. High speed A/D converters would be used to convert data to the digital domain and gamma correction would be performed with a control application specific integrated circuit (ASIC) using look-up tables. Data would then be converted back into the analog domain with high speed D/A converters. A data inverting circuit would be used to optimize display quality. Again, disadvantages would include the number of ICs and board space as well as the high cost and power consumption;

- A digital interface that is an extension of existing interfaces. It would consist of 24 data lines for one pixel per clock plus HSYNC, VSYNC, data clock (DCLK) and data enable (DE), and would have an existing base of controllers that could support this interface. Digital logic is moving from 5 V levels to 3.3 V levels. The disadvantage of this kind of digital interface would be either high frequency (to reduce the data lines) or a large number of data lines to allow lower operating frequencies.

Whatever the interface, Mr. Velamuri said that it must satisfy several compatibility requirements. First, it must be compatible with the Video Electronics Standards Association (VESA) monitor timing and 60Hz, 72 Hz and 75 Hz frame rates. Second, it must allow software driver compatibility for different resolutions and frame rates.

Mr. Velamuri was asked whether the panel standard should be strictly compatible with CRT timings. His answer was that the CRT blanking imposes too big a penalty on flat panels. Rather, it is software driver compatibility that must be achieved.

Mr. Velamuri was asked which of the alternatives he had outlined was his choice. He preferred the extension of the parallel digital interface, however he had no solution to offer to the problem of very wide buses. He felt that the multilevel logic proposal was interesting but he had many questions about it.

Mr. Velamuri was asked what additional considerations for multimedia are required. His reply was that there are two approaches: (1) concentrate the hardware in the panel, or (2)

perform the function in the controller and send it over the regular interface. Mr. Velamuri thinks that it is better to do it in the controller. When asked why not then just embed the controller in the display, Mr. Velamuri replied that it is better not to embed the controller in the display because controllers change more rapidly than panel designs.

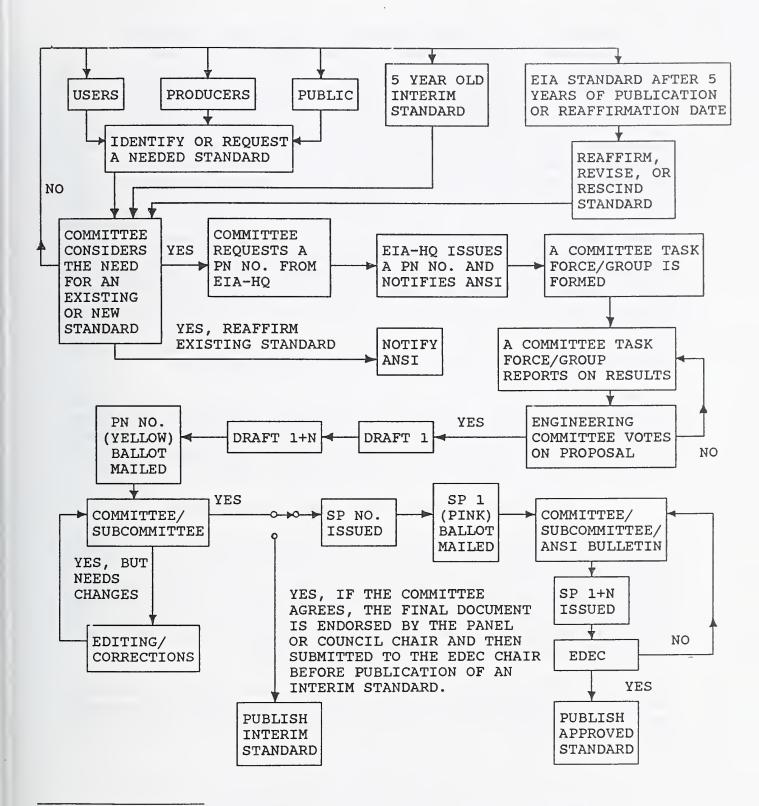

Mr. Bill Burr, of NIST, made a presentation on the voluntary standards process. His presentation is section (13). By "voluntary standards" Mr. Burr means the published standards worked out in rather formal recognized or "accredited" standards processes. The American National Standards Institute (ANSI) is the preeminent U.S. voluntary standards organization. ANSI does not develop standards, instead it "accredits" the processes of organizations that do. ANSI is also the U.S. member of the International Standards Organization (ISO) and the International Electrotechnical Commission (IEC). Joint Technical Committee 1 (JTC1) of the ISO and IEC are the recognized international standards organizations for information technology. Mr. Burr stated that ANSI accredited procedures for developing standards are meant to ensure fairness and consensus and to reduce the risks of antitrust actions resulting from standards activities. The price for this deliberate procedure is that it takes time, and time is often what is most critical in the computer industry. Mr. Burr outlines several ways that standards originally drafted in less formal, and perhaps quicker acting, industry groups might eventually be recognized as ANSI or ISO/IEC standards.

Mr. Thomas Mock described the Electronic Industries Association (EIA) standardization process. His presentation is section (14). He stressed that the EIA is in the business of establishing information technology standards. The EIA has an extensive program in consumer electronics and audio and video standards, and its sister organization, the Telecommunications Industry Association (TIA) has one in communications-oriented standards. With the apparent fusion of the traditional computer, communications and consumer electronics industries the EIA is a key player in the information technology voluntary standards arena. The EIA (and its sister organization the TIA) are accredited by ANSI and many of the standards developed there become ANSI standards. He stated that the EIA would enjoy working with the industry on flat panel interface standards.

Mr. Daniel Chen, of Mitsubishi Electronics America, Inc., supplemented Mr. Mock's remarks by describing the activities of the components group of the EIA and their effect on standards for ICs.

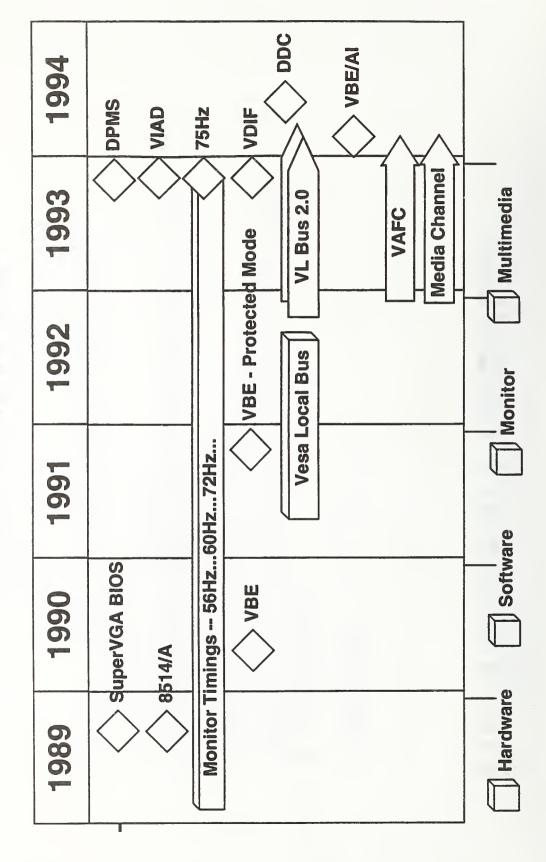

Mr. Scott Vouri of Binar Graphics made a presentation on the Video Electronics Standards Association. His presentation is section (15). VESA, established in 1989, is the industry organization that has set the prevalent standards for display controllers, video BIOS, and monitors in the PC market. VESA has also established the VESA local bus (VL Bus) standard, which is now very widely used in the PC industry to provide a fast path between the CPU, memory, high speed peripherals and video controllers. Many major manufacturers of PCs, video controllers, monitors and flat panels are VESA members. VESA has five technical committees:

- Monitor:

- Local Bus:

- Advanced Video Interface;

- Software standards;

- Advanced Graphics Interface.

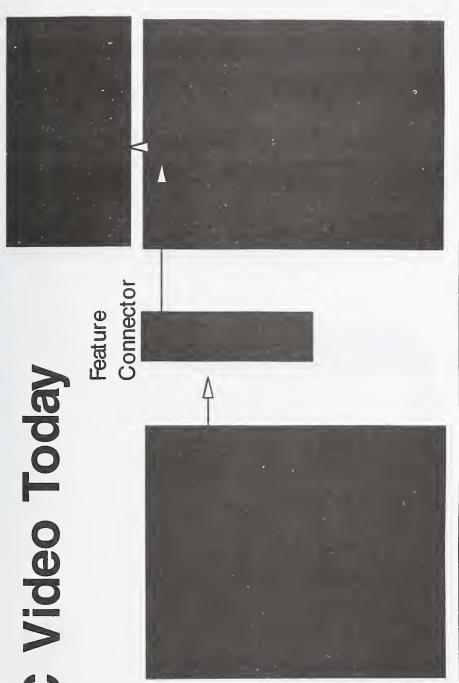

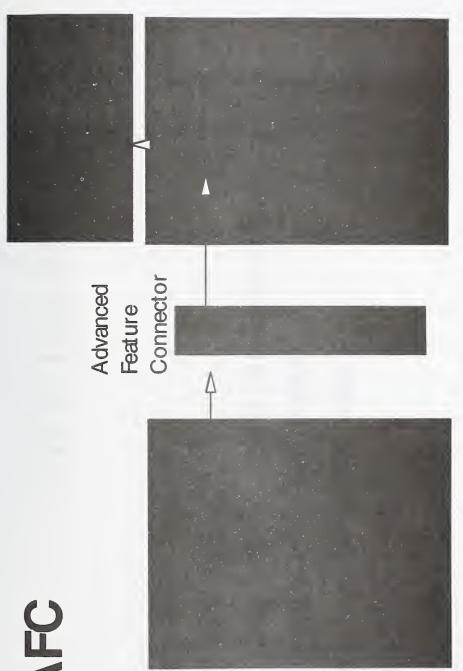

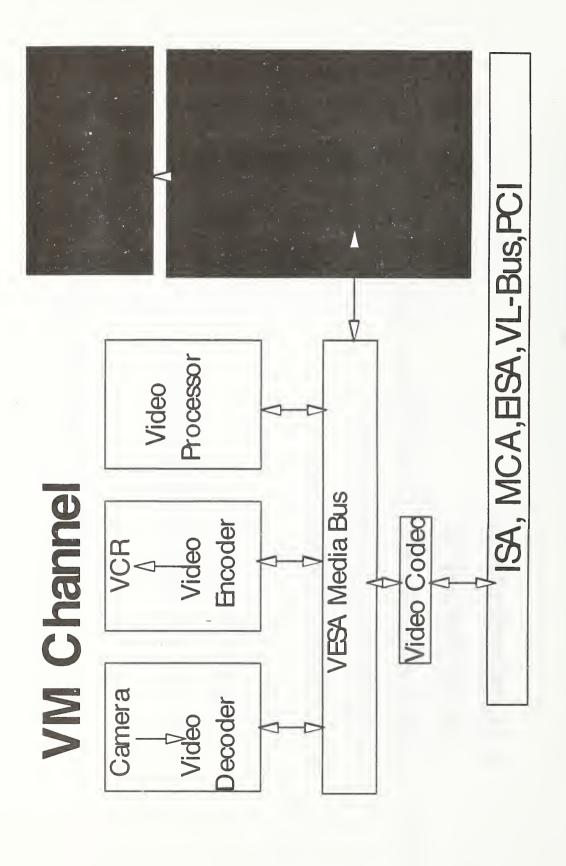

VESA is now developing the VESA Advanced Feature Connector (VAFC) and VESA Media (VM) Channel standards. VAFC provides a 32 bit, 150 Mbps standard for 1280 x 1024 displays that is implementable now with some cost reductions. It connects a video source (such as an MPEG processor card) to a video display adapter. It allows only a single source, is unidirectional, and cost reductions are modest. The VM channel will provide a 32-bit bus supporting 16-bit color that can connect cameras, other video sources such as VCRs, video processors, and the like to a video display adapter. This will be a bi-directional bus and will provide a greater overall cost reduction.

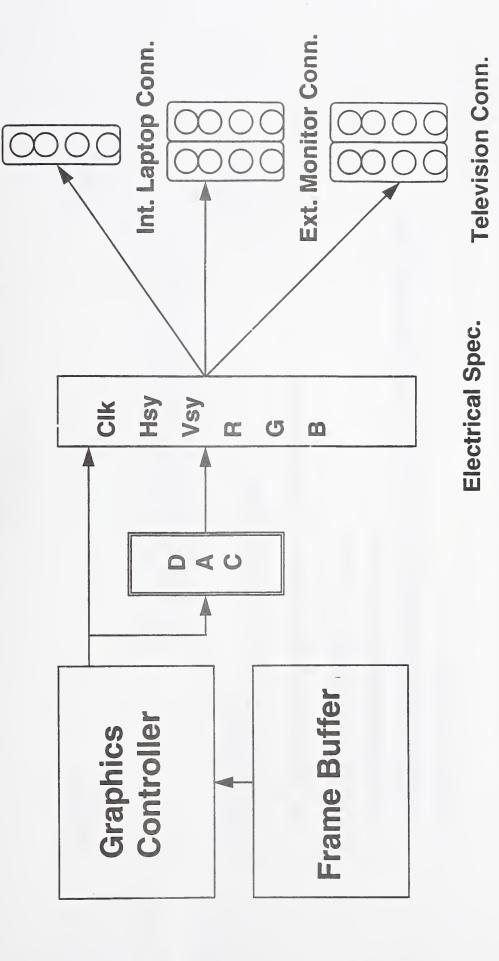

Mr. Vouri described possible panel display standards including an electrical interface and internal laptop connector, and an external monitor connector and a television connector. He stated that he believes VESA is the organization that has the right participants to do the job and could do it quickly and effectively by establishing a special interest group to address the controller-to-display interface. He proposed that interested individuals meet at the VESA office on Feb. 9.

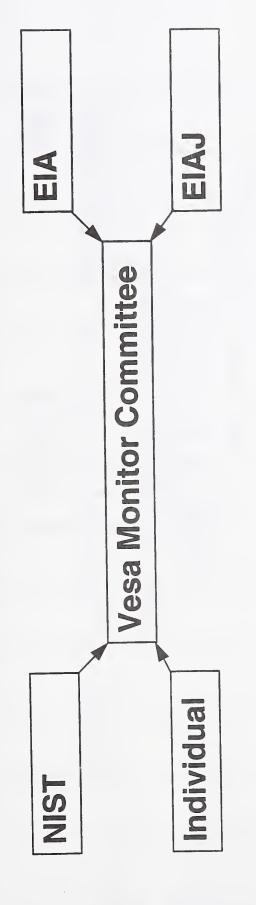

The questions following Mr. Vouri's talk centered on greater participation by volume panel manufacturers, particularly Japanese firms, who were not as well represented at the workshop as the system and controller suppliers. Mr. Vouri said that VESA can reach out to the Electronic Industries Association of Japan (EIAJ), but the thing that will really bring the panel vendors in will be interest and participation of their customers, that is the system vendors. Mr. Knox of Compaq Computer noted that the panel vendors cannot react very quickly, but if customers want a standard, and allow a reasonable time for deliveries of panels with standard interfaces (18 months or so), there wouldn't be a big problem. Mr. Anders Frisk, of ICL and chairman of the VESA Monitor committee, noted that they had scheduled a meeting for March 10 to consider future monitor interfaces, and supported the idea of a meeting on the 9th to consider flat panel interfaces.

Mr. Burr moderated a panel discussion. The members of the panel were:

Mr. Thomas Credelle - Apple Computer;

Dr. Paul Alt - IBM Corporation;

Mr. Rick Knox - Compaq Computer;

Mr. Ron Pacheco - Digital Equipment Corporation;

Mr. Chuck Whelchel - Sharp Electronics Corporation;

Mr. Sunder Velamuri - Cirrus Logic.

Mr. Burr opened the discussion by asking whether a single interface standard that supports both CRTs and flat panels is required. Dr. Alt's response was that there are two different levels of interface that can and should be standardized. One of these, the remote monitor interface, should broadly support CRTs and flat panel technologies through one connector. However, it would probably be premature to immediately begin to standardize this interface; there are at present too many unknowns, including multimedia requirements, and it involves the very paradigm of computing (e.g., networked workstations versus more centralized parallel processors serving a number of relatively "dumb" terminals). Rather, additional workshops and study would be appropriate before plunging into an effort to develop a standard interface. The interface that is now ripe for immediate standardization is the interface for "captive" or "embedded" flat panel displays, such as those that are used in notebook computers. Dr. Alt believed this could be done quickly.

This position was broadly accepted by the participants and the discussion that followed was couched in those terms. Although the discussion was free-ranging and switched back and forth between the two interfaces, in the interest of clarity these minutes summarize the discussion by subject rather than in the order of occurrence.

The participants broadly agreed that in the interim until a general standard can be agreed on, the de facto standard for many remote monitor applications will be the VGA CRT interface. This standard, although deficient in some respects, is very broadly accepted in the huge IBM-compatible PC market. The workstation market is much more diverse, with a number of variations on the CRT interface.

However, there are many problems with this, especially for flat panel technology. Although now uncommon as desktop monitors, LCD panels for projection displays are becoming fairly common. The major difficulty is the range of variation in the coding of the analog video signals and the lack of a dot clock. There was a discussion of the difficulties of recovering the clock for a flat panel. There is a significant challenge to develop clock recovery that works well over the range of video sources found in computers, but it can be done.

There was no definite consensus about the range of distances that must be supported by a monitor interface, although there seemed to be agreement that something more than a few meters was desirable. Nor was it certain whether a monitor interface should be analog or

digital. Mr. Myers of Hewlett Packard returned to the theme that there need not be a sharp distinction between the two, when multilevel digital signals are included. It may be that a standard connector could support both. The precise requirements for multimedia and the level of intelligence required in the display were both discussed. There was broad support for the idea that monitor display should be able to identify themselves and their capabilities to the display controller, and that the controller should be able to configure to the display without operator intervention.

There was broad agreement among the speakers that the time is ripe to standardize the flat panel device interface for embedded displays, such as those in notebook computers and PDAs. Even in this area, there are three fairly distinct markets: PDAs with relatively small screens, notebook computers with at least 640 x 480 resolution, and laptop engineering workstation displays which need a minimum resolution of 1024 x 768. Moreover, both active and passive matrix color and monochrome displays are in fairly wide use. Mr. Burr asked the panel if it is sufficient to cover only the AMLCD displays in the standard and assume that the other technologies are mature and not in need of standardization. The response from the panel was that the other technologies are not disappearing any time soon and that, to be effective, the interface standard should not be limited to just AMLCD displays, but should be applicable to other LCD, plasma, and EL displays.

Although the amount of "intelligence" required on the panel for various applications was not settled by the discussion, broad support was expressed for the idea that enough functionality should be contained in the panel to regularize the interface, in the interest of supporting diverse displays with one interface. This concept, first expressed by Dr. DaCosta in his talk on the previous day, seems to offer a good prospect of a single interface that broadly encompasses various display technologies. The amount of extra functionality incorporated on the panel itself may depend on the application and the intended market niche. Much sentiment was expressed that the panel itself, and not the video controller, is the proper place for such functions as gamma correction and temperature compensation.

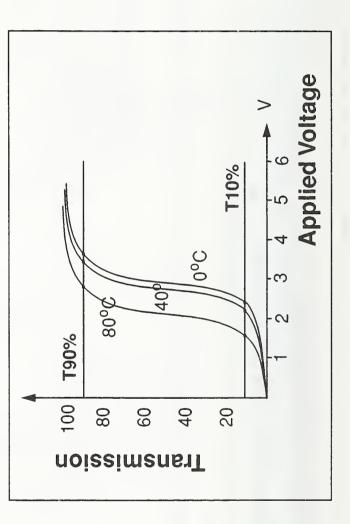

Digital versus analog interfaces were again discussed. Most LCD panels expect a digital input. However, some panels are entirely analog. The general trend in data transmission is digital, and most participants felt that gamma correction and temperature compensation could best be done in the digital domain. There was some discussion about requirements for temperature compensation and gamma correction. Many applications may not be particularly sensitive to precise color matching or consistency, but many other image intensive applications are quite sensitive to these factors.

Mr. Burr noted that there are broadly useful de facto standards for the physical "footprint" of storage peripherals, as well as their interfaces. This, he noted, greatly facilitates plug and play substitution of peripherals by end users. Is it appropriate to consider similar footprint standards for displays? The consensus of the panel was that this would be unwise. Not only are the physical packages for displays evolving, but the physical size of

the display is directly related to and largely determined by its function. This is not the case for storage peripherals. There is no reason simply to change the size of a disk drive for its own sake, but there are applications for displays of many sizes.

A final concern expressed was that mass market FPD vendors were not as well represented on the panel and in the workshop as were computer system manufacturers and controller vendors. This had been sounded earlier in the workshop and would be repeated in the following discussion of proposals for standards development. The feeling seemed to be that it took some time for panel vendors to respond to such initiatives, but if system vendors expressed their interest to their panel suppliers, then they would participate.

At the conclusion of the panel discussion, Mr. Williamson opened the floor to specific proposals on how to proceed. Mr. Vouri made the proposal that VESA establish a special interest group to address the controller to captive flat panel interface in a timely manner. He proposed that interested individuals meet at the VESA office in San Jose on 9 February. Mr. Burr took the floor and led a discussion to develop a consensus about the specific conclusions and action items resulting from the workshop.

The consensus reached at this workshop resulted in the following action items:

- 1. Form a Video Electronics Standards Association Special Interest Group (VESA SIG) to undertake the development of a standard or a series of standards for the interface between a flat panel display and its controller. This interface standard will address both active and passive FPDs in integrated devices. It will cover both the electrical and the mechanical (connector) specifications.

- An organizational meeting will be held on February 9, 1994, at the VESA headquarters with the intention of having a proposal ready to discuss with manufacturers of FPDs at the Society for Information Display (SID) meeting in June. Inputs are requested by March 9, 1994.

- 2. NIST will seek to inform all materially interested parties, especially the flat panel display manufacturers, of the standards plans, and encourage their participation.

- 3. VESA will distribute the February 9, 1994, meeting announcement and agenda.

- 4. The interface for remote FPDs requires additional technical discussions before a standard can be written. Additional workshops on display interfaces and /or technical sessions at the SID Symposium should be explored. In addition, the VESA Monitor Committee invited interested parties to participate in their committee which will be considering interfaces and connectors to desktop and remote FPDs in addition to their CRT interface work.

Dr. Paul Alt will seek to set up a technical session at future SID meetings to consider these long-term display interface requirements. It is too late to add a technical session on interface topics at SID '94. However, an interface session may be possible for SID '95.

The meeting adjourned at 4:00 PM on January 14.

1

Workshop Agenda

#### UNITED STATES DEPARTMENT OF COMMERCE National Institute of Standards and Technology

Gaithersburg, Maryland 20899-0001

# Workshop on the Computer Interface to Flat Panel Displays San Jose Hilton and Towers San Jose, California

#### January 13, 1994

| 11 | • 30 | ΔM    | Check | Tn |

|----|------|-------|-------|----|

| 44 |      | SAL'I | CHECK |    |

- 12:30 PM Opening remarks

Mr. Mark Williamson, NIST

- 12:45 PM "NIST's Advanced Technology Program"

Mr. Thomas Leedy, NIST

- 1:10 PM "Issues in Interfacing Flat-panel Active Matrix TFT LCDs"

Dr. Victor Da Costa, Xerox PARC

- 1:35 PM "High Performance, Cost-Effective Computer and Video Interfacing to Megapixel AC-PDPs"

Ms. Carol A. Wedding, Photonics Systems

- 1:50 PM "Sun's Proposal for a Unified Display Interface"

Mr. Marc Klingelhofer, Sun Microsystems

- 2:15 PM "I/O Connectors for Video Applications, History, Requirements, and Technology to Meet Those Needs" Mr. Gary Manchester, MOLEX, Inc.

- 2:40 PM BREAK

- 3:00 PM "Issues in FPD Interfaces for PC and Workstation Use" Mr. Bob Myers, Hewlett-Packard Co.

- 3:25 PM "Plug and Play Flight Instruments"

Dr. Bill Hale, Wright-Patterson AFB

- 3:50 PM Q&A, Speaker Interviews, General Discussion

- 4:30 PM Reception

Hot and cold hors d'oeuvres and cash bar

# Workshop on the Computer Interface to Flat Panel Displays San Jose Hilton and Towers San Jose, California

#### January 14, 1994

9:00 AM Opening remarks

Mr. Mark Williamson, Mr. Dana Grubb, NIST

9:10 AM "United States Display Consortium"

Dr. Bob Pinnel, United States Display Consortium

9:30 AM "Issues Related to Interfacing Flat Panel Displays"

Ms. Jill Seman, Chips and Technologies

9:55 AM "High Resolution Color LCD Interface Issues"

Mr. Sunder Velamuri, Cirrus Logic

10:20 AM BREAK

10:40 AM "The Voluntary Standards Process" Mr. Bill Burr, NIST

11:10 AM "Electronic Industries Association (EIA)"

Mr. Thomas Mock, EIA.

11:30 AM "Video Electronics Standards Association (VESA)"

Mr. Scott Vouri, Binar Graphics, Inc.

12:00 PM LUNCH

1:00 PM Panel Discussion, "Are Standards Needed for the Computer Interface to Flat Panel Displays?"

Moderator:

Mr. Bill Burr, NIST

Panel Members: Mr. Sunder Velamuri, Cirrus Logic

Mr. Charles Whelchel, Sharp Electronics Mr. Thomas Credelle, Apple Computers

Mr. Rick Knox, Compaq Computer Dr. Paul Alt, IBM Corporation

Mr. Ron Pacheco, Digital Equipment Corp.

2:30 PM Proposals for Standards Development and Future Activities, Invited

3:00 PM BREAK

3:20 PM Discussion of Proposals and Action Items

4:00 PM End of Workshop

2

**List of Attendees**

Mr. Larry Kopp **AMP Inc.** M/S 210-020 P.O. Box 3608 Harrisburg, PA 17105-3608

Mr. Dick Cappels **Apple Computer** 3535 Monroe St. 69-C Santa Clara, CA

Mr. Doug Moore

At&T

2 Oak Way

Room # 4NC20

Berkley Heights, NJ 07922

Mr. Scott Vouri Binar Graphics, Inc 30 Mitchell Blvd. San Rafael, CA 94903

Mr. Sunder Velamuri

Cirrus Logic, Inc.

3100 West Warren Avenue

BZ-541

Fremont, California 94538

Mr. Ron Pacheco

Digital Equipment Corp.

4 Technology Park Drive

DSG1-21K5

Westford, MA 01886

Mr. Thomas Mock **Electronics Industry Association**2001 Pennsylvania Ave N.W.

Washington, DC 2006-1813

Mr. Arley Miller

AMP Inc.

P.O. Box 3605

MS 2414

Harrisburg, PA 17105-3608

Mr. Thomas L. Credelle **Apple Computer, Inc.** 6 Infinite Coop MK 306-3D Cupertino, California 95014

Dr. Les J. Wu AT&T Bell Laboratories 600 Mountain Avenue Room 2d-325 Murray Hill, NJ 07974

Ms. Jill Seman Chips and Technologies, Inc. 2950 Zanker Road San Jose, California 95134

Mr. Rick Knox Compaq Computer, Inc. P.O. Box 629000 MS 080404 Houston, TX 77269-2000

Mr. Brian Fuller **Electrical Enginnering Times** 1054 Saratoga-Sunny Rd. San Jose, CA 95129

Dr. James Akiyama **Epson America** Portland Div 3950 NW Aloclek Place Hillsboro, OR 97124 Dr. C.J. Noorhan Flat Panel Display Co. Bldg WAY-2 Prof. Holstlaan 4 5656 AA Eindhoven The Netherlands

Mr. Bob Myers

Hewlett Packard

3404 East Harmony Road

Fort Collins, Colorado 80525-9599

Mr. Tim Kriegel Hewlett-Packard 1400 Fountaingrove Pkwy 4US-S Santa Rosa, CA 95403

Mr. Tony Wheatley

Hewlett-Packard

1400 Fountaingrove Pkwy

4USM

Santa Rosa, CA 95403

Mr. Ed Anwyl IBM Internal Zip 2212 1000 NW 51st Street Boca Raton, FL 33429

Mr. Anders Frisk ICL Personal Systems 800 Central Expressway M/S 34-10 Santa Clara, CA 95050

Mr. Kaushal Mehta **LSI Logic, Inc.** 1525 McCarthy Blvd. MS G-780 Milpitas, CA 95035 Dr. John Erbacher General Research Corp 2940 Presidential Drive suite 390 Fairborn, OH 45324-6223

Mr. Howard Honig Hewlett-Packard 1000 NE Circle Blvd. 5UP8 Corvallis, OR 97330

Mr. Don Montgomery **Hewlett-Packard** 1400 Fountaingrove Pkwy 4USM Santa Rosa, CA 95403

Dr. Paul Alt

IBM

Thomas J. Watson Research Center

P.O. Box 704, 71-A01

Yorktown Heights, New York 10598

Mr. Kevin Warren

IBM

TJ Watson Research Center

100C Old Sawmill

EastView, NY 10591

Dr. M.K. Hatalis

Lehigh University

Dept. of Electrical Engineering

and Computer Science

Bethlehem, PA 18015

Mr. Daniel Chen Mitsubishi Electronics America, Inc 1050 E. Arques Ave.. Sunnyvale, CA 94086 Mr. Gary Manchester Molex 2222 Wellington Ct. Lisle, IL 60532

Molex Corp. 194 South Hillview Drive Milpitas, California 95035

Mr. Mike Garner

Mr. Frank Eveleno

NEC Electronics

475 Ellis St.

MS MV4561

Mountain View, CA 94039

Mr. Richard Atanus NEC Technologies 1255 Michael Dr. Wood Dale, IL 60191

Mr. William E. Burr NIST Bldg. 225, Rm. A61 Gaithersburg, MD 20899 Mr. Dana S. Grubb **NIST** Bldg.225, Rm. A61 Gaithersburg, MD 20899

Mr. Thomas F. Leedy NIST Bldg.101, Rm. A415 Gaithersburg, MD 20899 Mr. John Roberts **NIST** Bldg.223, Rm. B364 Gaithersburg, MD 20899

Mr. Mark P. Williamson NIST Bldg. 225, Rm. A61 Gaithersburg, MD 20899 Dr. Olivier Prache

Optical Imaging Systems, Inc.

1896 Barrett Street

Troy, MI 48084

Ms. Carol Ann Wedding Photonics Systems Inc. 6975 Wales Road Northwood, OH 43619 Dr. Larry Lewis

Planar Systems, Inc.

1400 N.W. Compton Drive

Beaverton, Oregon 97006

Mr. Larry Weber Plasmaco 180 South Street Highland, New York 12528 Mr. Kevin Gillette

S-MOS Systems

suite 110

11780 Hammersmith Way

Richmond, BC V785E3

Mr. Bill Thompson **SAI Technology** 10240 Sorrento Valley Suite 100 San Diego 92121

Dr. Motofumi Watanabe Sharp Microelectronics Technology Inc.. 5700 NW Pacific Rim Blvd Camas, WA 98607

Mr. Marc Klingelhofer Sun Microsystems 2550 Garcia MTV14-203 Mt. View, CA 94043

Mr. Kevin Ilcifin **Tektronix, Inc.** P.O. Box 500 MS 46-944 Beaverton, OR 97077

Dr. Joe Morrissy

Three-Five Systems, Inc.

10230 South 50th Place

Phoenix, AZ 85044

Dr. Bob Pinnel USDC 2 Oak Way Rm 45F-31 Berkley Heights, NJ 07922-2747

Mr. Wallace Kou Western Digital Corporation 800 East Middlefield Road Mountain View, California 94043 Mr. Charles Whelchel Sharp Electronics Corp. 5700 NW Pacific Rim Blvd. MS 20 Camas, WA 98607

Mr. Ron Hanson Silicon Video Corp. 10460 Bubb Rd. Cuppertino, CA 95014

Mr. Christopher Miles **Systems Planning Corporation** 1429 N, Quincy St. TCI-I Arlington, VA 22207-3645

Mr. Gene Primm Texas Instruments Inc. P.O. Box 655474 MS 8207 Dallas, TX 75265

Dr. Yue T. Chiu US Army Research Laboratory Myer Ctr, Bldg 2700 Fort Monmouth, NJ 07703-5601

Mr. Kirk Lowry **Western Digital Corp.** 800 E. Middlefield Rd. Mountain View, CA 94043

Mr. Bill Hale

Wright Laboratory

WL-AAAZ, Bldg. 146

2210 Eighth Street

STE 1

Wright-Paterson AFB, OH 43433-7511

Dr. Victor Chiu **Xerox Palo Alto Research Center** 3333 Coyote Hill Road Palo Alto, California 94304

Dr. David D. Lee **Xerox Palo Alto Research Center** 3333 Coyote Hill Road Palo Alto, California 94304

Mr. Jin Jiang **Yamaha** 981 Ridder Park Dr. San Jose, California 95131 Dr. Victor Da Costa **Xerox Palo Alto Research Center** 3333 Coyote Hill Road Palo Alto, California 94304

Dr. Alan Lewis **Xerox Palo Alto Research Center** 3333 Coyote Hill Road Palo Alto, California 94304 3

**Opening Remarks**Mark P. Williamson, NIST

### NIST Workshop on the Computer Interface to Flat Panel Displays

San Jose Hilton and Towers January 13 - 14, 1994 San Jose, California

STATES OF THE PREPARE AND TECHNISHED AND TECHNISH AND TECHNISH AND TECHNISHED AND TECHNISH AND TE

UNITED STATES

DEPARTMENT OF COMMERCE

NATIONAL INSTITUTE OF STANDARDS

AND TECHNOLOGY

### Introductions

■ Mr. Dana Grubb, Co-chairman

■ Mr. William E. Burr, Secretary, Moderator

■ Mr. John Roberts

■ Mr. Thomas Leedy, ATP

■ Mr. Mark P. Williamson, Organizer, Chairman

## Workshop Objectives

77700

of standards for the computer interface to flat ■ Determine the need for a standard or a series panel displays

- logical, electrical, & mechanical

» integrated device displays

» FPD monitors

» entertainment displays

## Workshop Objectives

Identify what types of standards are needed

de facto standards

- formal national standards

formal international standards

■ Identify viable approaches for developing flat panel display interface standards

- industry groups

- formal standards committee

## Workshop Objectives

Obtain consensus on a coordinated plan for standards development

### NIST Activities in Flat Panel Displays

- NIST the nation's leading measurement and standards laboratory

- Computer Systems Laboratory

- Flat panel display interfaces

- Electronics and Electrical Engineering Lab

- Display performance and quality metrics

- I Physics Laboratory

- Radiometric, colorimetric & photometric calibration

- Advanced Technology Program

- American Display Consortium

#### NIST Flat Panel Display Interface Project

Support standards development

- initiate and participate in standards activities

provide a neutral laboratory for prototyping and feasibility studies

represent government agencies' interest in standards

development

#### NIST Flat Panel Display Interface Project

- Support the implementation of advanced display technologies

- research and development of advanced interfaces

- prototype and demonstrate high risk / advanced interfaces

- develop meaningful performance measurements

#### NIST's Advanced Technology Program Mr. Thomas Leedy, NIST

#### り と

# Advanced Technology Program

#### Thomas Leedy Project Manager

National Institute of Standards and Technology **Technology Administration** Department of Commerce

### Advanced Technology Program MISSION

Stimulate U.S. economic growth through the development and application of high-risk technologies by companies.

### ATP STRATEGY

and co-fund high-risk technology development programs. Develop technologies that are: Work with U.S. industry to plan, execute,

- process- and product-specific applications ENABLING - - provide technical basis for

- HIGH VALUE - offer large and/or strategic long-term benefits to the U.S. economy

### ATP ELIGIBILITY

- Individual companies

- No more than 3 years

- Up to \$2 million total

- ATP pays only direct costs

- Joint ventures

- No more than 5 years

- No limit on award amount

- ATP share less than 50%

- No direct funding to universities, government agencies or non-profit independent research institutes

# MAJOR CHARACTERISTICS OF THE ATP

- Development / application of high-risk technologies to stimulate economic growth

- Market oriented -- industry proposes ideas, shares costs, and performs work

- Competitive selection process - technical and business merit

- Cost sharing

### ADVANCED TECHNOLOGY PROGRAM Important Statistics - - 3 Competitions

Proposals Submitted

Participating Organizations\*

Total ATP Funding Requested

Total Estimated Cost Share

\$1 \$1 B

09

1232

099

Number of Awards

(Joint Ventures)

(Single Applicants)

Participating Organizations\*

Total ATP Funds Committed

Total Estimated Cost Share

Award Size - - Range

(18) (42) 150 \$187 M \$210 M \$500K - \$20 M

<sup>\*</sup> Excludes Subcontractors

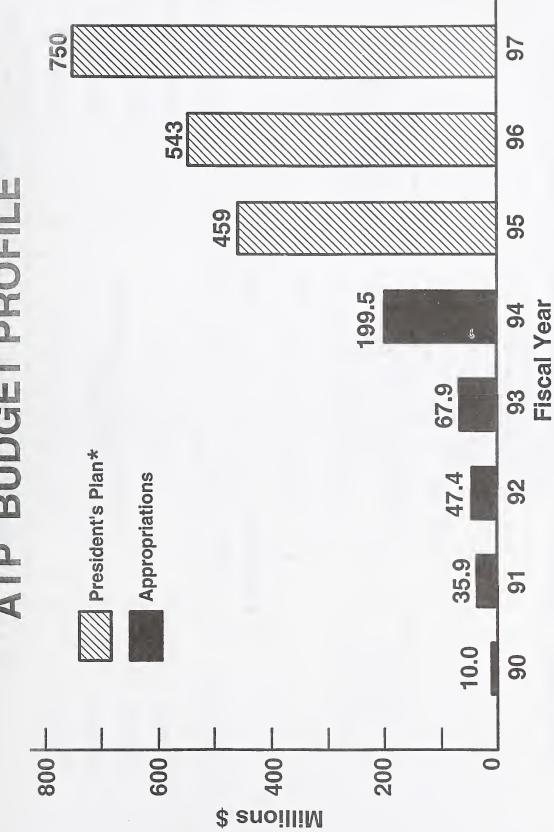

## ATP BUDGET PROFILE

\* Based on "A Vision of Change for America," President Clinton's Economic Plan - - February 17, 1993

# SELECTION PROCESS MANAGEMENT

## ATP SELECTION PROCESS

#### ATP PROPOSALS

#### SCREENING

#### CLASSIFICATION

#### TECHNICAL REVIEW

Quality / Innovativeness

Technical Risk / Feasibility

Plan Coherency

Systems Integration

Experience / Qualifications

#### BUSINESS REVIEW Commercial Benefits

Technology Transfer Experience / Qualifications Commitment /Organization

### SEMIFINALISTS IDENTIFIED Oral Review Site Visit (Optional)

FINAL SELECTION

Rank Order of Proposals

Balanced Program

## TECHNOLOGIES FUNDED BY ATP

As a percent of \$187 M Awarded

#### BY TYPE OF ORGANIZATION ATP 60 AWARDEES

Joint Venture

### \$187 MILLION OF ATP FUNDS AWARDED BY TYPE OF ORGANIZATION

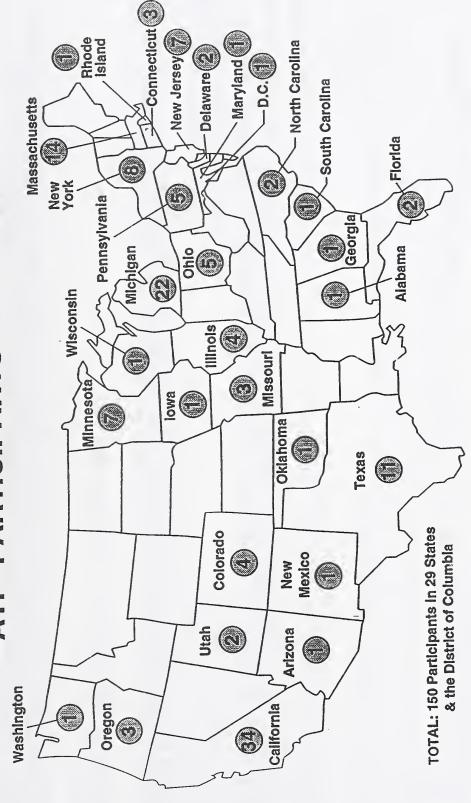

## ATP PARTICIPANTS\* BY STATE

\* "Participants" includes joint venture members, and excludes subcontractors, informal collaborators with joint ventures, and collaborators and strategic partners of slingle applicants.

### Display Technology

## Advanced Manufacturing Technology for Low-Cost Flat-Panel Displays

American Display Consortium,

Project budget: \$14,909 K competing against large, vertically integrated Japanese firms — to develop A joint venture by several U.S. producers of flat-panel displays for computers key production and testing technologies for a multi-billion-dollar industry. ATP Award: \$7,305 K

# Scalable High-Density Electronics Based on MultiFilm Modules

The MultiFilm Venture, Taunton, MA

Project budget: \$5,705 K Develop high-density electronic circuit modules based on thin-film silicon circuits which can be closely packed laterally and vertically. ATP Award: \$2,776 K

(USDC - Palo Alto, CA - 940111)

### Display Technology

# Large Area Digital HDTV Field Emitter Display Development

#### FED Corporation

Develop manufacturing techniques for large-scale, flat panel displays based on arrays of field emitters to make a sort of "flat CRT."

ATP Award: \$2,000 K

Project budget: \$2,943 K

# Patterning Technology for Color Flat-Panel Displays

### The American Display Consortium

Project budget: \$13,192 K Develop a group of patterning technologies necessary for the manufacture of color flat-panel displays, including large-area photoexposure tools, printing tools, panel alignment methods, and a final inspection tool. ATP Award: \$6,464 K

(USDC - Palo Alto, CA - 94011)

### Display Technology

# Optically Controlled Alignment Materials for Liquid-Crystal Displays

Hercules, Inc.

polarized light, leading to an improved method of manufacturing liguid crystal Develop a novel technology for optically aligning liquid crystals using displays at lower costs and greater yield.

ATP Award: \$1,671 K

Project budget: \$3,042 K

# Advanced Cathode for Flat Fluorescent Light Source

Thomas Electronics, Inc.

possible a new generation of high-efficiency, high reliability area light sources Develop a novel barium dispenser cathode for flat fluorescent lights, making for use in flat panel displays.

ATP Award: \$718 K

Project budget: \$933 K

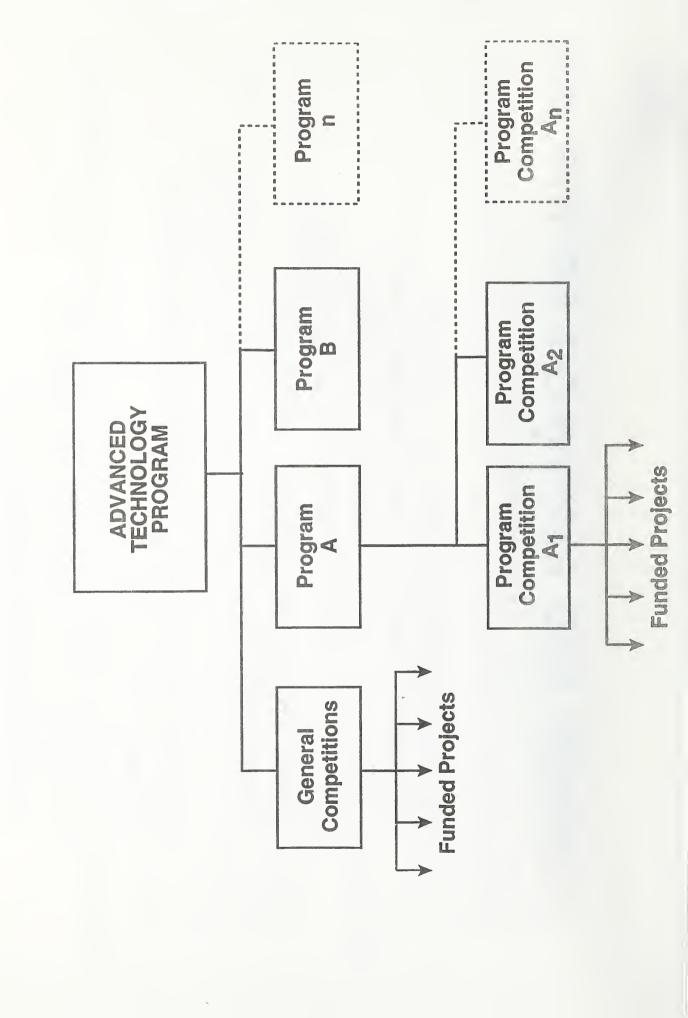

## ROADMAP FOR EXPANSION OF THE ATF 1994 TO 1997

- well-defined technical and business goals Establish programs under the ATP with

- Establish an administrative framework to get industry ideas and evaluate, define, and select programs

- Increase the number of projects funded through program competitions

- Continue to hold general competitions to all areas of technology

# DESIRED PROGRAM CHARACTERISTICS

- Well-defined technical and business goals

- Pathway from R&D to market

- Well-defined research plan

- Measurable impact on U.S. economic growth

- Program duration: approximately 5 or more years

- Program funding: in the range of \$20-50 million per year (federal share)

- Multiple competitions per program - each competition can result in multiple projects - - single companies and

- Performance measures linked to technical / business goals and ultimate impact on economic growth

# PROGRAM DEFINITION AND EXECUTION

# CRITERIA FOR ATP PROGRAM SELECTION

- 1. POTENTIAL U.S. ECONOMIC BENEFIT

- 2. GOOD TECHNICAL IDEAS

- 3. STRONG INDUSTRY COMMITMENT

- 4. OPPORTUNITY FOR ATP FUNDING TO MAKE A MAJOR DIFFERENCE

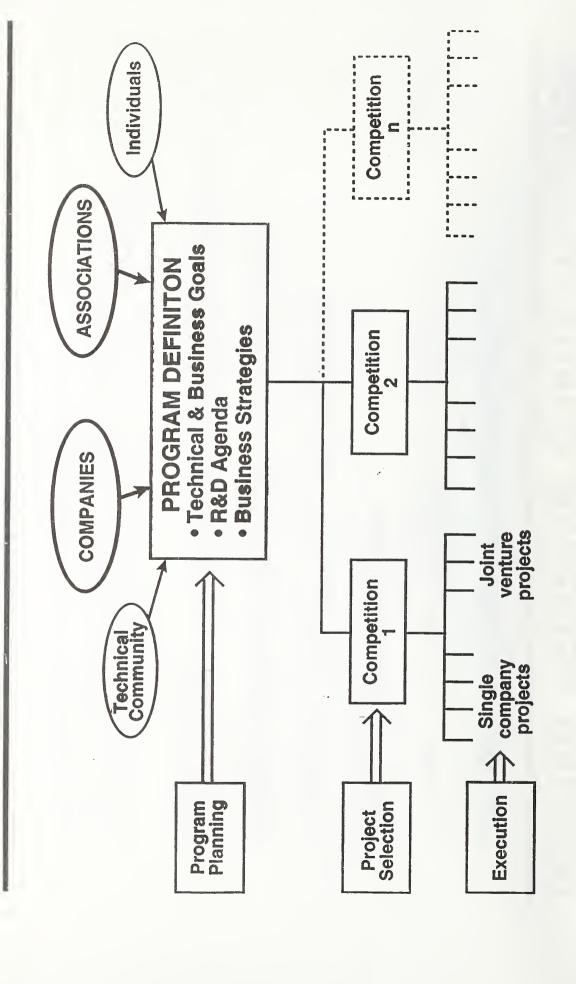

### ATP Program Planning and Execution KEY CONCEPTS

- ATP listens to industry

- Joint development of technology and business goals and R&D plans

- Industry executes R&D and commercialization

- Cost-sharing essential

- Aim to enhance U.S. economic growth

- Success depends on good ideas and cooperation from industry

SEND US YOUR PROGRAM IDEAS!

# HOW TO SUBMIT A PROGRAM IDEA

that describes the proposed technical and business goals and addresses program selection criteria to: Submit a letter or brief white paper (< 10 pages)</li>

Program Ideas Advanced Technology Program NIST A430 Admin. Bldg. Gaithersburg, MD 20899 1 - 800 - ATP - FUND (General Information) ATP@MICF.NIST.GOV 1 - 301 - 926 - 9524 Facsimile E-Mail

# NO PROPRIETARY INFORMATION SHOULD BE SUBMITTED!

Issues in Interfacing Flat-panel

Active Matrix TFT LCDs

Dr. Victor Da Costa, Xerox PARC

## Issues in Interfacing Flat-panel Active Matrix TFT LCD's

Victor M. Da Costa and David D. Lee

Xerox Palo Alto Research Center 3333 Coyote Hill Road Palo Alto, CA 94304

# No standard interface to flat panel displays

- Characteristics or requirements of FPDs vary among technologies and applications.

- This leads to customization and complexity in interface design

#### Need for

A consistent and flexible interface to the widest possible range of FPDs.

### Contents

1. Basics of Matrix driven FPDs interfaces.

2. Interfacing problems in driving AMLCD's.

3. Summary and conclusions.

This talk will be AMLCD specific, but the basic concepts apply to FPDs in general.

## A Matrix Driven FPD

To address NXM pixels requires N+M drivers (minimum).

Two types of drive schemes:

Passive STN LCD - uses time multiplexed drive.

Active Matrix LCD - a transistor at each pixel provides drive at all times.

CRT display:

N Column Drivers

single pixel scan

Matrix driven FPD:

single row scan

M Row Drivers

display panel

### Trends are to:

## Highly optimized/customized display adapter to handle display dependent functions.

This leads to:

- complexity in the display controller ASICs.

- similar displays in function having different signals/connectors.

- the controller needing to change as the display parameters (resolution, number of colors) change.

# Simple and generalized column and row driver ICs

They tend to have common characteristics (# of drive outputs, output voltage levels).

XEROX

### Contents

1. Basics of Matrix driven FPDs Interfaces

2. Interfacing problems and issues

3. Summary and conclusions

### **Active Matrix LCD**

## Characteristics of future AMLCDs:

- wide range of technologies and driver electronics will be used

TFT technologies - Poly Si, α-Si

LC materials

driver IC and packaging

- very high resolution and more colors

3 or more subpixels per color pixel with 6-8bit gray levels more than 1000 lines and 1000 color pixels per line per subpixel.

- high image quality

active matrix technology will be better than a CRT

# Problems and Issues in Driving High Resolution AMLCD's

- 1. Analog or digital interface, which one?

- 2. Speed mismatch in frame buffer output and panel driver IC input.

Image Quality Issues:

- 3. Different color filter mosaics may be used.

- 4. Differing Color/grey level control/correction schemes

- These issues lead to complexity in interface design.

This results in highly customized graphics adapters to handle AMLCD-specific controls.

### PLAC