FILE COPY

DO NOT REMO

**NBSIR 77-1231**

# Measurement of Transistor Collector-Emitter Saturation Voltage

RECEIVED

RATE 6/13/77

OTP

K. O. Leedy

Electronic Technology Division Institute for Applied Technology National Bureau of Standards Washington, D.C. 20234

June 1977

Final

Prepared for Defense Nuclear Agency Washington, D.C. 20305

# MEASUREMENT OF TRANSISTOR COLLECTOR-EMITTER SATURATION VOLTAGE

K. O. Leedy

Electronic Technology Division Institute for Applied Technology National Bureau of Standards Washington, D.C. 20234

June 1977

Final

Prepared for Defense Nuclear Agency Washington, D.C. 20305

# U.S. DEPARTMENT OF COMMERCE, Juanita M. Kreps, Secretary

Dr. Sidney Harman, *Under Secretary*Jordan J. Baruch, *Assistant Secretary for Science and Technology*NATIONAL BUREAU OF STANDARDS, Ernest Ambler, *Acting Director*

## TABLE OF CONTENTS

|                            | Page                                                                                                                                                       |   |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Abstract                   |                                                                                                                                                            |   |

| Introduction               |                                                                                                                                                            |   |

| Definition of Saturation   |                                                                                                                                                            |   |

| Measurement Method         |                                                                                                                                                            |   |

| Temp                       | rature Effects                                                                                                                                             | , |

| Current Effects            |                                                                                                                                                            | ١ |

| Other Important Parameters |                                                                                                                                                            |   |

| Summ                       | ry                                                                                                                                                         |   |

| Acknowledgment             |                                                                                                                                                            |   |

| References                 |                                                                                                                                                            |   |

| Appendix                   |                                                                                                                                                            |   |

| Distribution               |                                                                                                                                                            |   |

|                            | LIST OF FIGURES                                                                                                                                            |   |

|                            | Page                                                                                                                                                       |   |

| 1.                         | llustration of the three transistor operating regions: ut-off, active, and saturation                                                                      |   |

| 2a.                        | out-off, active, and saturation                                                                                                                            |   |

| <b>_</b>                   | each of the three 2N2222 transistors 6                                                                                                                     |   |

| 2Ъ.                        | collector-emitter voltage as a function of temperature for each of the three 2N3055 transistors                                                            |   |

| 2c.                        | collector-emitter voltage as a function of temperature for each of the three 2N5840 transistors                                                            |   |

| 3.                         | ypical change in collector-emitter voltage as a function f temperature for the three device types with the data veraged for the three samples of each type |   |

| 4a.                        | ollector-emitter voltage as a function of duty cycle for ach of the three 2N5840 transistors                                                               |   |

# List of Figures (continued)

|     |                                                                                                                                           | Pa | age |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 4b. | Typical change in collector-emitter voltage as a function of duty cycle averaged for the three 2N5840 transistors                         |    | 12  |

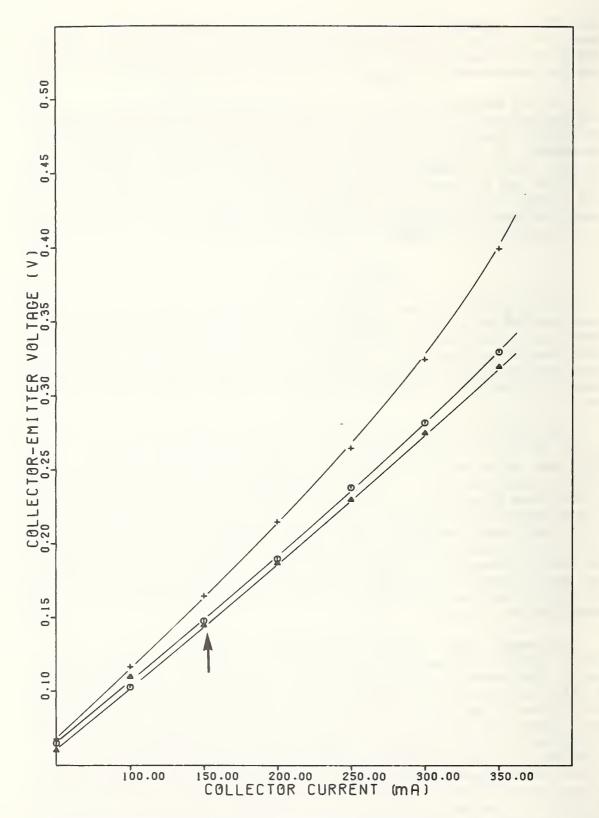

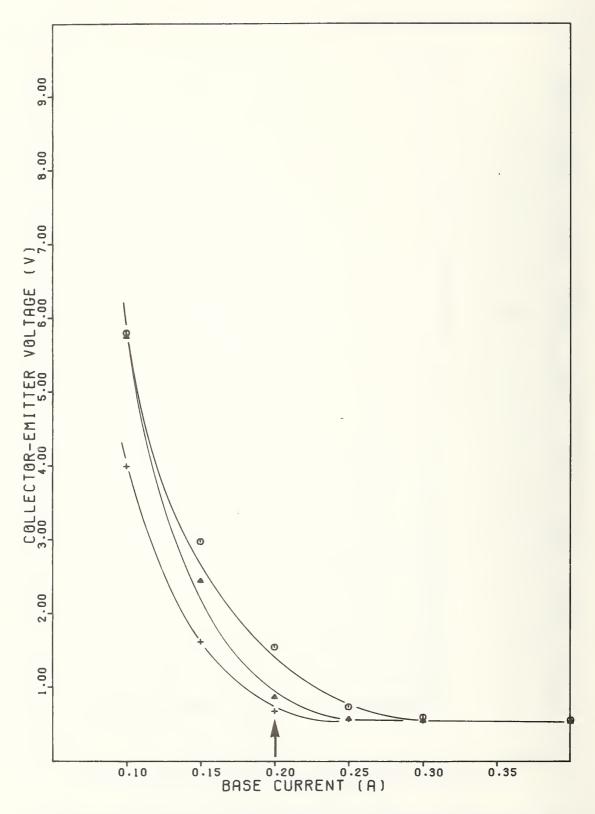

| 5a. | Collector-emitter voltage as a function of collector current with a fixed base current of 15 mA for each of the three 2N2222 transistors  | •  | 14  |

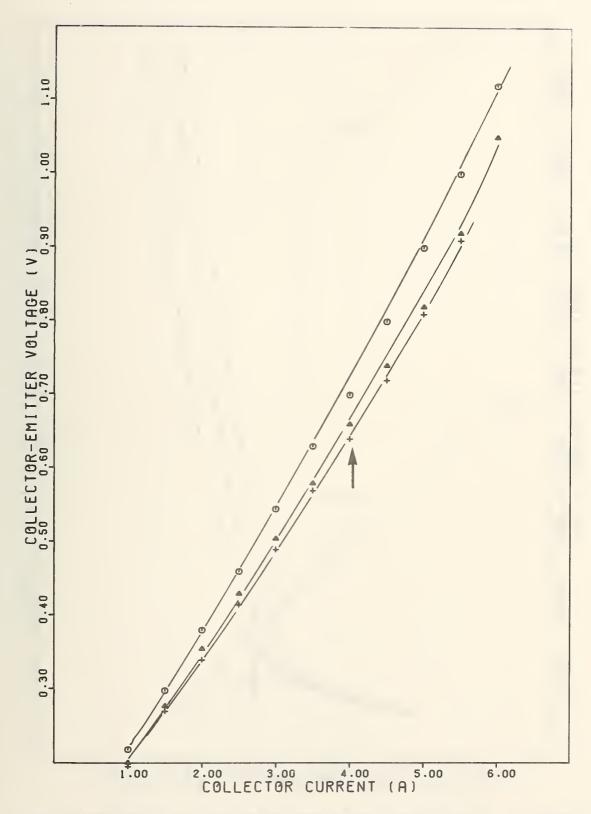

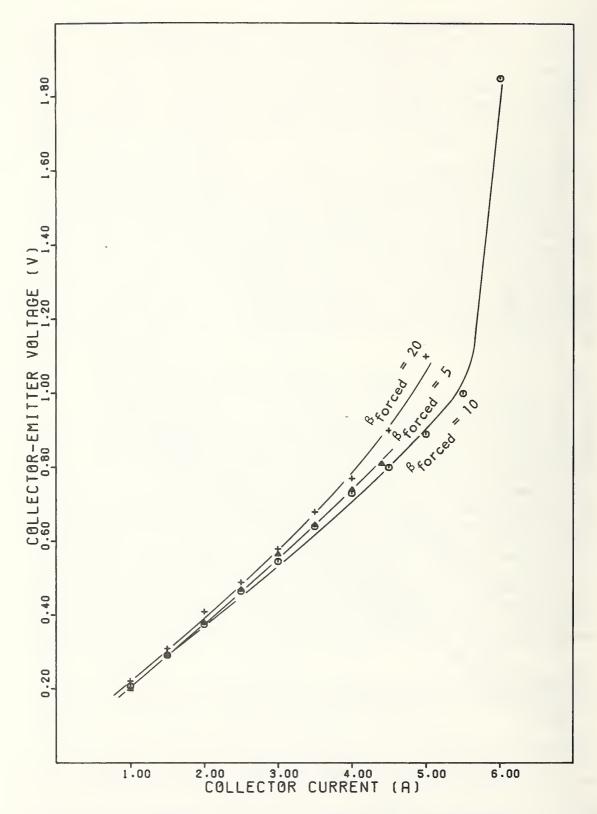

| 5b. | Collector-emitter voltage as a function of collector current with a fixed base current of 400 mA for each of the three 2N3055 transistors | •  | 15  |

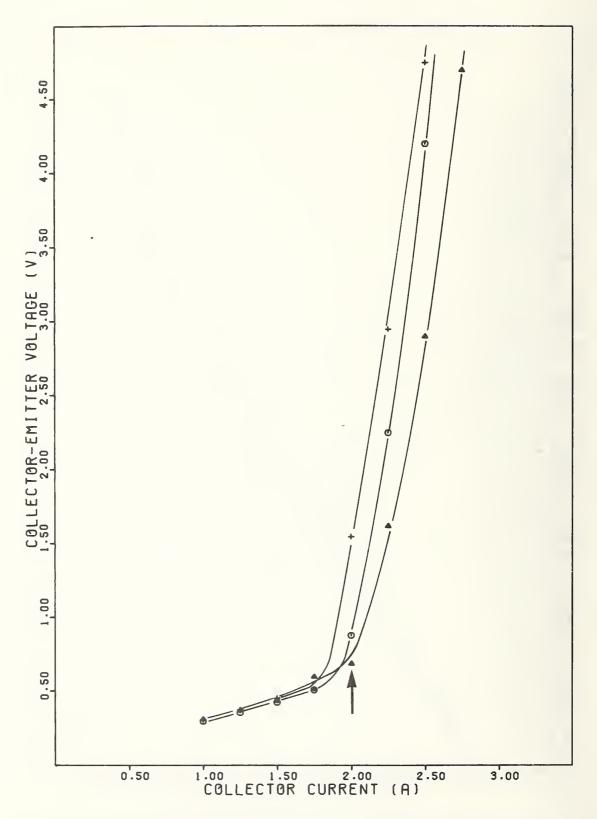

| 5c. | Collector-emitter voltage as a function of collector current with a fixed base current of 200 mA for each of the three 2N5840 transistors | •  | 16  |

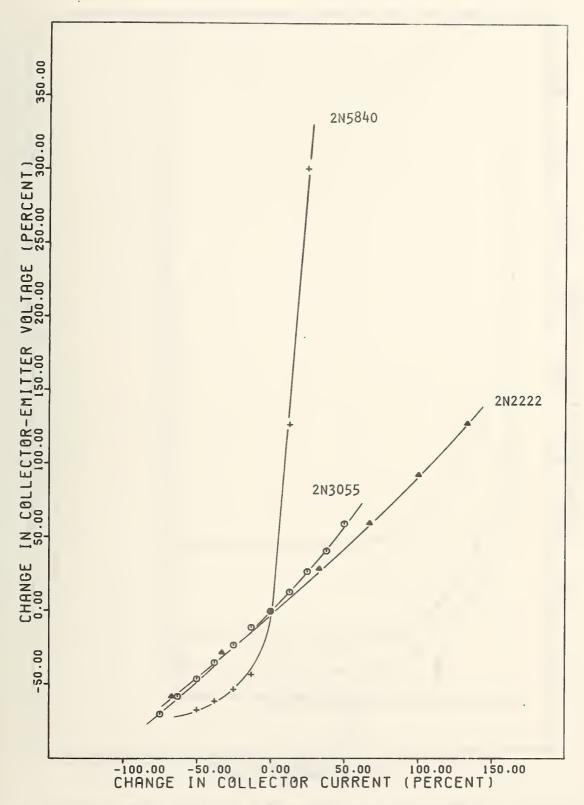

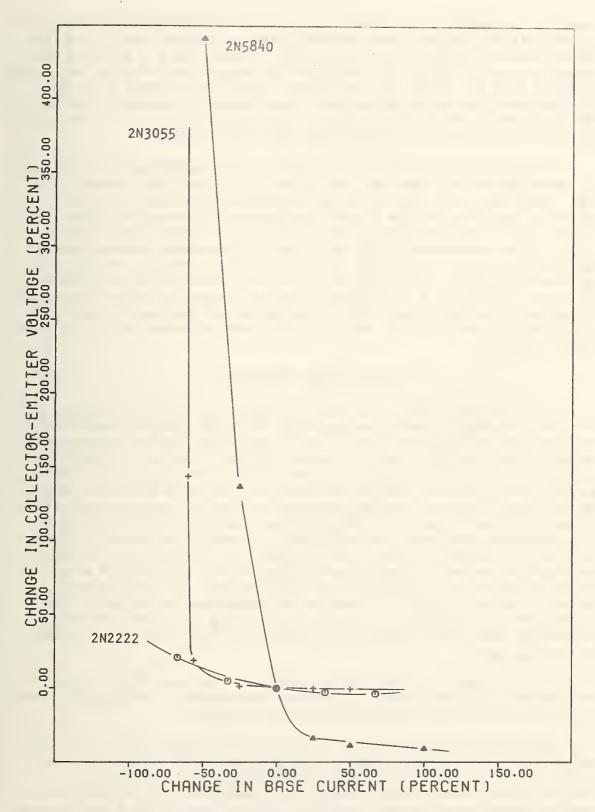

| 6.  | Typical change in collector-emitter voltage as a function of change in collector current                                                  | •  | 17  |

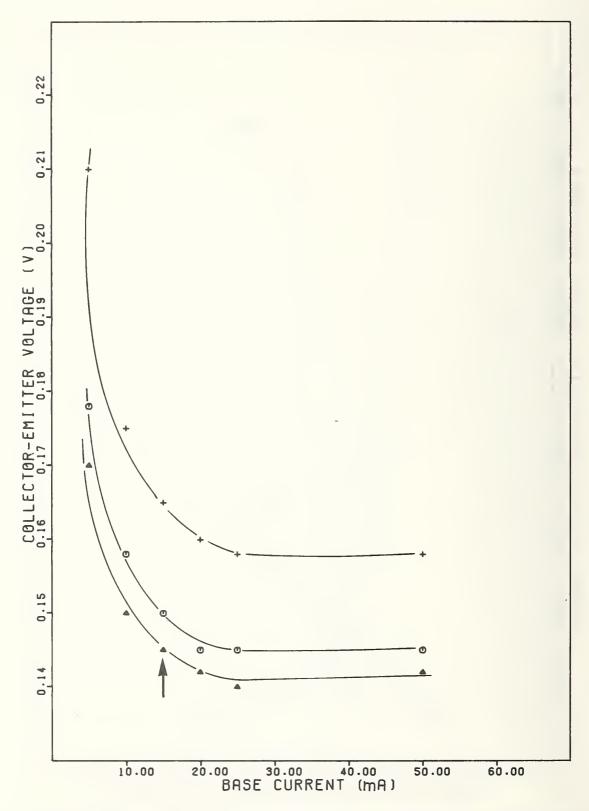

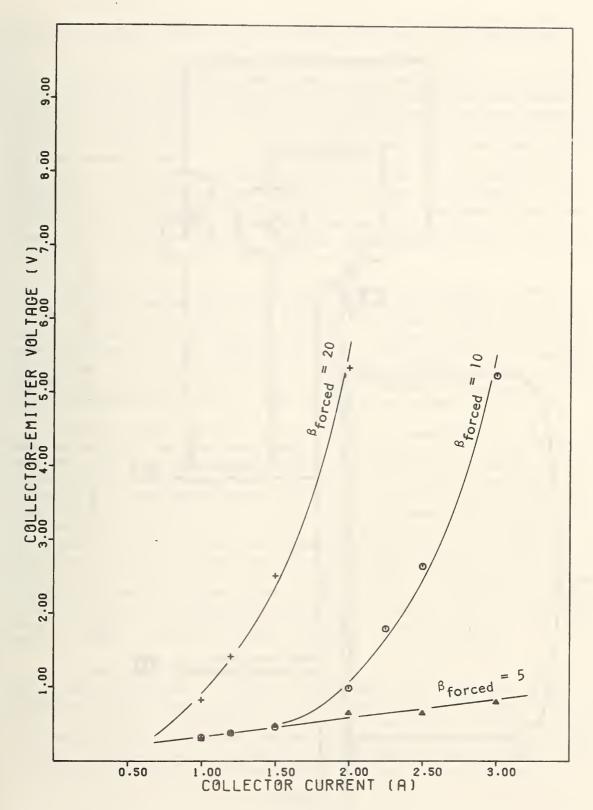

| 7a. | Collector-emitter voltage as a function of base current with a fixed collector current of 150 mA for each of the three 2N2222 transistors |    | 18  |

| 7Ъ. | Collector-emitter voltage as a function of base current with a fixed collector current of 4 A for each of the three 2N3055 transistors    |    | 19  |

| 7c. | Collector-emitter voltage as a function of base current with a fixed collector current of 2 A for each of the three 2N5840 transistors    |    | 20  |

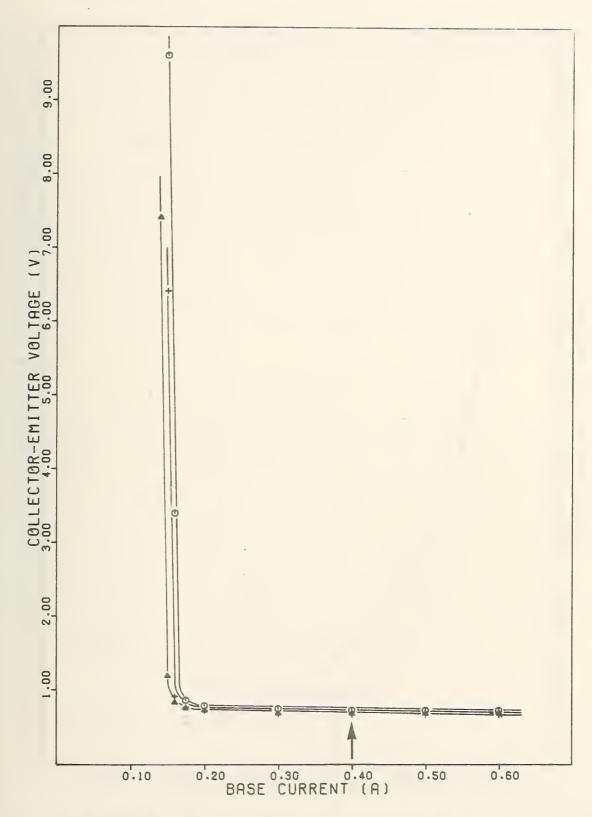

| 8.  | Typical change in collector-emitter voltage as a function of change in base current                                                       | •  | 21  |

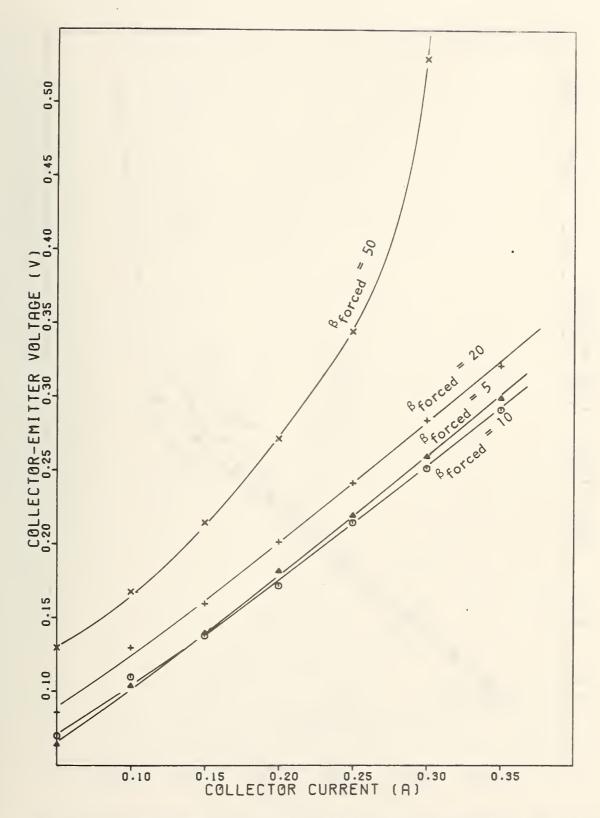

| 9a. | Collector-emitter voltage as a function of collector current for different values of forced $\beta$ for a 2N2222 transistor               |    | 23  |

| 9Ъ. | Collector-emitter voltage as a function of collector current for different values of forced $\beta$ for a 2N3055 transistor               |    | 24  |

| 9c. | Collector-emitter voltage as a function of collector current for different values of forced $\beta$ for a 2N5840 transistor               |    | 25  |

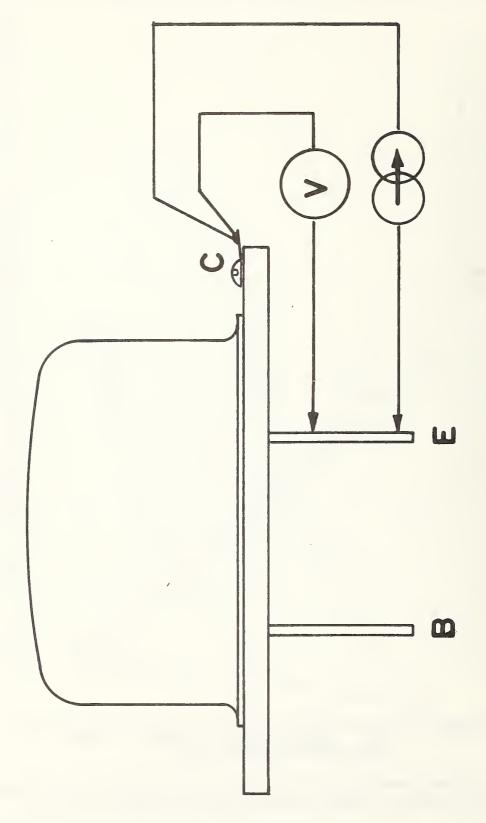

| 10. | Illustration of Kelvin connections                                                                                                        |    | 26  |

#### Measurement of Transistor Collector-Emitter Saturation Voltage

K. O. Leedy

Institute for Applied Technology

National Bureau of Standards

Washington, D. C. 20234

#### ABSTRACT

This report presents a detailed method for the measurement of collector-emitter saturation voltage. The method which is included in the Appendix is proposed for standardization. The report also contains a description of the laboratory confirmation of the method and a discussion of the precautions to be taken to assure repeatability of the measurement. Emphasized is the necessity to determine that the conditions for saturation are met during the measurement.

#### INTRODUCTION

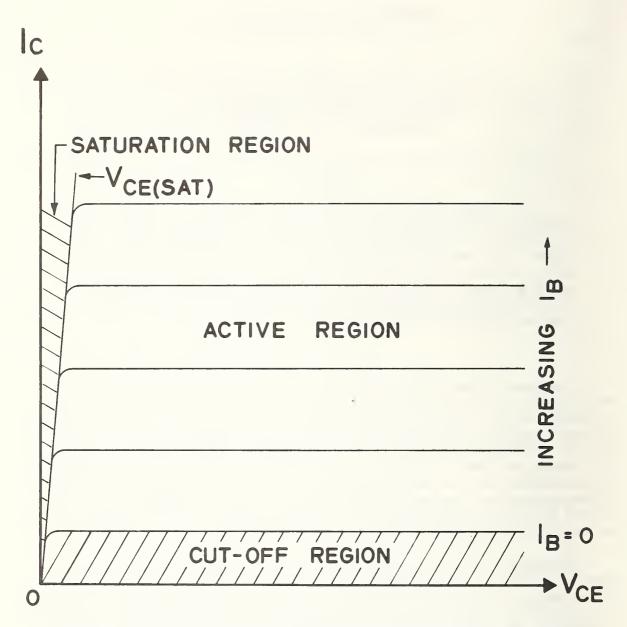

There are three regions of transistor operation: cut-off, active, and saturation. These are illustrated in figure 1 which shows curves of collector current versus collector-emitter voltage for different values of base current. For transistors used in switching applications the cut-off and saturation regions are most important. In saturation, or in the "on" state, an ideal transistor switch should have a very low resistance, approaching that of a short circuit so that the voltage drop across the collector-emitter terminals approaches zero. This voltage drop is called the collector-emitter saturation voltage and is usually represented in specification literature by the symbol  $V_{\rm CE\,(SAT)}$ .

The saturation voltage is an important parameter because it can be used to predict the performance of a transistor used in switching apparatus such as in d-c to a-c power inverters, chopping circuits, or logic circuits. It represents the "zero" logic level in many types of digital circuits. It is important to know how low the collector-emitter voltage becomes in saturation because during saturation the transistor passes the most current for the longest periods of time, and power dissipation at the collector can become excessive. When a system design is to be used in a radiation environment, it is important to know the change in saturation voltage as a result of radiation dose so that the design can accommodate the changed value.

In the application of a transistor in circuit, it is not always necessary to know the actual  $V_{\text{CE}(\text{SAT})}$ , that is, the collector-emitter voltage of a transistor operating in the saturation region. Instead, it is important to know that for the bias conditions of interest, the collector-emitter voltage is less than a specified value. The circuit designer would have assumed this value, probably from knowledge of

Figure 1. Illustration of the three transistor operating regions: cut-off, active, and saturation.

V<sub>CE(SAT)</sub> for that transistor type. The measurement method attached can be used to determine if a particular transistor will meet the requirement if the test for saturation is omitted.

From the diagram in figure 1, it is apparent that saturation is a region and that  $V_{CE(SAT)}$  is not a single point but rather a line. Its value depends on the collector current and base current among other variables. The purpose of the measurement presented here is to adequately define all variables so that a repeatable measurement of  $V_{CE(SAT)}$  is possible. The method itself is given in the Appendix. It can be used for any  $V_{CE(SAT)}$  measurement but it is most useful when a measurement of a change in  $V_{CE(SAT)}$  is required. Normally, when  $V_{CE(SAT)}$  is measured, it is for the purpose of assuring that it be less than a maximum voltage in a specification. This implies that better devices have lower values of  $V_{CE(SAT)}$ . Therefore, it is to the advantage of the manufacturer to report a low value. To perform his measurement, he then need only control his parameters to the extent that he obtains a measured value of  $V_{CE(SAT)}$  low enough to meet the specification. To measure a change in  $V_{CE(SAT)}$ , however, it is necessary to make the measurement twice with all important independent variables specified and carefully controlled.

#### DEFINITION OF SATURATION

By definition, a transistor is operating in the saturation region when both the emitter-base and the collector-base junctions are forward-biased. The collector-emitter voltage in this condition has two components: the junction saturation voltage, defined below, and the voltages due to the collector saturation current in the collector series resistance and due to the emitter current in the emitter series resistance. The base series resistance can be neglected.

The junction saturation voltage is the difference between the forward-biased junction voltages of the collector-base and the emitter-base junctions. It is given by the Ebers and Moll<sup>2</sup> expression as:

$$\Delta V_{j} = \frac{kT}{q} \ln \frac{\alpha_{I} \left[1 - \frac{I_{C}}{I_{B}} \frac{1 - \alpha_{N}}{\alpha_{N}}\right]}{1 + \frac{I_{C}}{I_{B}} (1 - \alpha_{I})}$$

where

$\Delta V_{i}$  = junction saturation voltage, V

T = absolute temperature, K

$\alpha_{\rm N}$  = common base large signal d-c current gain with the emitter functioning as an emitter and the collector functioning as a collector

a = common base large signal d-c current gain with the emitter functioning as a collector and the collector functioning as an emitter

$I_C$  = collector current, A

$I_R$  = base current, A

k = Boltzman's constant  $(1.381 \times 10^{-23} \text{ J/K})$

q = charge on electron  $(1.602 \times 10^{-19} \text{ C})$ .

The saturation voltage is then given by

$$V_{CE(SAT)} = \Delta V_{j} + I_{C}r_{C} + I_{E}r_{E}$$

where

$r_{c}$  = collector series resistance,  $\Omega$

$\mathbf{r}_{_{\mathrm{F}}}$  = emitter series resistance,  $\Omega.$

The junction saturation voltage is normally small and rather insensitive to variations in collector or base current because of the logarithmic relation. Of more significance, particularly for power transistors, is the saturation voltage due to the resistive component. The collector region of many power transistors is lightly doped to obtain high breakdown voltages and the transistor is usually operated at high currents in saturation. Under conditions which affect  $V_{CE}(SAT)$ , such as an increase in temperature or an exposure to radiation, the effect on the collector resistance can produce a major change in  $V_{CE}(SAT)$ , as can the effects of variations in transistor gain.

#### MEASUREMENT METHOD

The method for measuring  $V_{CE(SAT)}$  as outlined in the Appendix requires that the following measurement conditions be specified:

- 1)  $I_c$  the collector current

- 2)  $I_{R}$  the base current

- 3) ambient temperature

- 4) selection of a pulsed or d-c method, and

- 5) the pulse width and duty cycle (if other than 300  $\mu$ s and 2%, respectively).

This information must be included in the specification for  $V_{\text{CE}(SAT)}$  for the particular device to be tested, such as in the detailed specifi-

cation in the appropriate military standard, if the specification is to be meaningful. The method instructs the user how to determine all circuit values. It describes all necessary apparatus, procedural steps to be performed, data to be taken, and cautions to be observed.

Using this method, several experiments were performed to determine the sensitivity of the measured VCE(SAT) to several variables. Three transistor types were chosen for these experiments: a small-signal transistor (2N2222), a single-diffused power transistor (2N3055), and a triple-diffused power transistor (2N5840). These devices are found in military systems and each is available in a military version. These device types were selected to provide a wide variation in measured results for variations in the measurement parameters. Three devices of each type were used for each experiment. All were off-the-shelf commercial transistors. Though the number of devices used is small, the data indicate the trends in the effects of the variables and, as such, indicate which parameters are necessary to control carefully and which are not.

#### TEMPERATURE EFFECTS

The value of  $V_{\text{CE}(\text{SAT})}$  is dependent on temperature in at least two ways: first, temperature appears in the expression for the junction saturation voltage, and second, the collector series resistance is a function of temperature. The method specifies that the measurement be made at a nominal temperature of 20°C and that the power levels used do not give rise to significant heating of the junction. To investigate the effects of elevated temperature on the value of  $V_{\text{CE}(\text{SAT})}$ , the following experiments were performed.

To simulate a rise in the ambient temperature, the transistors were placed in a heated oil bath whose temperature was controlled at approximately  $10^{\circ}\text{C}$  intervals from room temperature to  $100^{\circ}\text{C}$  during measurement of VCE(SAT). Sufficient time was allowed for the transistor to reach a steady-state temperature between measurements.

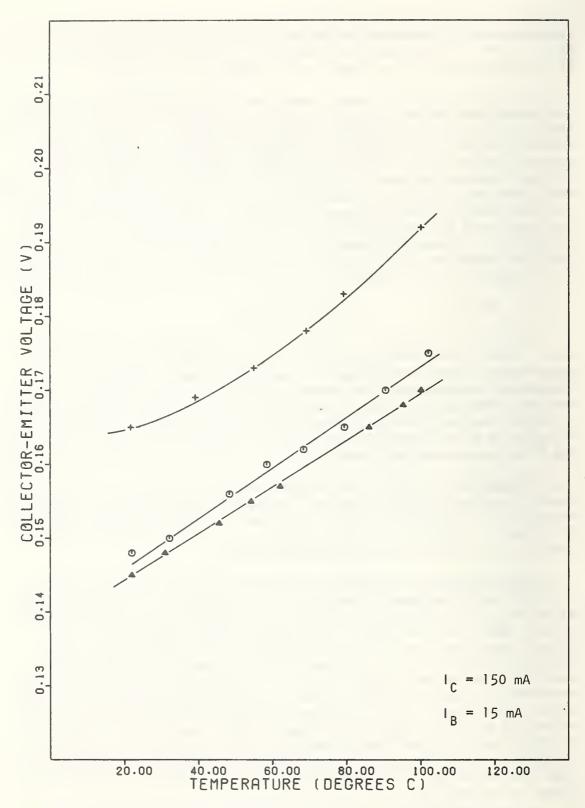

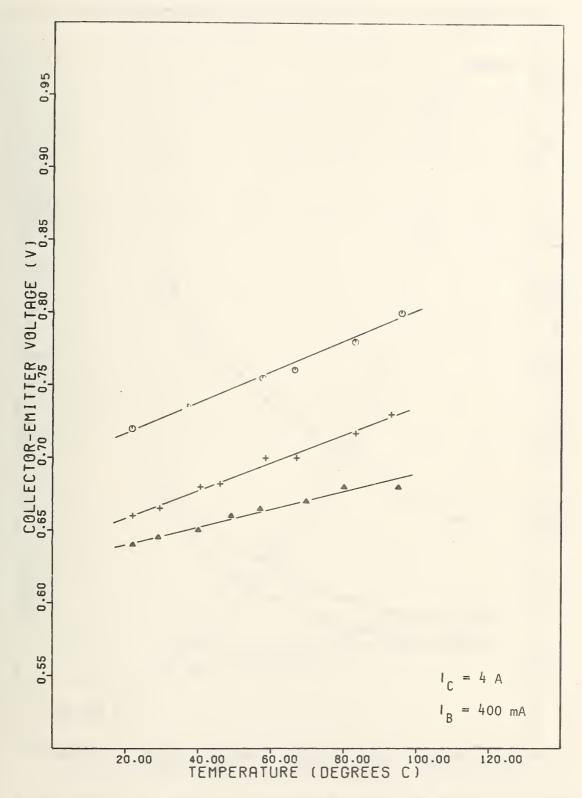

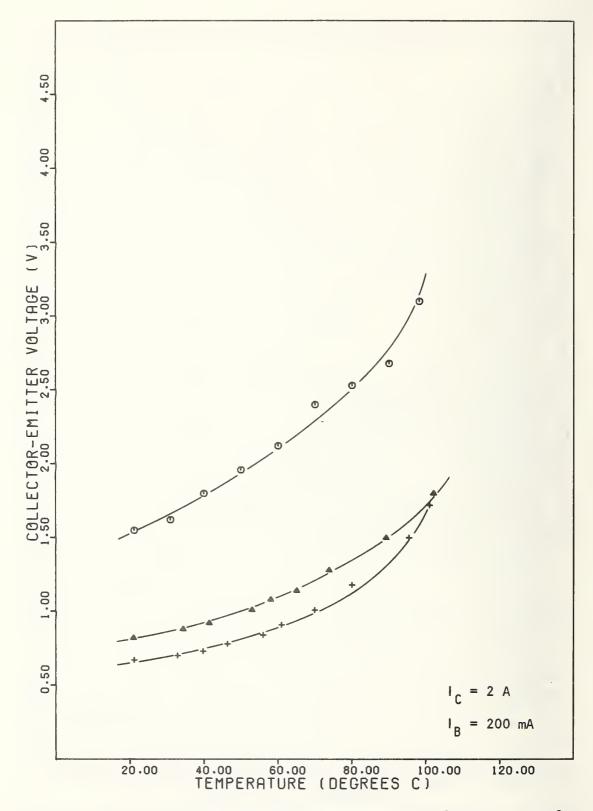

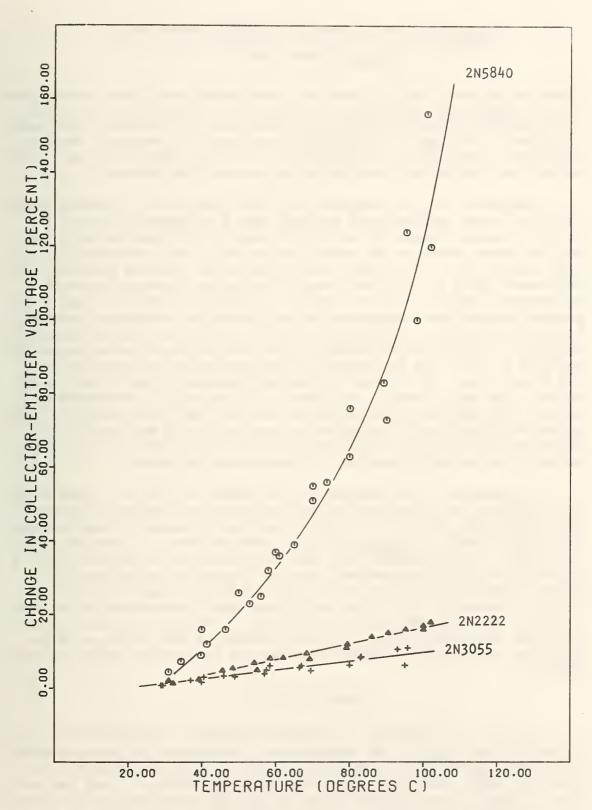

Figure 2 shows the measured value of  $V_{CE}(SAT)$  versus temperature for the three transistor types studied. In each case the base current was pulsed with a 2% duty cycle and a pulse width of 300  $\mu s$ . Both the 2N2222, figure 2a, and 2N3055, figure 2b, show a small increase in VCE(SAT) with temperature while the 2N5840, figure 2c, shows a much greater increase. It is to be expected that the 2N5840 would be much more sensitive to temperature since it is designed to have a very high breakdown voltage. In order to have a high breakdown voltage, the collector region has a very low doping level which provides a high collector series resistance with a high temperature coefficient. To compare the performance of the three transistor types, the data in figure 2 was plotted in figure 3 as percentage change in  $V_{CE}(SAT)$  from its value at room temperature as a function of temperature. In this case the percent change in  $V_{CE}(SAT)$  is

Figure 2a. Collector-emitter voltage as a function of temperature for each of the three 2N2222 transistors.

Figure 2b. Collector-emitter voltage as a function of temperature for each of the three 2N3055 transistors.

Figure 2c. Collector-emitter voltage as a function of temperature for each of the three 2N5840 transistors.

Figure 3. Typical change in collector-emitter voltage as a function of temperature for the three device types with the data averaged for the three samples of each type.

$$\frac{\text{V}_{\text{CE(SAT)}} \text{ (Elevated Temp.) - V}_{\text{CE(SAT)}} \text{ (Room Temp.)}}{\text{V}_{\text{CE(SAT)}} \text{ (Room Temp.)}}$$

These curves show that for practical measurement conditions, normal laboratory temperature conditions are adequate as deviations of less than  $10^{\circ}\text{C}$  result in changes in  $\text{V}_{\text{CE}(\text{SAT})}$  of less than 5%. However, with some transistor types when a very precise measurement is required, ambient temperature changes can be significant. For this reason, the method requires that the ambient temperature be measured and recorded.

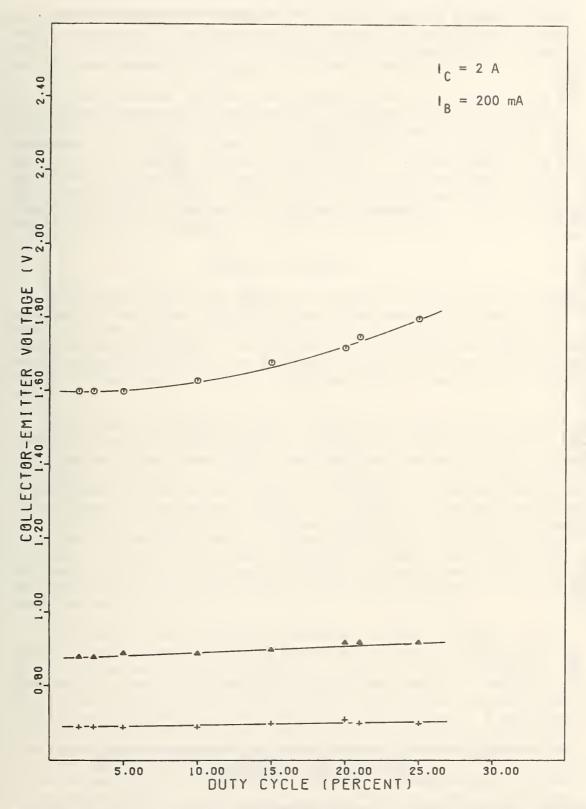

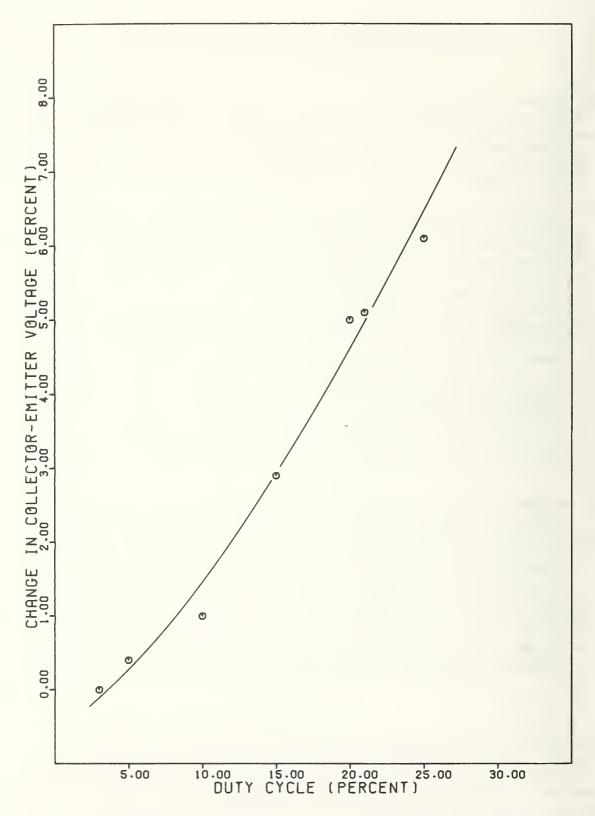

Examination of the manufacturer's specified value of thermal resistance for these devices would indicate that a temperature rise of two or three degrees Celsius at most would result from junction heating at the low power levels of the saturation region if the transistor is properly mounted with a heat-sink. According to the previous measurements, this would yield very little change in V<sub>CE(SAT)</sub>. However, since the measurement could be made in a condition where the transistor was not properly mounted on a heat-sink, it was decided to determine the effect of junction heating. Also examined was the effect on the measurement of VCE(SAT) of errors in the setting of the duty cycle, from the normal value of 2% to 25%. The duty cycle is the fraction of the cycle in which the pulse is on. It is given by the pulse width divided by the period of the cycle and is usually expressed as a percentage. Since the duty cycle is dependent on both the pulse width and the pulse repetition rate, errors in either can be expressed as an error in the duty cycle. The measurement of VCE(SAT) versus duty cycle was made only on the 2N5840 since it was the most sensitive to temperature variation.

The results of the measurements are shown in figure 4. Figure 4a shows  $V_{CE(SAT)}$  as a function of duty cycle with a fixed pulse width of 300 µs for each of the three devices measured. Figure 4b shows average percentage change in  $V_{CE(SAT)}$  for the three devices as a function of duty cycle. It is apparent that the duty cycle can be increased from 2 to 20 percent with the measured value of  $V_{CE(SAT)}$  changing only by 5%. Errors in setting the duty cycle or pulse width for small deviations from the nominal 2% duty cycle and 300-µs pulse width would not be significant. However, the method allows that other values be used if required by the specification. If other values of duty cycle and pulse width are to be used, the possible effect of temperature should be considered.

#### CURRENT EFFECTS

The effect of both the base and the collector currents on the measured value of  $V_{CE(SAT)}$  was investigated. Variations in these currents affect the measurement in two ways. First, a change in collector current will alter the  $I_{CC}$  term of the saturation voltage. This can produce a change in the measured value of  $V_{CE(SAT)}$  approximately proportional to the change in collector current. Second, changing either current can cause the transistor to operate in the active region instead of the saturation region. This will increase the measured value of  $V_{CE}$  by sev-

Figure 4a. Collector-emitter voltage as a function of duty cycle for each of the three 2N5840 transistors.

Figure 4b. Typical change in collector-emitter voltage as a function of duty cycle averaged for the three 2N5840 transistors.

eral hundred percent for changes in  $I_C$  of only tens of percent. Obviously, this value of collector-emitter voltage is not  $V_{CE(SAT)}$ . Assuring that the transistor is indeed operating in the saturation region during the measurement of  $V_{CE(SAT)}$  is of utmost importance.

As was indicated earlier, the definition of saturation is when both the collector-base and the emitter-base junctions are forward-biased. In practice the bias conditions to assure saturation are difficult to determine. It is more convenient to observe the gain to determine saturation. The d-c common emitter current gain,  $\beta$ , is the ratio of  $I_C$  to  $I_B$ . When the transistor is operating in the saturation region, this ratio is referred to as the forced gain, since both  $I_C$  and  $I_B$  are set in order to force the transistor to operate in saturation. It is convenient to consider a transistor to be in saturation if

# $\beta_{\text{forced}} << \beta_{\text{active}}$

Measurements were made of  $V_{\rm CE}$  as a function of base and collector currents for the three transistor types. The base and collector currents were sensed with a current transformer, the output of which was viewed on an oscilloscope. As outlined in the method, the current could have been measured by using an oscilloscope with a differential input to measure voltage across resistors in series with the base and the collector.

The results of varying  $I_C$  with  $I_B$  fixed are shown for the 2N2222 in figure 5a, for the 2N3055 in figure 5b, and the 2N5840 in figure 5c. In each case the value chosen for  $I_B$  was the value required in the detailed military specification. The value required for  $I_C$  in that specification is indicated by an arrow in each case. The data are combined in figure 6 which shows the percentage change in  $V_{CE}$  versus percentage change in  $I_C$  for the three transistor types. Each data point represents the average value for the three devices sampled. Similar curves of  $V_{CE}$  versus  $I_B$ , with  $I_C$  constant, are shown in figure 7. Figure 8 shows the results combined. Again, in each case, the value which was fixed for  $I_C$  is from the detailed military specification and the  $I_B$  value required in that specification is noted.

The results show that  $V_{CE}$  is sensitive to both  $I_C$  and  $I_B$  in most cases. Errors in measuring these currents can result in significant errors in the measured value of  $V_{CE(SAT)}$ . For this reason the method stresses the necessity of making accurate measurements of these currents. The portion of the curves where the slope is very steep represents operation of the transistor in or very near the active region. A measurement of  $V_{CE}$  here is not of  $V_{CE(SAT)}$ . When  $I_B$  and  $I_C$  (or the forced  $\beta$ ) are selected in the specification for this method, care should be taken so that this measurement is made well within the saturation region so that errors in setting the currents will not cause the measurement to be made in the active region. For the three transistor types used in this report, the value of forced  $\beta$  given in the detailed specification of the military standard is 10 in each case. That is, the  $V_{CE(SAT)}$  measurement is made with an  $I_C$  to  $I_B$  ratio of 10. This is the same value chosen for

Figure 5a. Collector-emitter voltage as a function of collector current with a fixed base current of 15 mA for each of the three 2N2222 transistors.

Figure 5b. Collector-emitter voltage as a function of collector current with a fixed base current of 400 mA for each of the three 2N3055 transistors.

Figure 5c. Collector-emitter voltage as a function of collector current with a fixed base current of 200 mA for each of the three 2N5840 transistors.

Figure 6. Typical change in collector-emitter voltage as a function of change in collector current.

Figure 7a. Collector-emitter voltage as a function of base current with a fixed collector current of 150 mA for each of the three 2N2222 transistors.

Figure 7b. Collector-emitter voltage as a function of base current with a fixed collector current of 4 A for each of the three 2N3055 transistors.

Figure 7c. Collector-emitter voltage as a function of base current with a fixed collector current of 2 A for each of the three 2N5840 transistors.

Figure 8. Typical change in collector-emitter voltage as a function of change in base current.

nearly every transistor for which there is a detailed military specification. It is also the ratio commonly given on manufacturer's specification sheets. In our case, for the 2N2222 which has a  $\beta$  in the active region in excess of 100, the condition for saturation is easily met with a forced  $\beta$  of 10. Also, for the 2N3055, which has a normal  $\beta$  of about 50, the condition is satisfied over a wide range of currents. For the 2N5840, however, which has a minimum specified gain of only 10, using a forced  $\beta$  of 10 is operating very near the active region.

To illustrate the effect of forced  $\beta$  on the measurement of VCE(SAT), an investigation was made into the effect of varying this factor. Figure 9 shows VCE as a function of IC for different values of forced  $\beta$ . It can be seen that as the forced  $\beta$  approaches the normal  $\beta$  of the transistor, small variations in IC give increasingly larger variations in VCE. If the measurement point is on one of these steep curves, precise measurement of VCE is difficult and it is doubtful whether the results represent VCE(SAT). It is not the intent of the method to describe how to choose the forced  $\beta$  of the specification. Since it is very important, the method gives guidelines for its selection and outlines a test which can be made to determine if the selection provides operation in the saturation region.

#### OTHER IMPORTANT PARAMETERS

There are other practical considerations for measuring VCE(SAT) particularly in power transistors where the collector currents used can be many amperes so that even a small series resistance in the voltage measuring circuit can be a serious source of error. The use of Kelvin connections, such as illustrated in figure 10 for a transistor in a TO-3 package, can eliminate most of these series resistance problems. With Kelvin connections the voltage measuring circuit is separated from the current driving circuit. The voltage measurement is made with a very high impedance instrument so that there is a negligible amount of current in that portion of the circuit. There is a separate set of leads to which the current driving circuit is attached. If there is an extraneous resistance in the voltage measuring circuit, the voltage drop across it is negligible. If there is an extraneous resistance in the current driving circuit, the voltage drop across it is not involved in the voltage measurement and therefore will not lead to an error in measuring V<sub>CE</sub>(SAT):

Note in figure 10 that Kelvin connections are made only to the emitter and collector leads. No voltage measurement is made in the base circuit so that Kelvin connections are not required.

The method requires Kelvin connections to be made on the collector and emitter leads for all types of transistors tested. There are perhaps transistor types which have a high  $V_{\text{CE}(SAT)}$  at a low collector current for which Kelvin connections are not essential. It is difficult to incorporate into the method a means of judging when to use Kelvin connections since the possible size of an extraneous resistance is not known. Since the majority of transistor types require Kelvin connections in any

Figure 9a. Collector-emitter voltage as a function of collector current for different values of forced  $\beta$  for a 2N2222 transistor.

Figure 9b. Collector-emitter voltage as a function of collector current for different values of forced  $\beta$  for a 2N3055 transistor.

Figure 9c. Collector-emitter voltage as a function of collector current for different values of forced  $\beta$  for a 2N5840 transistor.

Figure 10. Illustration of Kelvin connections.

case, it is more appropriate to require their use on all transistor types.

The effect of another type of extraneous resistance is not correctable by the use of Kelvin connections. These are series resistances that occur in the circuit between the transistor and the point where the voltage sensing connection is made. The current provided by the current driving circuit will cause a voltage drop across such a resistance which will be measured by the voltage measuring circuit as part of  $V_{\rm CE}({\rm SAT})$ . An example of such a resistance is the resistance of the leads of the transistor. For this reason, the method requires that contact be made reproducibly to the transistor within 3 mm of the transistor case. Another source of resistance is contact resistance due to poor or dirty contacts. The method requires that the transistor holder have good quality contacts and that they be kept clean.

Another source of error in the measurement of  $V_{CE}(SAT)$  is variations in the measurement circuit itself. The current levels used, particularly for power transistors, require considerable power dissipation in the resistors in the collector circuit. Care should be taken to select resistors that are capable of handling this power without changing resistance. In the pulsed method, a temperature drift in the resistors  $R_B$  and  $R_C$  could cause serious error in the measurement of  $V_{CE}(SAT)$  because the measurement would be made at the wrong values of  $I_B$  and  $I_C$ .

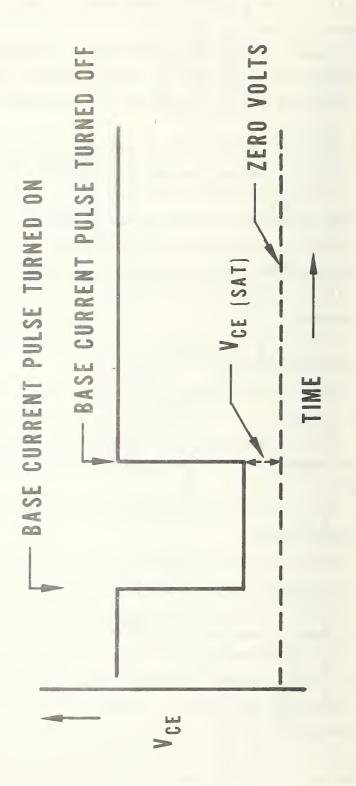

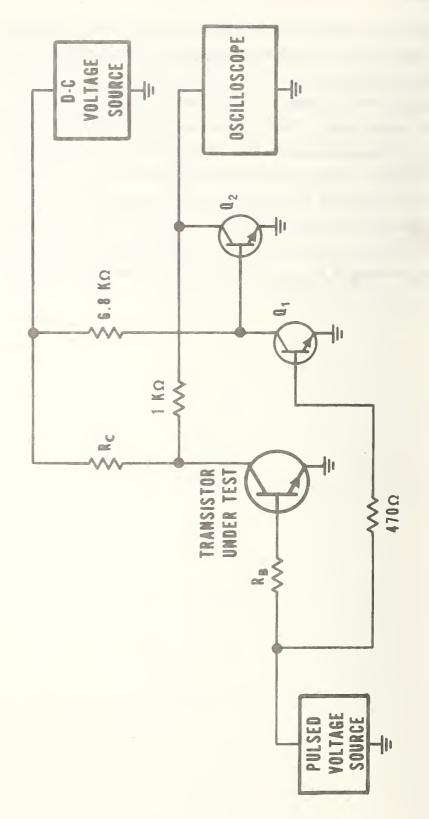

When the pulsed method is used, the voltage measurement of  $V_{\text{CE}(SAT)}$  must be made with an instrument capable of measuring the voltage of one portion of a pulse with respect to the ground potential. See figure 3 in the method. This measurement can be made with an oscilloscope if it is capable of accurately following the pulse from the high level which occurs when the current pulse is off to the low level of  $V_{\text{CE}(SAT)}$  when the current pulse is on. If, however, the amplifiers in the oscilloscope saturate, an erroneous measurement of  $V_{\text{CE}(SAT)}$  will be made. One way to avoid this is by application of a clamping circuit at the input of the oscilloscope. The effect of this circuit is to lower the voltage during the time the current pulse is off so that it is similar in magnitude to the value of  $V_{\text{CE}(SAT)}$  when the current pulse is on. An oscilloscope can easily follow the new pulse shape without saturating. An example of such a circuit is shown in Appendix X2 of the method.

A clamping circuit similar to that shown was used in the  $V_{CE}(SAT)$  measurements described. In order to determine if the addition of the clamping circuit caused error in the measured value of  $V_{CE}(SAT)$ , the current was measured in the  $1000-\Omega$  resistor. It was found to be less than 1  $\mu A$  during the time the base current pulse was on and the  $V_{CE}(SAT)$  measurement was being made. Therefore, the clamping circuit did not cause a measurable extraneous voltage drop to occur as part of  $V_{CE}(SAT)$ .

#### SUMMARY

A method for the measurement of  $V_{\rm CE(SAT)}$  has been outlined and discussed. It was found that the most important factor in the measurement

of  $V_{CE(SAT)}$  was the selection of the forced  $\beta$ . Precise measurement of base and collector currents is necessary. Small temperature changes are usually not important. The use of Kelvin connections to eliminate errors due to extraneous resistances is very important. Short lead lengths on the test transistors and good quality connections and contacts should be maintained. Good quality circuit components with adequate power rating should be used.

#### ACKNOWLEDGMENT

D. L. Blackburn, G. J. Rogers, and T. F. Leedy have provided useful comments and suggestions in the preparation of this report.

#### REFERENCES

- 1. JEDEC Recommendations for Letter Symbols, Abbreviations, Terms, and Definitions for Semiconductor Device Data Sheets and Specifications, JEDEC Publication No. 77A, p. D1 (March 1974).

- 2. Ebers, J. J., and Moll, J. L., Large-Signal Behavior of Junction Transistors, *Proc. IRE* 42, 1761-1772 (1954).

# METHODS TO MEASURE TRANSISTOR COLLECTOR-EMITTER SATURATION VOLTAGE

Document No.:

Draft No.: 1

Date: June 1, 1977

Prepared by: K. O. Leedy

(301) 921-3625

#### 1. Scope

- 1.1 These methods cover tests to determine transistor collector-emitter saturation voltage  $V_{\text{CE}(\text{SAT})}$  under specified conditions.

- 1.2 The d-c method is applicable at currents low enough to produce negligible heating in the junction.

- 1.3 The pulse method is applicable at high currents which would cause significant heating in the junction if not pulsed.

- 1.4 Before this test method can be implemented, test conditions which are appropriate for the transistor type to be measured must be selected and agreed upon by the parties to the test. Conditions will vary from one transistor type to another, and are determined in part by the intended application of the transistor. The d-c condition chosen should permit continuous operation of the device under test. The pulsed method should permit repetitive operation of the device under test. The following test conditions must be specified:

- 1.4.1 Choice of either d-c or pulse method,

- 1.4.2 Permissible range of ambient temperature if other than nominally 20°C,

- 1.4.3 Collector current  $I_{C}$  at which the measurement is to be made,

- 1.4.4 Base current  $I_{\rm R}$  at which the measurement is to be made, and

- 1.4.5 Pulse duration and duty cycle of current pulse if other than 300  $\mu s$  and 2%.

### 2. Summary of Methods

2.1 The base and collector currents of the transistor under test are each in turn adjusted to be at a specified value. The collectoremitter voltage is then measured.

# 3. Significance and Use

3.1 The collector-emitter saturation voltage of a transistor is a basic parameter of a transistor included in purchase specifications. The saturation voltage can be used for design purposes to predict the performance of a transistor used in saturated switching applications, such as in d-c to a-c power inverters, chopping circuits, and logic circuits as well as other circuits. Differences in  $V_{\text{CE}(\text{SAT})}$  before and after irradiation are a measure of radiation damage in the transistor.

# 4. Description of Terms

- 4.1 <u>collector-emitter saturation voltage</u> of a transistor, the voltage developed between the collector and emitter when the transistor is operated in the saturation region.

- 4.2 <u>saturation region</u> a base-current and a collector-current condition resulting in both the emitter-base and the collector-base junction being forward biased.

# 5. Interferences

- 5.1 During the test, care must be taken to maintain the ambient temperature within the specified range. Deviations may invalidate test results.

- 5.2 Care must be taken in the selection of  $I_C$  and  $I_B$  for the test to assure that the transistor is operating in the saturation region. Generally, when in saturation the ratio  $I_C$  to  $I_B$  is less than one tenth the gain of the transistor in the active region for the same base current. If a suitable ratio is not maintained, the test results may be invalid. A method for determining if a transistor is in saturation is given in Appendix X1.

### d-c Method

# 6. Apparatus

- 6.1 <u>Transistor Test Fixture</u> fixture to attach the transistor to be tested to the test circuit. Contacts shall be clean and of good quality. Kelvin connections shall be made to the collector and emitter leads. Electrical contact of the voltage measuring leads to collector and emitter leads shall be made to the transistor leads within 3 mm of the transistor case.

- 6.2 Voltmeter  $V_1$  voltmeter with an input impedance greater than  $100\frac{V_{CE(SAT)}}{I_C}$  capable of measuring d-c voltage in the range of the

- anticipated  $V_{\text{CE(SAT)}}$  with a full scale accuracy of  $\pm 0.5\%$  or better.

- 6.3 Ammeter  $A_1$  d-c ammeter capable of measuring current in the range of the specified base current with a full scale accuracy of  $\pm 0.5\%$  or better.

- 6.4 Ammeter  $A_2$  ammeter capable of measuring current in the range of the specified collector current with a full scale accuracy of  $\pm 0.5\%$  or better.

- 6.5 <u>Voltage Sources</u> d-c voltage sources (sources 1 and 2, Fig. 1) meeting the following specifications:

- 6.5.1 Stable to within  $\pm 0.25\%$  of the set voltage,

- 6.5.2 Noise and ripple less than 0.5% of the output voltage, and

- 6.5.3 Adjustable over a nominal range of zero to 30 volts.

- 6.6 Resistors resistors ( $R_{\mbox{\footnotesize{B}}}$  and  $R_{\mbox{\footnotesize{C}}}$ ) which meet the following requirements:

- 6.6.1  $R_B$  shall have a resistance of approximately  $R_B = \frac{20}{I_B} \, \Omega$  where  $I_B$  is the specified base current in amperes. The resistance shall be known to within 1%. It shall be capable of dissipating at least  $I_B^{\ 2}R_B^{\ 2}$  watts. It shall have a temperature coefficient of resistance less than 0.1%/°C.

- 6.6.2  $R_C$  shall have a resistance of approximately  $R_C = \frac{20}{I_C} \Omega$  where  $I_C$  is the specified collector current in amperes. The resistance shall be known to within 1%. It shall be capable of dissipating at least  $I_C^2 R_C$  watts. It shall have a temperature coefficient of resistance less than 0.1%/°C.

- 6.7 <u>Temperature Measuring Instrument</u> instrument to measure the ambient temperature with an accuracy of  $\pm 2\%$  in the range of the specified ambient temperature.

# 7. Sampling

This method determines the properties of a single specimen. If sampling procedures are used to select devices for test, they must be agreed upon in advance by the parties to the test.

# 8. <u>Procedure</u>

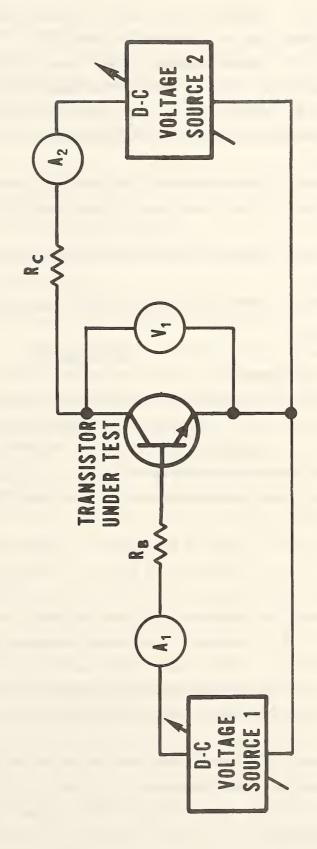

- 8.1 Assemble the circuit shown in Fig. 1.

- 8.2 Set both voltage sources at zero volts and insert transistor to be tested into transistor test fixture.

- 8.3 Measure and record the ambient temperature in the vicinity of the test fixture.

Figure 1. Test circuit for use with the d-c method.

- 8.4 Adjust voltage source 1 until the base current equals the specified value as measured on ammeter  ${\rm A_1}$ .

- 8.5 Adjust voltage source 2 until the collector current equals the specified value as measured on ammeter  $A_2$ .

- 8.6 Check ammeter  $\mathbf{A}_1$  to see if it still reads the specified value and, if not, readjust voltage source 1 to obtain the specified value.

- 8.7 Check ammeter  $\mathbf{A}_2$  to see if it still reads the specified value and, if not, readjust voltage source 2 to obtain the specified value.

- 8.8 Repeat 8.6 and 8.7 until no further readjustments are required.

- 8.9 Measure and record the voltage on voltmeter  $\mathbf{V}_1$ . This is  $\mathbf{V}_{\text{CE(SAT)}}$ .

## Pulse Method

# 9. Apparatus

- 9.1 In addition to items 6.1, 6.6, 6.7 and voltage source 2 described in 6.5, the following apparatus is required.

- 9.1.1 <u>Pulsed Voltage Source</u> Pulsed voltage source which meets the following requirements:

- 9.1.1.1 Adjustable output which is sufficient to provide  $I_{\mbox{\footnotesize B}}$  required,

- 9.1.1.2 Polarity selectable as either positive or negative,

- 9.1.1.3 Rise and fall times of less than 0.1 times the pulse width used,

- 9.1.1.4 Droop of less than 5%, and

- 9.1.1.5 Capable of producing the pulse width of 300 µs with a duty cycle of 2% or other pulse width and duty cycle if specified.

- 9.1.2 <u>Current Measuring Equipment</u> equipment for measuring base current and collector current described in 9.1.2.1 and 9.1.2.2 or 9.1.2.3.

- 9.1.2.1 Current probe and an amplifier which used together meet the following requirements:

- 9.1.2.1.1 Rise time less than or equal to 0.1 times the pulse width used,

- 9.1.2.1.2 Accuracy ±3% or better,

- 9.1.2.1.3 Sensitivity of 0.1 V/A or better,

- 9.1.2.1.4 Core saturation rating exceeding the product of the current to be measured and its pulse width, and

- 9.1.2.1.5 Low-frequency response such that a square pulse of the width used in the test results in a negative tilt of less than 3% in the pulse interval.

- 9.1.2.2 <u>Oscilloscope 1</u> general-purpose laboratory oscilloscope meeting the following specification:

- 9.1.2.2.1 Bandwidth of d-c to 10 MHz minimum,

- 9.1.2.2.2 Input resistance greater than or equal to 100 times the resistance across which it is measuring,

- 9.1.2.2.3 Deflection factors covering at least the range from 5 mV/div to 1 V/div.

- 9.1.2.3 Oscilloscope 2 general-purpose laboratory oscilloscope as described in 9.1.2.2 with the following additional requirements:

- 9.1.2.3.1 Capability of differential measurements with both inputs isolated from test circuit common, and

- 9.1.2.3.2 Common mode rejection ratio of 20 dB minimum.

- 9.1.3 <u>Voltage Measuring Means</u> instrument for measuring and displaying the voltage waveform of nominally square pulses having the specified pulse width and duty cycle (see 9.1.1.5) and with a voltage range of zero to 20 V.

# 10. Sampling

10.1 This method determines the properties of a single specimen. If sampling procedures are used to select devices for test, they must be agreed upon in advance by the parties to the test.

# 11. Procedure

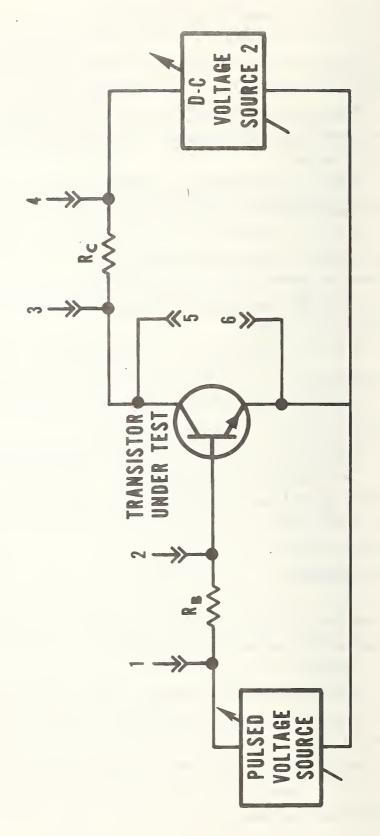

- 11.1 With voltage source 2 set at zero volts, assemble the circuit shown in Fig. 2. Set the pulsed voltage source to have a pulse width of 300  $\mu$ s and a duty cycle of 2% unless otherwise specified.

- 11.2 Insert transistor to be tested into transistor test fixture.

- 11.3 Measure and record the ambient temperature in the vicinity of the test fixture.

- 11.4 Set the base and collector currents equal to the specified

Figure 2. Test circuit for use with the pulsed method.

values using either 11.4.1 or 11.4.2.

- 11.4.1 Use a current transformer to set the base and collector currents as follows:

- 11.4.1.1 Attach the current probe and amplifier combination to oscilloscope 1 and position the current probe to monitor the current in  $R_{\rm p}$ .

- 11.4.1.2 Adjust the pulsed voltage source to obtain the specified  $\mathbf{I}_{\mathrm{R}}.$

- 11.4.1.3 Position the current probe to monitor the current in  $R_{\rm C}$ .

- 11.4.1.4 Adjust the voltage source 2 to obtain the specified  $I_{\rm C}$ .

- 11.4.1.5 Remeasure the current in  $R_B$ . If other than specified  $I_B$ , readjust the pulsed voltage source to obtain specified  $I_R$ .

- 11.4.1.6 Remeasure the current in R  $_{\rm C}$ . If other than specified I  $_{\rm C}$ , readjust voltage source 2 to obtain specified I  $_{\rm C}$ .

- 11.4.1.7 Repeat 11.4.1.5 and 11.4.1.6 until no further readjustment is necessary.

- 11.4.2 Use oscilloscope 2 to set the base and collector currents as follows:

- 11.4.2.1 Calculate and record  $V_B = I_B R_B$  where  $I_B$  is the required base current.

- 11.4.2.2 Adjust the pulsed voltage source to obtain the required  ${\bf V}_{\bf B}$  as measured with oscilloscope 2 connected differentially across points 1 and 2.

- 11.4.2.3 Calculate and record  $V_C = I_C R_C$  where  $I_C$  is the required collector current.

- 11.4.2.4 Adjust voltage source 2 to obtain the required  $\rm V_{C}$  as measured with oscilloscope 2 connected differentially across points 3 and 4.

- 11.4.2.5 Remeasure the voltage across points 1 and 2. If this is other than  $\rm V_R$ , readjust the pulsed voltage source to obtain  $\rm V_R$ .

- 11.4.2.6 Remeasure the voltage across points 3 and 4. If this is other than  $V_{\rm C}$ , readjust voltage source 2 to obtain  $V_{\rm C}$ .

- 11.4.2.7 Repeat 11.4.2.5 and 11.4.2.6 until no further readjustment is necessary.

- 11.5 With the voltage measuring means described in 9.1.3 connected across points 5 and 6, observe the voltage waveform which is similar to that shown in Fig. 3. Measure and record the voltage difference,

Figure 3. Voltage waveform as observed with an oscilloscope in the pulsed method.

V, indicated as  $V_{CE(SAT)}$  in the figure.

Note 1 - Since the voltage difference to be measured is small compared to the pulse height, some difficulty may be encountered in making the measurement of  $V_{\text{CE}(\text{SAT})}$ , depending on the detailed performance characteristics of the equipment used. Appendix X2 describes a clamping circuit which lowers the  $V_{\text{CE}}$  pulse height and details a procedure found satisfactory for its use.

# 12. Report

- 12.1 The report for d-c Method shall contain the following:

- 12.1.1 Name of person performing the test,

- 12.1.2 Date of the test,

- 12.1.3 Device type and identification of the transistor tested,

- 12.1.4 Ambient temperature,

- 12.1.5 Resistance of resistors  $R_B$  and  $R_C$ ,

- 12.1.6 Base and collector currents used in the test, and,

- 12.1.7 Measured value of the collector-emitter saturation voltage.

- 12.2 The report for Pulse Method shall contain the following in addition to items 12.1.1 to 12.1.7:

- 12.2.1 Pulse width, µs, and duty cycle, percent, and

- 12.2.2 Measured values of  $V_R$  and  $V_C$ .

# 13. Precision

No interlaboratory precision data is available at this time.

#### APPENDIX X1

X1.1 In some applications it is the intention to measure the transistor collector-emitter voltage for a given bias regardless of whether the transistor is operating in the saturation region or not. However, if a measurement of the actual  $\rm V_{CE(SAT)}$  is required, one technique that may be used to assure that, with the specified values of  $\rm I_B$  and  $\rm I_C$ , the transistor is operating in the saturation region is to first measure  $\rm V_{CE(SAT)}$  as indicated. Then repeat the measurement with a base current equal to  $\rm 2I_B$ . If the measured value of  $\rm V_{CE(SAT)}$  changes by more than 25%, the transistor was not in saturation. In order to determine values of  $\rm I_B$  and  $\rm I_C$  such that the transistor is operating in the saturation region, it is necessary to plot  $\rm V_{CE}$  as a function of  $\rm I_C/I_B$  with  $\rm I_B$  or  $\rm I_C$  fixed. Suitable current values can then be chosen by looking for the flat portion of this curve.

#### APPENDIX X2

X2.1 One technique that may be used to assist in measuring  $V_{\text{CE}(\text{SAT})}$  (see Note 1) is the use of a clamping circuit shown connected to the measuring circuit in Fig. X2.1. This clamping circuit acts to maintain the voltage across  $Q_2$  near the anticipated level of the  $V_{\text{CE}(\text{SAT})}$  of the transistor under test. When the base-current pulse occurs, transistor  $Q_1$  turns on which then turns off transistor  $Q_2$ . The resistor values shown are nominal. Transistors  $Q_1$  and  $Q_2$  can be any transistors whose  $V_{\text{CE}(\text{SAT})}$  is in the range of the  $V_{\text{CE}(\text{SAT})}$  of the transistor to be tested. It is convenient to use transistors of the same type as is being tested. With the clamping circuit connected as shown in Fig. X2.1, use the oscilloscope to measure  $V_{\text{CE}(\text{SAT})}$  and record the measured value.

Figure X2.1. Measuring circuit with clamping circuit attached.

#### DISTRIBUTION

Defense Communication Engineer Center 1860 Wiehle Avenue Reston, VA 22090 ATTN R410 James W. McLean

Director

Defense Communications Agency

Washington, D.C. 20305

ATTN Code 930 Monte T. Burgett, Jr.

Defense Documentation Center Cameron Station Alexandria, VA 22314 ATTN TC (12 copies)

Director

Defense Electronic Supply Center

Dayton, OH 45444

ATTN ECS Robert E. Cooper

ATTN ECS Joseph Dennis

Director

Defense Nuclear Agency

Washington, D.C. 20305

ATTN STTL Tech Library (3 copies)

ATTN STVL

ATTN DDST

ATTN RAEV

ATTN RAEV

ATTN RAEV Maj. W. Adams (2 copies)

Dir of Defense Rsch & Engineering Department of Defense Washington, D.C. 20301 ATTN DDR&E(OS)

Commander Field Command Defense Nuclear Agency Kirtland AFB, NM 87115 ATTN FCPR

Director

Interservice Nuclear Weapons School

Kirtland AFB, NM 87115

ATTN Document Control

Director Joint Strat TGT Planning Staff JCS Offutt AFB Omaha, NB 68113 ATTN JLTW-2

Chief Livermore Division Fld Command DNA Lawrence Livermore Laboratory P.O. Box 808 Livermore, CA 94550 ATIN FCPRI Project Manager

Army Tactical Data Systems

U.S. Army Electronics Command

Fort Monmouth, NJ 07703

ATTN Dwaine B. Huewe

Commander

BMD System Command

P.O. Box 1500

Huntsville, AL 35807

ATTN BDMSC-TEN Noah J. Hurst

Commander

Frankford Arsenal

Bridge and Tacony Streets

Philadelphia, PA 19137

ATTN SARFA-FCD Marvin Elnick

Commander

Harry Diamond Laboratories

2800 Powder Mill Road

Adelphi, MD 20783

ATTN DRXDO-EM R. Bostak

ATTN DRXDO-RC Robert B. Oswald, Jr.

ATTN DRXDO-EM J. W. Beilfuss

ATTN DRXDO-EM Robert E. McCoskey

ATTN DRXDO-NP Francis N. Wimenitz

ATTN DRXDO-RBG Joseph Halpin

ATTN DRXDO-RB Joseph R. Miletta

ATTN DRXDO-TI Tech Lib

Commanding Officer

Night Vision Laboratory

U.S. Army Electronics Command

Fort Belvoir, VA 22060

ATTN Capt. Allan S. Parker

Commiander

Picatinny Arsenal

Dover, NJ 07801

ATTN SMUPA-ND-D-E

ATTN SMUPA-ND-W

Commander

Redstone Scientific Information Ctr

U.S. Army Missile Command

Redstone Arsenal, AL 35809

ATTN Chief, Documents (3 copies)

Secretary of the Army Washington, D.C. 20310 ATTN ODUSA or Daniel Willard

Commander TRASANA White Sands Missile Range, NM 88002 ATTN ATAA-EAC Francis N. Winans

Chief

Chief

U.S. Army Communications Sys Agency

Fort Monmouth, NJ 07703

ATTN SCCM-AD-SV Library

Maval Electronic Systems Cmd Hqs

Washington, D.C. 20360

ATTN CODE 50451

ATTN ELEX 05323 Cleveland F. Watkins

U.S. Army Electronics Command Fort Monmouth, NJ 07703 ATTN DRSEL-GG-TD W. R. Werk ATTN DRSEL-TL-IR Edwin T. Hunter ATTN DRSEL-PL-ENV Hans A. Bomke

Commander-in-Chief U.S. Army Europe and Seventh Army APO New York 09403 ATTN ODCSE-E AEAGE-PI

Commander

U.S. Army Materiel Dev & Readiness Cmd 5001 Eisenhower Avenue Alexandria, VA 22333 ATTN DRCDE-D Lawrence Flynn

Commander

U.S. Army Missile Command Redstone Arsenal, AL 35809 ATTN DRCPM-PE-EA Wallace O. Wagner ATTN DRCPM-LCEX Howard H. Henriksen

ATTN DRCPM-MDTI Capt. Joe A. Sims

Commander

Naval Surf ATTN DRSMI-RGD Victor W. Ruwe ATTN AMSI-RGP Victor W. Ruwe

Commander

U.S. Army Mobility Equip R&D Ctr Fort Belvoir, VA 22060 ATTN STSFB-MW John W. Bond, Jr. ATTN AMSEL-NV-SD J. H. Carter

Chief

U.S. Army Nuc and Chemical Surety Gp Bldg. 2073, North Area Ft. Belvoir, VA 22060

ATTN MOSG-ND Maj. Sidney W. Winslow Commanding Officer

Commander

U.S. Army Nuclear Agency Fort Bliss, TX 79916 ATTN ATCN-W LTC Leonard A. Sluga

Commander

U.S. Army Test and Evaluation Comd Aberdeen Proving Ground, MD 21005

Commander

White Sands Missile Range White Sands Missile Range, NM 88002 ATTN STEWS-TE-NT Marvin P. Squires ATTN Nuclear Effects Lab Ted F. Leura, Jr.

Commander

ATTN CODE 504511 Charles R. Suman ATTN PME 117-21

ATTN CODE 5032 Charles W. Neill

Director

Naval Research Laboratory Washington, D.C. 20375 ATTN CODE 2627 Doris R. Folen ATTN CODE 6601 E. Wolicki ATTN CODE 5216 Harold L. Hughes ATTN CODE 5210 John E. Davey ATTN CODE 6620 Bruce Faraday ATTN CODE 6627 Neal Wilsey

Commander

Naval Sea Systems Command Navy Department Washington, D.C. 20362 ATTN SEA-9931 Samuel A. Barham ATTN SEA-9931 Riley B. Lane

Naval Surface Weapons Center White Oak, Silver Spring, MD 20910 ATTN CODE WX21 Tech Lib ATTN CODE WASO John H. Malloy ATTN CODE 244 ATTN CODE 431 Edwin B. Dean ATTN CODE WA501 Navy Nuc Prgms Off ATTN CODE WA52 Fred Warnock

Commander

Naval Weapons Center China Lake, CA 93555 ATTN CODE 533 Tech Lib

Naval Weapons Support Center Crane, IN 47522 ATTN CODE 3073 James Ramsey ATTN CODE 3073 Joseph A. Munarin ATTN CODE 3073 Ron Pease

Army Test and Evaluation Comd

deen Proving Ground, MD 21005

ATTN DRSTE-EL Richard I. Kolchin

ATTN DRSTE-NB Russell R. Galasso

Director

Strategic Systems Project Office

Navy Department

Washington, D.C. 20376

ATTN NSP-27221 ATTN NSP-27331 Phil Spector ATTN NSP-2342 Richard L. Coleman ATTN NSP-230 David Gold

ATTN SP 2701 John W. Pitsenberger

Director SAMSO/DY Office of Naval Research Post Office Box 93960 800 N. Quincy Street Arlington, VA 22217 Worldway Postal Center Los Angeles, CA 90009 ATTN 220 David Lewis ATTN DYS Maj. Larry A. Darda ATTN AWSR Lt. Col. Cornelius H. McGuiness AF Aero-Propulsion Laboratory, AFSC Wright-Patterson AFB, OH 45433 SAMSO/IN ATTN POE-2 Joseph F. Wise Post Office Box 92960 Worldway Postal Center AF Institute of Technology, AU Los Angeles, CA 90009 Wright-Patterson AFB, OH 45433 ATTN IND I. J. Judy ATTN ENP Charles J. Bridgman SAMSO/MN AF Materials Laboratory, AFSC Norton AFB, CA 92409 Wright-Patterson AFB, OH 45433 ATTN MNNG Capt. David J. Strobel ATTN LTE ATTN MNNG ATTN MNNH AF Weapons Laboratory, AFSC Kirtland AFB, NM 87117 ATTN ELP TREE Section SAMSO/RS Post Office Box 92960 ATTN ELA Worldway Postal Center ATTN SAS Los Angeles, CA 90009 ATTN ELP Capt. John G. Tucker ATTN RSSE LTC Kenneth L. Gilbert ATTN SAT ATTN SAB SAMSO/SK ATTN ELPT John Mullis Post Office Box 92960 ATTN ELPT David Ferry Worldway Postal Center Los Angeles, CA 90009 ATTN SKF Peter H. Stadler AFTAC Patrick AFB, FL 32925 ATTN TFS Maj. Marion F. Schneider Commander-in-Chief Strategic Air Command Commander Offutt AFB, NB 68113 ATTN XPFS Maj. Brian G. Stephan ATTN NRI-STINFO Library Wright-Patterson AFB, OH 45433 ATTN ASD-YH-EX LTC Robert Leverette University of California Lawrence Livermore Laboratory Headquarters Electronic Systems Division (AFSC) P.O. Box 808 Hanscom AFB, MA 01731 ATTN DCD/SATIN IV Livermore, CA 94550 ATTN Tech Info Dept L-3 ATTN YSEV ATTN Lawrence Cleland L-156 ATTN Hans Kruger L-96 ATTN YWET ATTN Joseph E. Keller, Jr. L-125 Commander Foreign Technology Division, AFSC Wright-Patterson AFB, OH 45433 Los Alamos Scientific Laboratory P.O. Box 1663 ATTN ETET Capt. Richard C. Husemann Los Alamos, NM 87545 ATTN Doc. Cont. for J. Arthur Freed Commander Rome Air Development Center, AFSC Sandia Laboratories Griffiss AFB, NY 13440 ATTN RBRAC I. L. Krulac P.O. Box 5800 Albuquerque, NM 87115 ATTN RBRP Jack S. Smith ATTN DOC CON for 3141 Sandia Rpt Coll ATTN DOC CON for Org 2110 J. A. Hood ATTN RBRP Clyde Lane ATTN DOC CON for Org 1933 F. N. Coppage ATTN RBRP Joseph Brauer

Department of Commerce National Bureau of Standards Washington, D.C. 20234 ATTN Judson C. French, A357 Tech ATTN W. M. Bullis, A355 Tech ATTN K. F. Galloway, A327 Tech

Aerojet Electro-Systems Co Div Aerojet-General Corp P.O. Box 296 Azusa, CA 91702 ATTN Thomas D. Hanscome

Aeronutronic Ford Corporation Aerospace & Communications Ops Aeronutronic Div Fort & Jamboree Roads Newport Beach, CA 92663 ATTN Tech Info Section ATTN Ken C. Attinger

Aeronutronic Ford Corporation

Western Development Laboratories Div

3939 Fabian Way

Palo Alto, CA 94303

ATTN Samuel R. Crawford MS 531

Aerospace Corp

P.O. Box 92957

Los Angeles, CA 90009

ATTN Irving M. Garfunkel

ATTN J. Benveniste

ATTN Julian Reinheimer

ATTN S. P. Bower

ATTN W. Willis

AVCO Research & Systems Group 201 Lowell Street Wilmington, MA 01887 ATTN Research Lib A830, Rm 7201

The BDM Corp 1920 Aline Ave Vienna, VA 21180 ATTN T. H. Neighbors

The Bendix Corp Communication Division East Joppa Road - Towson Baltimore, MD 21204 ATTN Document Control

The Bendix Corp

Research Laboratories Div

Bendix Center

Southfield, MI 48076

ATTN Max Frank

ATTN Mgr Prgm Dev Donald J. Niehaus

The Bendix Corp

Navigation and Control Div

Teterboro, NJ 07608

ATTN George Gartner

The Boeing Company

P.O. Box 3707

Seattle, WA 98124

ATTN David L. Dye MS 87-75

ATTN Aerospace Library

ATTN Howard W. Wicklein MS 17-11

ATTN Robert S. Caldwell 2R-00

ATTN Carl Rosenberg 2R-00

ATTN Itsu Arimura 2R-00

Booz-Allen and Hamilton, Inc. 106 Apple Street New Shrewsbury, NJ 07724 ATTN Raymond J. Chrisner

California Inst. of Tech. Jet Propulsion Lab 4800 Oak Park Grove Pasadena, CA 91103 ATTN J. Bryden ATTN A. G. Stanley

Charles Start Draper Laboratory, Inc. 68 Albany Street Cambridge, MA 02139 ATTN Kenneth Fertig

Computer Sciences Corp 201 La Veta Drive, N.E. Albuquerque, NM 87108 ATTN Richard H. Dickhaut

Cutler-Hammer, Inc.

AIL Div

Comac Road

Deer Park, NJ 11729

ATTN Central Tech Files Anne Anthony

The Dikewood Corp 1009 Bradbury Drive, S.E. University Research Park Albuquerque, NM 87106 ATTN L. Wayne Davis

E-Systems, Inc.

Greenville Div

P.O. Box 1056

Greenville, TX 75401

ATTN Library 8-50100

Effects Technology, Inc. 5383 Hollister Avenue Santa Barbara, CA 93111 ATTN Edward John Steele

Fairchild Camera and Instrument Corp 464 Ellis Street Mountain View, CA 94040 ATTN Sec Dept for 2-233 David K. Myers

Fairchild Industries, Inc.

Sherman Fairchild Technology Ctr

2030l Century Boulevard

Germantown, MD 20767

ATTN Mgr Config Data & Standards

Garrett Corp P.O. Box 92248 Los Angeles, CA 90009 ATTN Robert E. Weir Dept 93-9

General Dynamics Corp Electronics Div Orlando Operations P.O. Box 2566 Orlando, FL 32802 ATTN D. W. Coleman

General Electric Company

Space Division

Valley Forge Space Center

Goddard Blvd King of Prussia

P.O. Box 8555

Philadelphia, PA 19101

ATTN Larry I. Chasen

ATTN John L. Andrews

ATTN Joseph C. Peden VFSC, Rm 4230M

General Electric Company

Re-entry & Environmental Systems Div

P.O. Box 7722

3198 Chestnut Street

Philadelphia, PA 19101

ATTN John W. Palchefsky Jr.

ATTN Robert V. Benedict

General Electric Company Ordnance Systems 100 Plastics Avenue Pittsfield, MA 01201 ATTN Joseph J. Reidl

General Electric Company

Tempo-Center for Advanced Studies

816 State Street (P.O. Drwr QQ)

Santa Barbara, CA 93102

ATTN M. Espig

ATTN DASIAC

ATTN Royden R. Rutherford

General Electric Company P.O. Box 1122 Syracuse, NY 13201 ATTN CSP 0-7 L. H. Dee General Electric Company

Aircraft Engine Group

Evendale Plant

Cincinnati, OH 45215

ATTN John A. Ellerhorst E 2

General Electric Company

Aerospace Electronics Systems

French Road

Utica. NY 13503

ATTN W. J. Patterson Drop 233

ATTN Charles M. Hewison Drop 624

General Electric Company - Tempo ATTN: DASIAC C/O Defense Nuclear Agency Washington, D.C. 20305 ATTN William Alfonte

Georgia Institute of Technology Georgia Tech Research Inst Atlanta, GA 30332 ATTN R. Curry

Grumman Aerospace Corp South Oyster Bay Road Bethpage, NY 11714 ATTN Jerry Rogers Dept 533

GTE Sylvania, Inc.

Electronics Systems Grp - Eastern Div

77 A Street

Needham, MA 02194

ATTN James A. Waldon

ATTN Charles A. Thornhill Librarian

ATTN Leonard L. Blaisdell

GTE Sylvania, Inc.

189 B Street

Needham Heights, MA 02194

ATTN H & V Group Mario A. Nurefora

ATTN Herbert A. Ullman

Gulton Industries, Inc.

Engineered Magnetics Division

13041 Cerise Avenue

Hawthorne, CA 90250

ATTN Engnmagnetics Div

Harris Corp

Harris Semiconductor Div

P.O. Box 883

Melbourne, FL 32901

ATTN Wayne E. Abare MS 16-111

ATTN Carl F. Davis MS 17-220

ATTN T. L. Clark MS 4040

Hazeltine Corp Pulaski Road Green Lawn, NY 11740 ATTN Tech Info Ctr M. Waite

Honeywell Inc.

Government and Aeronautical

Products Division

2600 Ridgeway Parkway

Minneapolis, MN 55413

ATTN Ronald R. Johnson A1622

Honeywell Inc.

Aerospace Division

13350 U.S. Highway 19

St. Petersburg, FL 33733

ATTN M.S. 725-J Stacey H. Graff

ATTN Harrison H. Noble M.S. 725-5A

Honeywell Inc.

Radiation Center

2 Forbes Road

Lexington, MA 02173

ATTN Technical Library

Hughes Aircraft Company

Centinela and Teale

Culver City, CA 90230

ATTN John B. Singletary MS 6-D133

ATTN Billy W. Campbell MS 6-E-110

ATTN Kenneth R. Walker MS D157

Hughes Aircraft Company

Space Systems Div

P.O. Box 92919

Los Angeles, CA 90009

ATTN Edward C. Smith MS A620

ATTN William W. Scott MS A1080

IBM Corp Route 17C Owego, NY 13827 ATTN Frank Frankovsky

IIT Research Institute 10 West 35th Street Chicago, IL 60616 ATTN Irving N. Mindel

Intl Tel & Telegraph Corp.

500 Washington Avenue

Nutley, NJ 07110

ATTN Alexander T. Richardson

IRT Corp

P.O. Box 81087

San Diego, CA 92138

ATTN R. L. Mertz

ATTN Ralph H. Stahl

ATTN Leo D. Cotter

ATTN MDC

ATTN John W. Harrity

ATTN J. L. Azarewicz

JAYCOR

205 S. Whiting Street, Suite 500

Alexandria, VA 22304

ATTN Robert Sullivan

ATTN Catherine Turesko

Johns Hopkins University

Applied Physics Laboratory

Johns Hopkins Road

Laurel, MD 20810

ATTN Peter E. Partridge

Kaman Sciences Corp P.O. Box 7463 Colorado Springs, CO 80933 ATTN Albert P. Bridges - ATTN Donald H. Bryce ATTN Jerry I. Lubell

Litton Systems, Inc.

Guidance & Control Systems Div

5500 Canoga Avenue

Woodland Hills, CA 91364

ATTN Val J. Ashby MS 67

ATTN John P. Retzler

Lockheed Missiles & Space Co., Inc. P.O. Box 504 Sunnyvale, CA 94088 ATTN Benjamin T. Kimura Dept 81-14 ATTN Edwin A. Smith Dept. 85-85 ATTN Dept 81-01 G. H. Morris ATTN L. Rossi Dept 81-64

ATTN Dept 85-85 Samual I. Taimuty

Lockheed Missiles and Space Company 3251 Hanover Street Palo Alto, CA 94304 ATTN Tech Info Ctr D/Coll ATTN John Crowley

LTV Aerospace Corp Vought Systems Division P.O. Box 6267 Dallas, TX 75222 ATTN Technical Data Center

LTV Aerospace Corp Michigan Division P.O. Box 909 Warren, MI 48090 ATTN Tech Lib

M.I.T. Lincoln Laboratory

P.O. Box 73

Lexington, MA 02173

ATTN Leona Loughlin Librarian A-082

Orlando Division

P.O. Box 5837

Orlando, FL 32805

ATTN Mona C. Griffith Lib MP-30

ATTN Jack M. Ashford MP-537

ATTN William W. Mras MP-413

ATTN Richard Gaynor

McDonnell Douglas Corp P.O. Box 516 St. Louis, MO 63166 ATTN Tech Lib ATTN Tom Ender

Martin Marietta Aerospace

Mission Research Corp 735 State Street Santa Barbara, CA 93101 ATTN William C. Hart

Mission Research Corp-La Jolla 1150 Silverado Street P.O. Box 1209 La Jolla, CA 92038 ATTN V. A. J. Van Lint ATTN James Raymond

National Academy of Sciences ATTN: National Materials Advisory Board 2101 Constitution Avenue Washington, D.C. 20418 ATTN R. S. Shane Nat Materials Advsy

Northrop Corp Electronic Div 1 Research Park Palos Verdes Peninsula, CA 90273 ATTN Vincent R. Demartino ATTN Boyce T. Ahlport

Northrop Corp

Northrop Research and Technology Ctr

3401 West Broadway

Hawthrone, CA 90250

ATTN Orlie L. Curtis, Jr.

ATTN J. R. Srour

ATTN David N. Pocock

Palisades Inst. for Rsch Services, Inc. 201 Varick Street New York, NY 10014 ATTN Records Supervisor

Power Physics Corp 542 Industrial Way West P.O. Box 626 Eatontown, NJ 07724 ATTN Mitchell Baker

R & D Associates P.O. Box 9695 Marina Del Rey, CA 90291 ATTN S. Clay Rogers

Raytheon Company Hartwell Road Bedford, MA 01730 ATTN Gajanan H. Joshi Radar Sys Lab

Raytheon Company 528 Boston Post Road Sudbury, MA 01776 ATTN Harold L. Flescher

RCA Corporation

Government & Commercial Systems

ASTRO Electronics Div

P.O. Box 800, Locust Corner

Princeton, NJ 08540

ATTN George J. Brucker

RCA Corporation

David Sarnoff Research Ctr

W. Windsor Twp

201 Washington Road, P.O. Box 432

Princeton, NJ 08540

ATTN K. H. Zaininger

RCA Corporation

Camden Complex

Front & Cooper Sts

Camden, NJ 08012

ATTN E. Van Keuren 13-5-2

Research Triangle Inst P.O. Box 12194 Research Triangle Park, NC 27709 ATTN Eng Div Mayrant Simons Jr.

Rockwell International Corp 3370 Miraloma Ave Anaheim, CA 92803 ATTN N. J. Rudie FA53 ATTN James E. Bell HA10 ATTN George C. Messenger FB61 ATTN K. F. Hull ATTN L. Apodaca FA53

Rockwell International Corporation 5701 West Imperial Highway Los Angeles, CA 90009 ATTN T. B. Yates

Rockwell International Corporation

Electronics Operations

Collins Radio Group

5225 C Avenue NE

Cedar Rapids, IA 52406

ATTN Alan A. Langenfeld

ATTN Dennis Sutherland

ATTN Mildred A. Blair

Sanders Associates, Inc. 95 Canal Street Nashua, NH 03060 ATTN Moe L. Aitel NCA 1-3236

Science Applications, Inc.

P.O. Box 2351

La Jolla, CA 92038

ATTN Larry Scott

ATTN J. Robert Beyster

ATTN Victor Orphan

Simulation Physics, Inc.

41 "B" Street

Burlington, MA 01803

ATTN Roger G. Little

The Singer Company (Data Systems)

150 Totowa Road

Wayne, NJ 07470

ATTN Tech Info Ctr

Sperry Flight Systems Div Sperry Rand Corp P.O. Box 21111 Phoenix, AZ 85036 ATTN D. Andrew Schow

Sperry Rand Corp Univac Div Defense Systems Div P.O. Box 3525 Mail Station 1931 St. Paul, MN 55101 ATTN James A. Inda MS 41725

Sperry Rand Corp Sperry Div Sperry Gyroscope Div Sperry Systems Management Div Marcus Avenue Great Neck, NY 11020 ATTN Paul Marraffino ATTN Charles L. Craig EV Stanford Research Inst 333 Ravenswood Ave Menlo Park, CA 94025 ATTN Philip J. Dolan

Sundstrand Corp 4751 Harrison Avenue Rockford, IL 61101 ATTN Curtis B. White

Texas Instruments, Inc.

P.O. Box 5474

Dallas, TX 75222

ATTN Donald J. Manus MS 72

TRW Systems Group

One Space Park

Redondo Beach, CA 90278

ATTN H. H. Holloway R1-2036

ATTN O. E. Adams R1-1144 (2 copies)

ATTN R. K. Plebuch R1-2078 (2 copies)

ATTN Tech Info Center/S-1930

ATTN Robert M. Webb R1-2410

TRW Systems Group

San Bernardino Operations

P.O. Box 1310

San Bernardino, CA 92402

ATTN F. B. Fay 527/710

ATTN Earl W. Allen

TRW Systems Group

P.O. Box 368

Clearfield, UT 84015

ATTN Donald W. Pugsley

United Technologies Corp Hamilton Standard Div Bradley International Airport Windsor Locks, CT 06069 ATTN Raymond G. Giguere

Westinghouse Electric Corp

Defense and Electronic Systems Ctr

P.O. Box 1693

Friendship International Airport

Baltimore, MD 21203

ATTN Henry P. Kalapaca MS 3525

| 103-114A (REV. 7-73)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                       |                                                                                            |                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|---------------------------------|

| U.S. DEPT. OF COMM. BIBLIOGRAPHIC DATA SHEET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1. PUBLICATION OR REPORT NO.  NBSIR 77-1231        | 2. Gov't Accession    | 3. Recipient's                                                                             | s Accession No.                 |

| Measurement of Transistor Collector-Emitter Saturation Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |                       | 5. Publication Date  June 1977 6. Performing Organization Code                             |                                 |

| 7. AUTHOR(S) Kathryn Leedy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |                       | 8. Performing Organ. Report No.<br>NBSIR-1231                                              |                                 |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS  NATIONAL BUREAU OF STANDARDS  DEPARTMENT OF COMMERCE  WASHINGTON, D.C. 20234                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                       | 10. Project/Task/Work Unit No. Z99QAXTDO72 W.U.66  11. Contract/Grant No. DNA IACRO 77-809 |                                 |

| 12. Sponsoring Organization Name and Complete Address (Street, City, State, ZIP)  Defense Nuclear Agency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |                       | 13. Type of Report & Period  Covered Final  July 1976 to Jan. 1977                         |                                 |

| Washington, DC 20305                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                       |                                                                                            | 6 to Jan. 19//<br>g Agency Code |

| 16. ABSTRACT (A 200-word or less factual summary of most significant information. If document includes a significant bibliography or literature survey, mention it here.)  This report presents a detailed method for the measurement of collector-emitter saturation voltage. The method which is included in the Appendix is proposed for standardization. The report also contains a description of the laboratory confirmation of the method and a discussion of the precautions to be taken to assure repeatability of the measurement. Emphasized is the necessity to determine that the conditions for saturation are met during the measurement. |                                                    |                       |                                                                                            |                                 |

| name; separated by semicol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | entries; alphabetical order; capitalize or<br>ons) |                       |                                                                                            |                                 |

| 18. AVAILABILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | w Unlimited                                        | 19. SECURI<br>(THIS R |                                                                                            | 21. NO. OF PAGES                |