# NIST SPECIAL PUBLICATION 400-86

U.S. DEPARTMENT OF COMMERCE/National Institute of Standards and Technology

Semiconductor Measurement Technology:

Thermal Resistance Measurements

F. F. Oetlinger and D. L. Blackburn

QC

100

. U57

400-86

1990

C.2

# NATIONAL INSTITUTE OF STANDARDS & TECHNOLOGY

Research Information Center Gaithersburg, MD 20899

# DATE DUE

|                  | 1   |   |   |

|------------------|-----|---|---|

|                  | 1   |   | 1 |

|                  | 1   |   | 1 |

|                  |     |   |   |

|                  |     |   |   |

|                  | i   |   | i |

|                  |     |   |   |

|                  |     |   |   |

|                  | i   |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   | 1 |

|                  |     |   |   |

|                  |     |   |   |

|                  | l . |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  | 1   | 1 | 1 |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   | 1 |

|                  |     |   | ĺ |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   | 1 |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   | ĺ |

|                  |     |   |   |

|                  |     |   | L |

|                  |     |   |   |

| 1                |     |   |   |

| '                |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  | ,   |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  |     |   |   |

|                  | 200 |   |   |

| Demco, Inc. 38-2 | 293 |   |   |

Demco, Inc. 38-293

Semiconductor Measurement Technology:

# Thermal Resistance Measurements

Frank F. Oettinger and David L. Blackburn

Semiconductor Electronics Division Center for Electronics and Electrical Engineering National Engineering Laboratory National Institute of Standards and Technology Gaithersburg, MD 20899

July 1990

National Institute of Standards and Technology Special Publication 400-86 Natl. Inst. Stand. Technol. Spec. Publ. 400-86, 78 pages (July 1990) CODEN: NSPUE2

> U.S. GOVERNMENT PRINTING OFFICE WASHINGTON: 1990

# Semiconductor Measurement Technology: THERMAL RESISTANCE MEASUREMENTS

# Table of Contents

| 1                                                                                  | age  |

|------------------------------------------------------------------------------------|------|

| I. POWER TRANSISTORS                                                               | . 1  |

| Introduction                                                                       |      |

| The Concept of Thermal Resistance                                                  | . 2  |

| The Effect of Nonuniform Junction Temperature on the Definition of $R_{\theta JR}$ |      |

| The Variation of $R_{\theta JR}$ with Device Operating Conditions $(I_C,V_{CE})$   |      |

| General Methods for Measuring Device Temperature                                   |      |

| Control of the Thermal Environment                                                 |      |

| Selection of Temperature-Sensitive Electrical Parameters                           |      |

| Measurement of Temperature-Sensitive Electrical Parameters                         |      |

| Safe-Operating-Area Limits                                                         |      |

| DC Thermal Limit                                                                   |      |

| Second Breakdown Limit                                                             |      |

| Relating the Chip Temperature to the Measured Temperature                          |      |

| Determination of Area of Power Generation and Peak Junction Temperature            |      |

| Detection of Onset of Current Constrictions                                        |      |

| Reasons for Measuring Temperature                                                  | . 33 |

| Measurement of Integrated Power Devices                                            |      |

| Power Transistor Thermal Standardization Activities                                |      |

| II. INTEGRATED CIRCUITS                                                            | . 41 |

| $\hbox{Introduction}  .  .  .  .  .  .  .  .  .  $                                 | . 41 |

| Design of Thermal Test Chips                                                       |      |

| Computer Simulations                                                               |      |

| Thermal Properties of Materials                                                    |      |

| Guidelines for Thermal Test Chip Design                                            |      |

| Utilization of Thermal Test Chips                                                  |      |

| Mounting Considerations                                                            |      |

| Direct Measurement Procedures                                                      |      |

| Indirect Measurement Procedures                                                    | 60   |

| IC Thermal Standardization Activities                                              |      |

| Acknowledgments                                                                    | 68   |

| References                                                                         | . 68 |

# List of Figures

|     |                                                                                                                                                                                                                     | a   | ge  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| 1.  | Idealized versus real-world temperature distribution for a power transistor                                                                                                                                         | •   | 4   |

| 2.  | A 20-W power transistor coated with a thermographic phosphor shown for three different operating conditions, each dissipating 16 W                                                                                  |     | 6   |

| 3.  | Measured thermal resistance as a function of collector current at a constant power of 20 W for a 35-W triple-diffused transistor                                                                                    |     | 8   |

| 4.  | Temperature distribution of a Darlington power transistor measured with an automated infrared microradiometer                                                                                                       |     | 9   |

| 5.  | Photomicrograph of a Darlington transistor in the previous figure after experiencing a high power pulse                                                                                                             | . : | 10  |

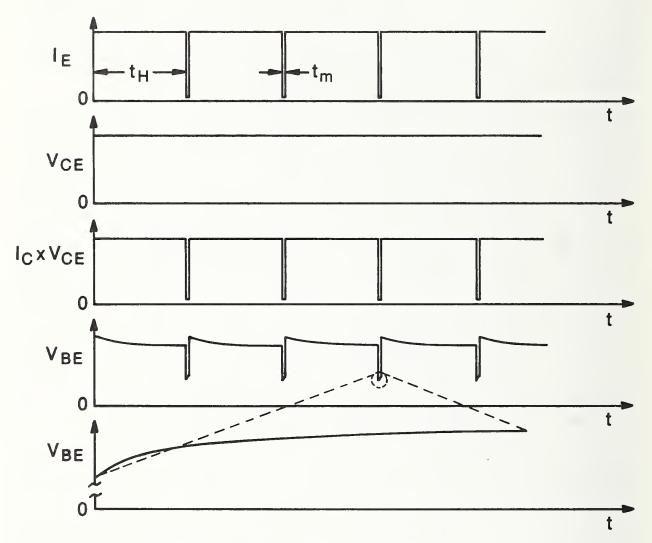

| 6.  | Heating and measurement waveforms as they appear at device terminals                                                                                                                                                |     | 12  |

| 7.  |                                                                                                                                                                                                                     |     |     |

| 8.  | Schematic of measurement circuit for using standard method for measuring temperature of a bipolar transistor                                                                                                        |     | 16  |

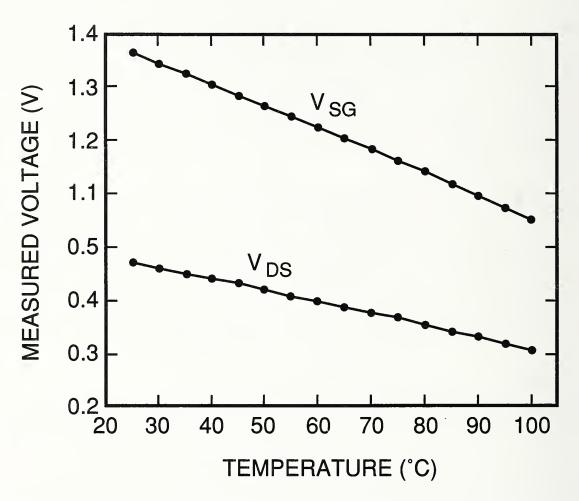

| 9.  | Examples of calibration curves for each of the power MOSFET TSEPs                                                                                                                                                   | . : | 18  |

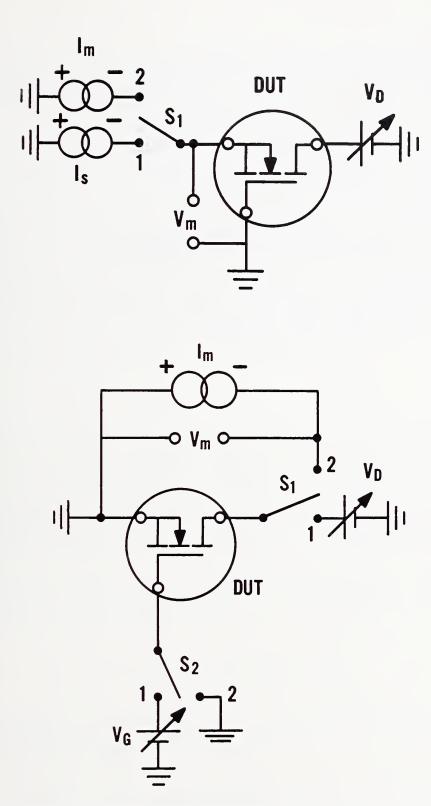

| 10. | Schematics of measurement circuits for each TSEP                                                                                                                                                                    |     | 19  |

| 11. | Measured and corrected emitter-base voltage waveform during measurement of the temperature for a bipolar transistor                                                                                                 | . 2 | 22  |

| 12. | Measured $T$ versus $\sqrt{t}$ and extrapolated temperature for a bipolar transistor .                                                                                                                              |     | 24  |

|     | A representative example of a manufacturer's published safe-operating-area (SOA) limits for a power transistor                                                                                                      |     |     |

| 14. | The manufacturer-specified SOA limits and the actual SOA limits determined by an infrared microradiometer for a power transistor which has no specified                                                             |     |     |

|     | second breakdown limit                                                                                                                                                                                              | . 2 | 27  |

| 15. | The manufacturer-specified SOA limits and the actual SOA limits determined by an infrared microradiometer for a device that is inadequately rated in the                                                            |     |     |

|     | second breakdown region by the manufacturer                                                                                                                                                                         | . 2 | 28  |

| 16. | The temperature distribution of a power MOSFET measured with an automated infrared microradiometer                                                                                                                  | . 3 | 30  |

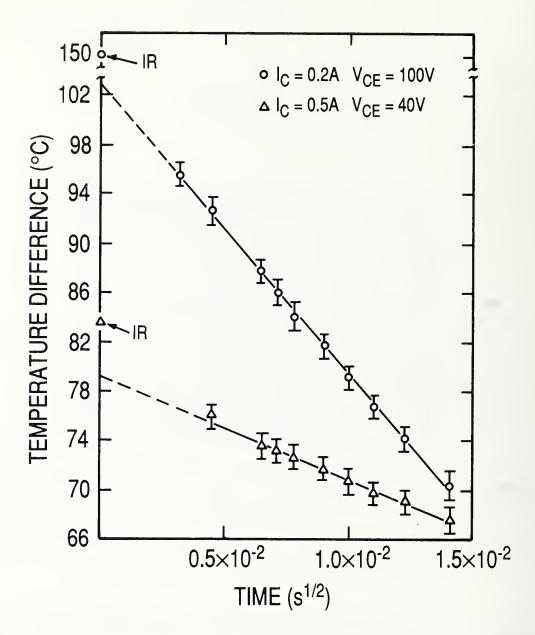

| 17. | The electrically measured cooling response of a power transistor versus the square root of time for two different operating conditions for the same power                                                           | . 3 | 32  |

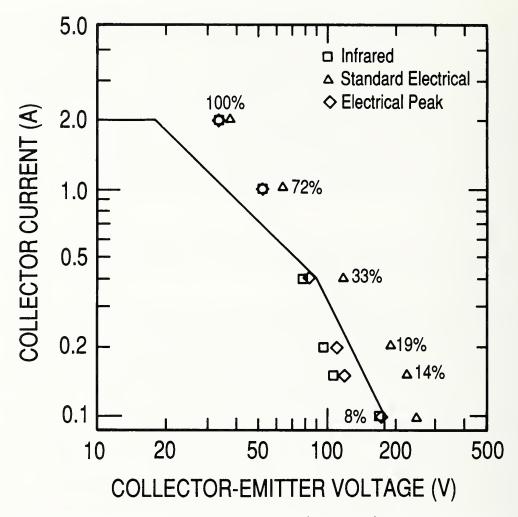

| 18. | The manufacturer-specified SOA limits and points along the measured SOA limits as determined by an infrared microradiometer, by the peak temperature electrical technique, and by the standard electrical technique | q   | 24  |

| 10  | The measured $V_{EB}$ at 20 $\mu$ s after the removal of a 1-s power pulse versus $V_{CE}$                                                                                                                          |     | 'n± |

| ıυ. | for a number of values of $I_C$                                                                                                                                                                                     | . 3 | 35  |

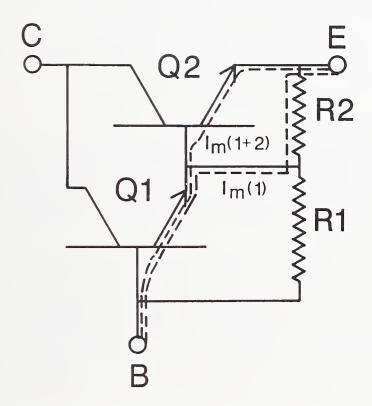

| 20. | Schematic of Darlington transistor                                                                                                                                                                                  |     |     |

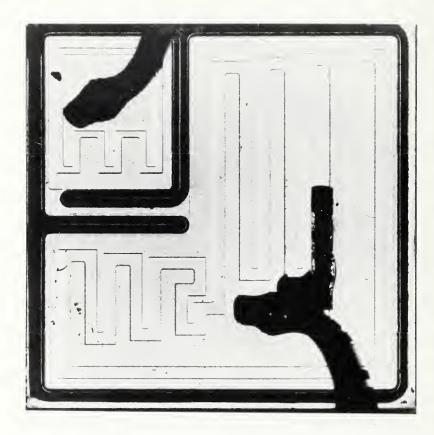

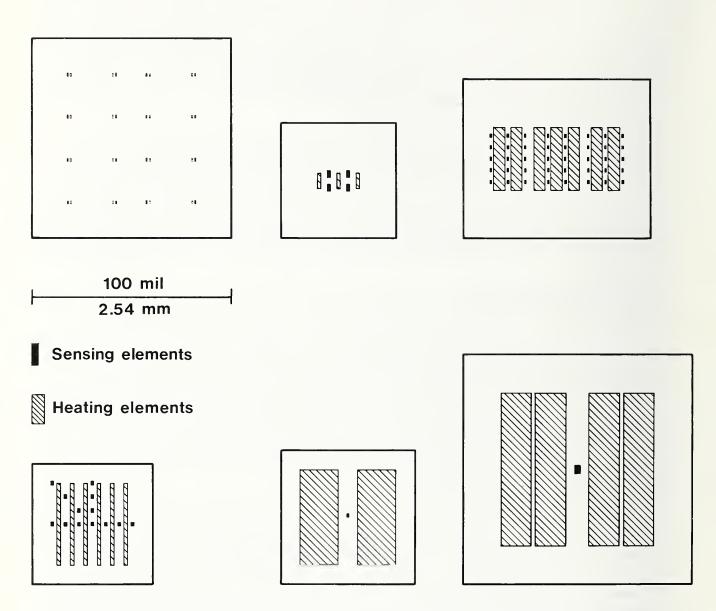

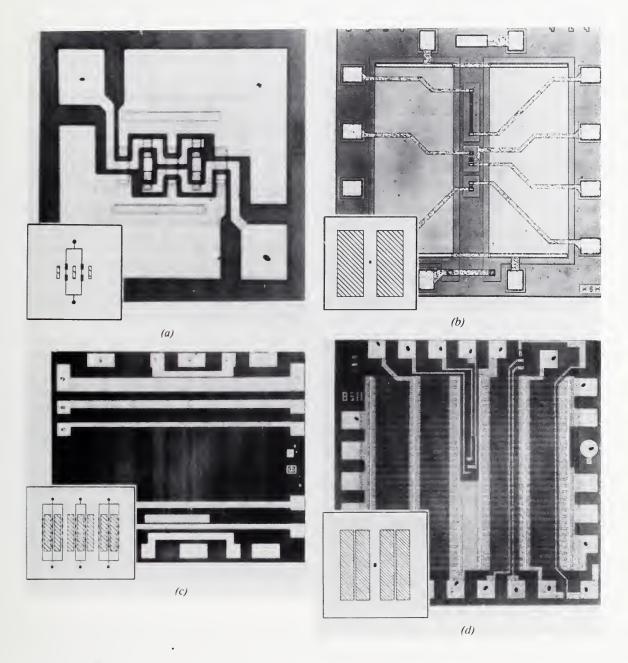

| 21. | Pictorial representation of heating and sensing areas on thermal test chips 44                                             |

|-----|----------------------------------------------------------------------------------------------------------------------------|

| 22. | Photomicrographs of representative thermal test chips with inserts showing                                                 |

|     | sensing diode circuit configuration                                                                                        |

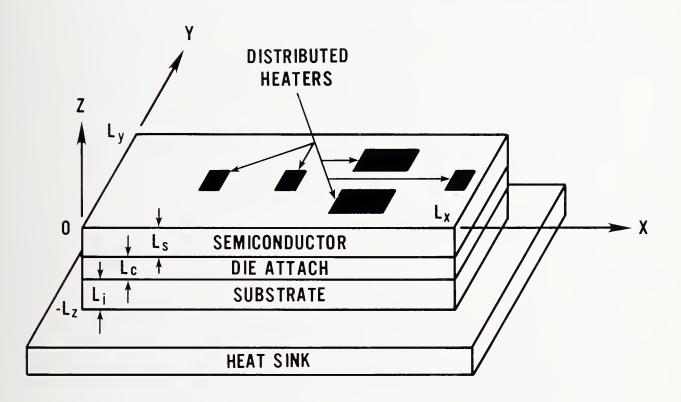

| 23. | Three-layer structure modeled by computer code                                                                             |

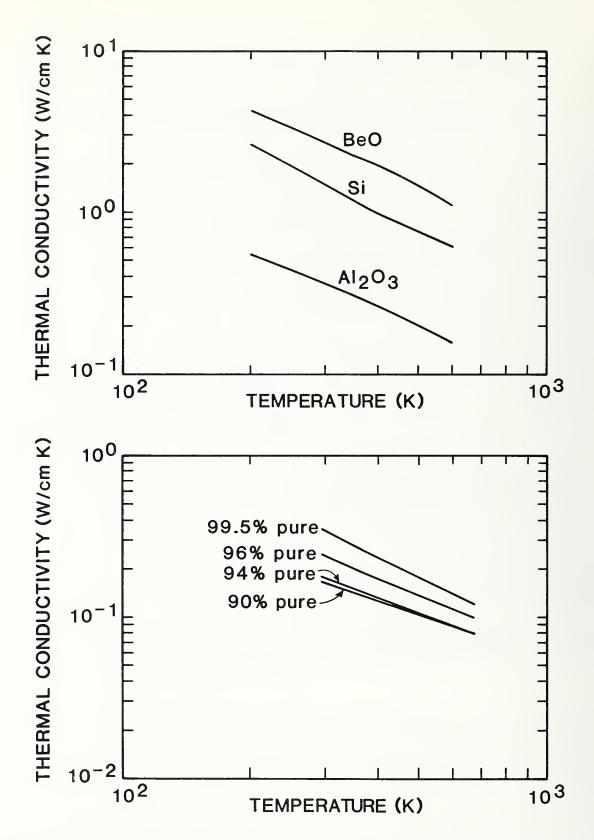

| 24. | Influence of temperature on the thermal conductivity of integrated-circuit-                                                |

|     | related materials                                                                                                          |

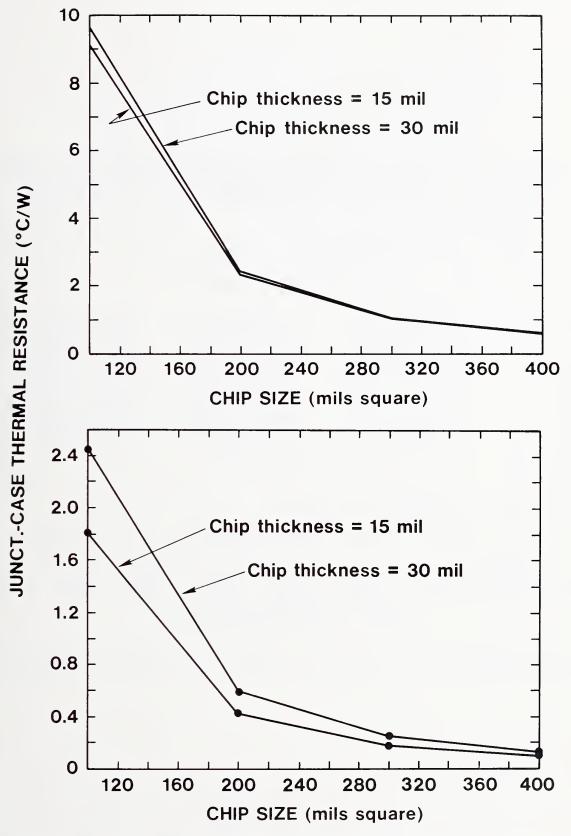

| 25. | Influence of chip size on the junction-to-case thermal resistance of a three-layer                                         |

|     | package structure                                                                                                          |

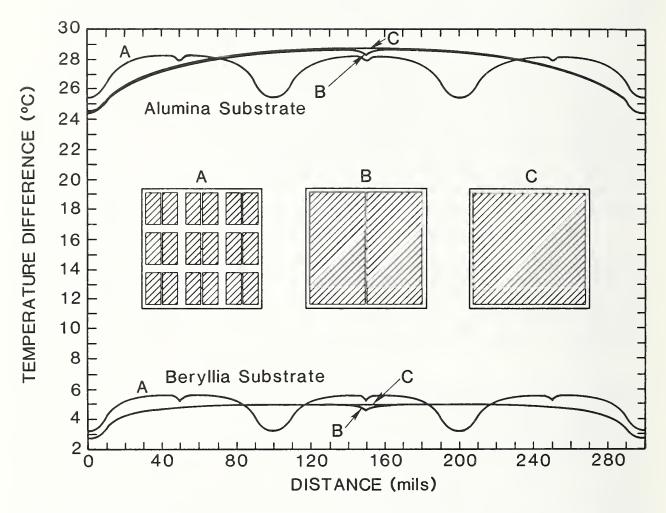

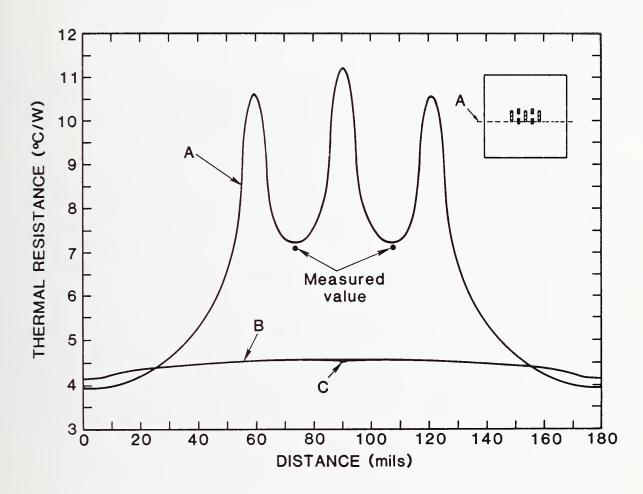

| 26. | Influence of heat source layout on chip surface temperature for test chip arrays and single cell chips                     |

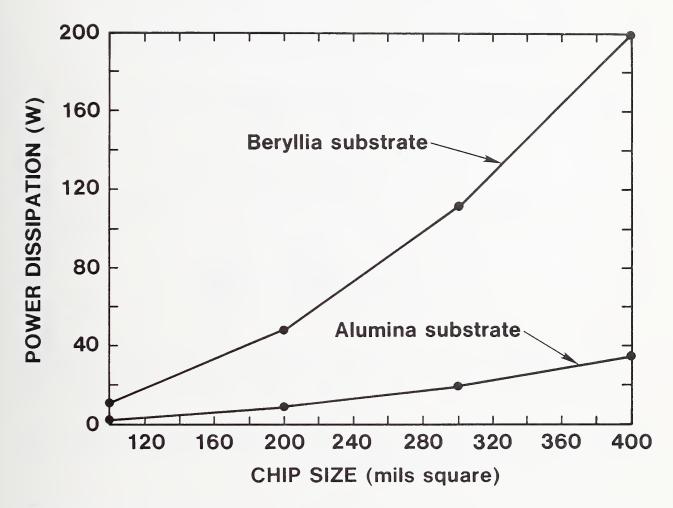

| 27. | Influence of chip size on internal power dissipation for a junction-to-case temperature difference of 20 °C                |

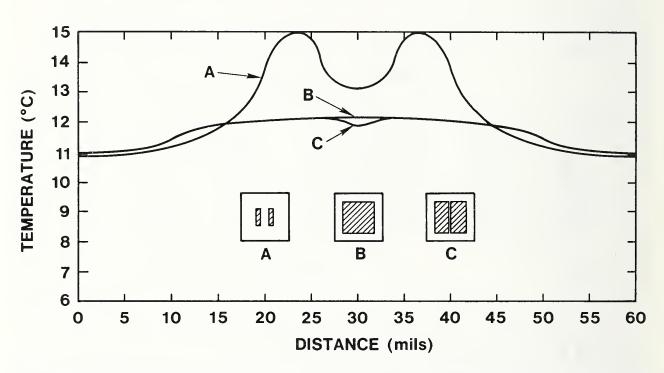

| 28. | Influence of heat source layout on chip surface temperature for a silicon chip eutectically bonded to an alumina substrate |

| 29  | Comparison of computer-simulated and measured thermal resistance for a                                                     |

| 20. | leadless ceramic chip carrier package                                                                                      |

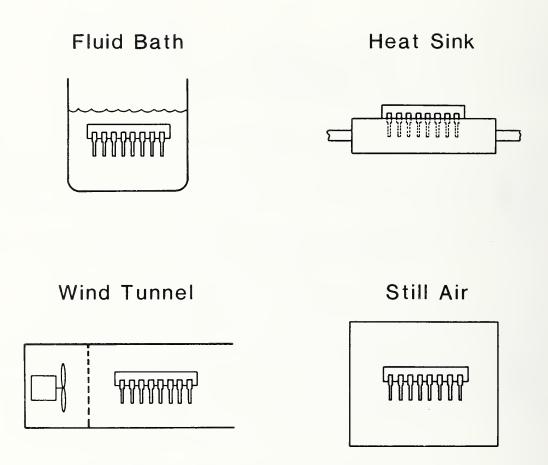

| 30. | Package mounting arrangements                                                                                              |

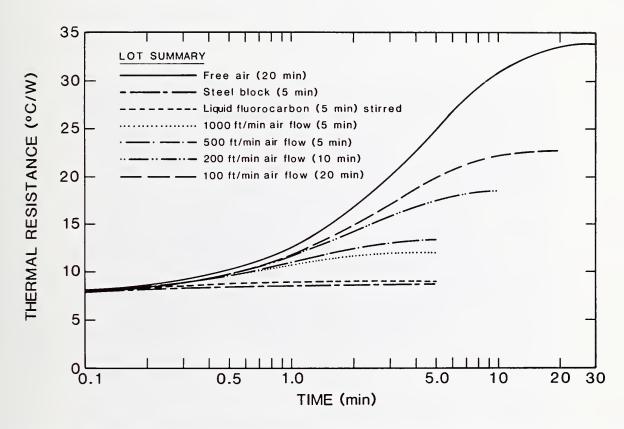

|     | Thermal response measurements for an alumina chip carrier package with an                                                  |

|     | integral aluminum heat sink for various mounting and cooling configurations 61                                             |

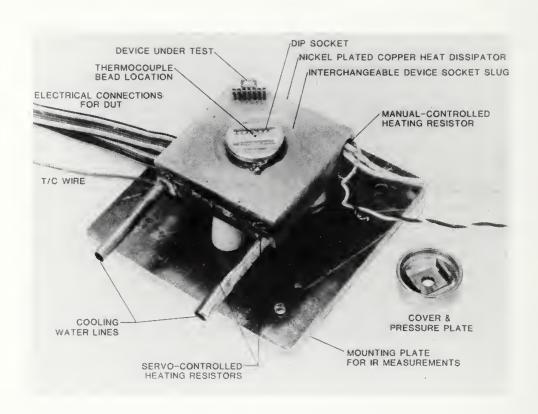

| 32. | Example of a temperature-controlled heat sink                                                                              |

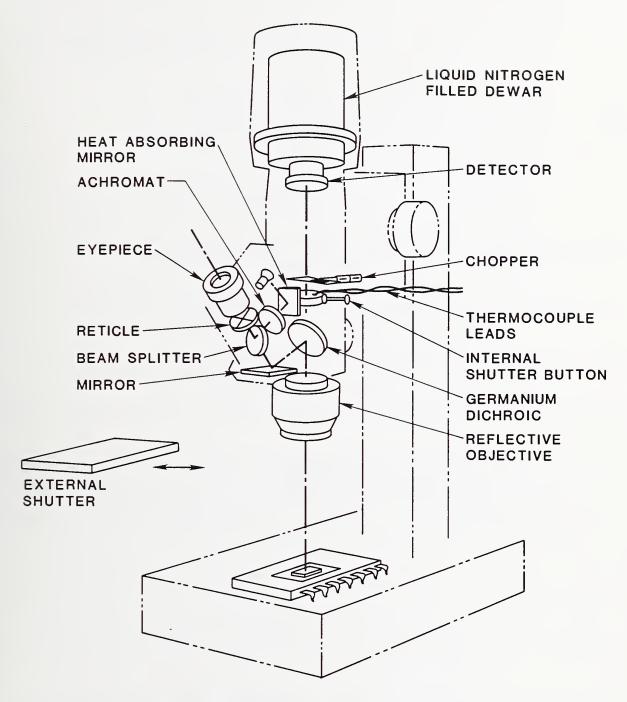

| 33. | Example of an infrared microradiometer                                                                                     |

|     |                                                                                                                            |

|     | List of Tables                                                                                                             |

|     | ${f Page}$                                                                                                                 |

| 1.  | Comparison of Thermal Resistance Measurement Techniques for a Bipolar                                                      |

|     | Transistor                                                                                                                 |

| 2.  | Comparison of Thermal Resistance Measurements for a MOSFET 20                                                              |

| 3.  | Procedure for Detecting Nonthermal Switching Transients and                                                                |

|     | Extrapolating Temperature to Instant of Switching                                                                          |

| 4.  | Advantages of Thermal Response Testing for Die Attachment                                                                  |

| 5.  | Procedure for Measuring the Temperature of Darlington Transistors 40                                                       |

| 6.  | Power Transistor Thermal Test Method Standardization                                                                       |

| 7.  | Thermal Conductivity of Materials                                                                                          |

| 8.  | Fabrication Technologies for Thermal Chips                                                                                 |

| 9.  | Computer Simulations of the Thermal Characteristics of Various                                                             |

|     | Chip-Package Configurations                                                                                                |

| 10. | Precision and Accuracy of Infrared Measurements                                                                            |

| 11. | IC Thermal Test Method and Specification Standardization 67                                                                |

# Semiconductor Measurement Technology: THERMAL RESISTANCE MEASUREMENTS

Frank F. Oettinger and David L. Blackburn

Semiconductor Electronics Division

National Institute of Standards and Technology

Gaithersburg, MD 20899

#### Abstract

This Special Publication reviews the thermal properties of power transistors and integrated circuits and discusses methods for characterizing these properties. The discrete devices discussed include bipolar transistors and metal-oxide-semiconductor field-effect-transistors. Measurement problems common to these devices, such as deciding the reason for requiring a particular measurement, adequate reference temperature control, selection of a temperature-sensitive electrical parameter, and separation of electrical and thermal effects during measurement are addressed. Due to the inherent difficulties in measuring and analyzing the thermal properties of active integrated circuits, an approach using specifically designed thermal test chips for evaluation of new die-attachment and packaging schemes is finding wide acceptance in the industry. In this Special Publication, indirect (i.e., electrical) measurements, direct (e.g., infrared) measurements, and computer simulation techniques for thermally characterizing integrated circuits are discussed in terms of their usefulness in characterizing VLSI packages.

Key words: integrated circuits; junction temperature; power transistors; safe-operating-area limits; temperature-sensitive electrical parameter; thermal measurements; thermal resistance; thermal test chips.

Disclaimer: Certain commercial equipment, instruments, or materials are identified in this paper in order to specify adequately the experimental procedure. Such identification does not imply recommendation or endorsement by the National Institute of Standards and Technology, nor does it imply that the materials or equipment identified are necessarily the best available for the purpose.

# I. POWER TRANSISTORS [1,2]

#### Introduction

Accurate characterization of the thermal properties of power transistors is critical to the reliability of the systems using these devices. Failure of a single power device can shut down a computer, bring to a halt a motor-driven system, or stop a vehicle dead in its tracks. Power devices are often expected to run hotter than other components, but the excessive temperature rise of an inherently "bad" device that "slipped through" screening will lead to early, often catastrophic failure. Likewise, the absence of adequate thermal characterization information may cause an otherwise "good" device to be used in a circuit

that stresses it beyond its thermal limits.

The purpose of this section is to review the thermal properties of power transistors and to discuss methods for characterizing these properties. The devices discussed include bipolar transistors and metal-oxide-semiconductor field-effect-transistors (MOSFETs). Measurement problems common to these devices, such as deciding the reason for requiring a particular measurement, adequate reference temperature control, selection of a temperature-sensitive electrical parameter (TSEP), and separation of electrical and thermal effects during measurement are addressed. Finally, the needs for thermal characterization of evolving devices such as high voltage and power integrated circuits and merged bipolar/MOSFET devices are mentioned.

### The Concept of Thermal Resistance

The concept of thermal resistance has been developed over the years as an aid to device manufacturers and users for calculating the junction temperature of operating devices. The concept is based upon an analogy between the electrical and thermal properties of materials, with temperature, heat flow, and thermal resistance being analogous to voltage, current, and electrical resistance, respectively. Thus, the equation

$$R_{\theta JR} \equiv \frac{T_J - T_R}{P} \tag{1}$$

where

$R_{\theta JR}$  = thermal resistance between the junction and the reference point (°C/W),

$T_J, T_R =$  temperatures of the junction and the reference point, respectively, (°C), and

P =power dissipated (W),

are used to define the device thermal resistance.

In applying the electrical analogy to the thermal problem and in using eq (1), it is implicitly assumed that

- 1) the junction temperature is spatially uniform, and

- 2)  $R_{\theta JR}$  is independent of the device operating conditions, i.e., independent of the values of collector current  $I_C$  and collector-emitter voltage  $V_{CE}$  used to obtain the power  $P(P \approx I_C \times V_{CE})$ .

Neither of these assumptions is valid for actual power transistors though, and care is needed in applying the results of eq (1) to real devices. The effect of these invalid assumptions on the defined and measured  $R_{\theta JR}$  is discussed in the remainder of this section.

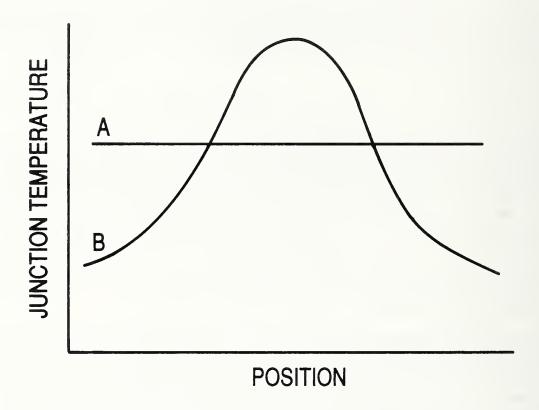

The Effect of Nonuniform Junction Temperature on the Definition of  $R_{\theta JR}$  – The idealized isothermal temperature distribution upon which eq (1) is based is shown superposed upon a

more realistic nonisothermal temperature distribution in figure 1. The calculation of  $R_{\theta JR}$  using eq (1) is straightforward for the isothermal case, but it is not immediately obvious how to apply the equation, or even if it is applicable, for the nonisothermal real-world case. This is because  $T_J$  is not well defined for the latter case in that it takes on a continuum of values between the peak junction temperature and the minimum junction temperature. For the concept of thermal resistance to be applicable to the real-world situation, some unique and meaningful value for  $T_J$  must be defined.

Because it is the peak junction temperature  $T_{J(peak)}$  that is most important for predicting the reliability and safe operation of a device,  $T_{J(peak)}$  is the most logical choice for use in place of  $T_J$  in eq (1) [3]. Thus, if eq (1) is rewritten as

$$R_{\theta JR(peak)} \equiv \frac{T_J(peak) - T_R}{P}$$

(2)

where  $R_{\theta JR(peak)}$ , the peak-junction-to-reference-point thermal resistance (°C/W), a unique and meaningful value of thermal resistance for any junction temperature distribution is defined. Unfortunately, all of the commonly used electrical methods for measuring junction temperature indicate some average temperature which is less than  $T_{J(peak)}$  by an unknown amount. Thus, if  $R_{\theta JR(peak)}$  is to be specified, some arbitrary correction factor usual must be applied to the measured value of  $R_{\theta JR}$  to account for the difference between the measured junction temperature and the peak junction temperature. There appears to be no consistency in the application of the arbitrary correction factor in common practice, and the factor is often insufficient to ensure safe device operation.

The peak junction temperature of power transistors can be estimated using a modification of the standard electrical measurement method in conjunction with some simple mathematical procedures [4]. Thus, realistic values for  $R_{\theta JR(peak)}$  can be determined without the need for arbitrary correction factors. A comparison of the actual peak thermal resistance as determined using an infrared microradiometer, that determined using the methods described in reference [4], and the average thermal resistance determined using the standard electrical technique is shown in table 1 for a number of devices and for a number of operating conditions. As can be seen in the table, a considerable difference may exist between the measured average thermal resistance and the peak thermal resistance.

Unfortunately, as also can be seen in table 1, the value of  $R_{\theta JR(peak)}$  depends upon the device operating conditions. This is true even for different values of  $I_C$  and  $V_{CE}$  which give nearly the same (or even the same) value of power  $(I_C \times V_{CE})$ . Thus, even though a unique value of thermal resistance can be defined for a given set of operating conditions, it is unique only to those specific operating conditions.

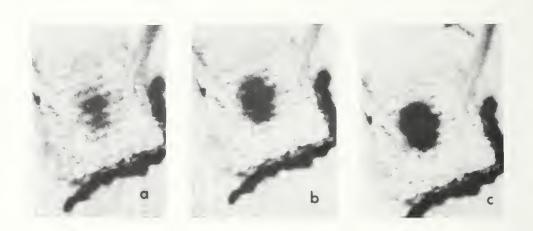

The Variation of  $R_{\theta JR}$  with Device Operating Conditions  $(I_C, V_{CE})$  – The value of  $R_{\theta JR(peak)}$  depends upon  $I_C$  and  $V_{CE}$  because the distribution of  $I_C$  throughout the device, and therefore the distribution of the power density, depends upon the device operating conditions [5,6]. An example of this can be seen in figure 2 for a 20-W planar power transistor which is dissipating 16 W of power for three different operating conditions. The device is coated

Figure 1. Idealized versus real-world temperature distribution for a power transistor. (A) idealized isothermal temperature distribution upon which the concept of thermal resistance is based; (B) more representative of the real-world temperature distribution for a power transistor.

TABLE 1

Comparison of Thermal Resistance Measurement Techniques for a Bipolar Transistor

| lesistance                         | Infrared<br>Microradiometer  | 14.6       | 0.6      | 5.5    | 3.4    | 2.7    | 4 6     | 4.0     | 2.9    | 2.1    | 8.<br>8. | 3.4    | 3.2    | 2.9    |

|------------------------------------|------------------------------|------------|----------|--------|--------|--------|---------|---------|--------|--------|----------|--------|--------|--------|

| Measured Thermal Resistance (°C/W) | Electrical Peak<br>Technique | 12.5       | 7.8      | 5.5    | 3.5    | 2.7    | 1.4     | 3.7     | 2.8    | 2.1    | 3.6      | ი<br>ი | 3.4    | 3.0    |

| Z                                  | Standard<br>Electrical       | <b>o</b> : | ນ<br>ນີ້ | 4.2    | 3.0    | 2.5    | 2.9     | 2.8     | 2.4    | 1.9    | 3.3      | 3.0    | 3.0    | 2.8    |

| Dower                              | (W)                          | 17         | 21       | 32     | 54     | 99     | 28      | 32      | 44     | 92     | 46       | 20     | 26     | 09     |

| Onerating Condition                | $I_C(A)/V_{CE}(V)$           | 0.1/170    | 0.2/105  | 0.4/80 | 1.0/54 | 2.0/33 | 0.2/140 | 0.3/106 | 1.0/44 | 2.0/38 | 0.6/76   | 1.0/50 | 2.0/28 | 3.0/20 |

| Specified Ross                     | MCAL TOWNS                   |            |          | ນ      |        |        |         |         | 1.5    |        |          |        | 2      |        |

| Dovice                             | Number                       |            |          |        |        |        |         |         | 2      |        |          |        | က      |        |

Figure 2. A 20-W power transistor coated with a thermographic phosphor shown for three different operating conditions, each dissipating 16 W. The phosphor when illuminated with ultraviolet radiation as done here is brightest at the cooler areas and darkest at the hotter areas. (a)  $I_C = 0.8$  A,  $V_{CE} = 20$  V; (b)  $I_C = 0.4$  A,  $V_{CE} = 40$  V; (c) $I_C = 267$  mA,  $V_{CE} = 60$  V.

with a thermographic phosphor [7] which appears darkest at the hottest areas of the device in this figure. For the low-current, high-voltage conditions ( $I_C = 267 \text{ mA}$ ,  $V_{CE} = 60 \text{ V}$ ), the power density is much more localized (as evidenced by the very dark "hot-spot") than for either of the other two operating conditions. This is despite the fact that the same power is being dissipated for each condition. The peak thermal resistance for the operating condition depicted in figure 2(c) is about 9.7 °C/W and for the condition depicted in figure 2(a) is about 9.1 °C/W. Although the  $R_{\theta JR(peak)}$  in this instance varies by only a few percent, variations as a function of operating conditions of several hundred percent are not uncommon for other devices [5].

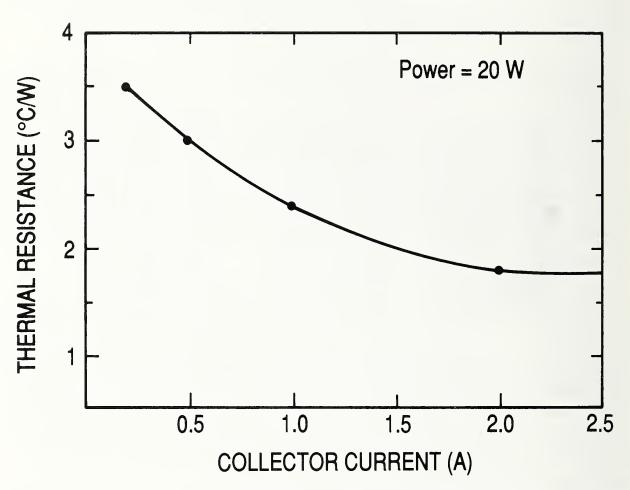

In general, for low-current, high-voltage operation, the thermal resistance is a strong function of operating conditions. At the other extreme, high current and low voltage, it is not as strong a function of operating conditions, but it still may depend upon  $I_C$  and  $V_{CE}$ . This can be seen in figure 3, which shows a plot of thermal resistance versus  $I_C$  at constant power for a bipolar power transistor. The reason for the large values of  $R_{\theta JR}$  at low values of  $I_C$  is that the thermal-electrical feedback mechanisms that initiate current crowding and eventually second breakdown [8] are stronger at small values of  $I_C$  than at large values. Thus, the current tends to be more constricted and the peak temperature higher for these conditions. It is shown later that the presence of current crowding and the associated large  $R_{\theta JR(peak)}$  at low values of  $I_C$  should be taken into account when generating SOA limits.

### General Methods for Measuring Device Temperature

There are two sets of "generic" methods in general use for measuring the operating temperature of a semiconductor device. One set requires that the semiconductor chip be exposed for viewing and in some instances that a foreign substance be placed on the surface of the chip. Examples are infrared microradiometry [9] and the use of liquid crystals [10,11] and thermographic phosphors [7]. These methods allow one to create a map of the temperature distribution on the chip surface. The infrared method is of most interest here for mapping purposes because it can be used to quantitatively map the surface temperature, whereas the other methods, although extremely valuable, are more qualitative in nature. The other set of "generic" methods uses a temperature-sensitive electrical parameter (TSEP) of the device as a thermometer. These methods can be performed on fully packaged devices but give a single, average temperature value for the chip.

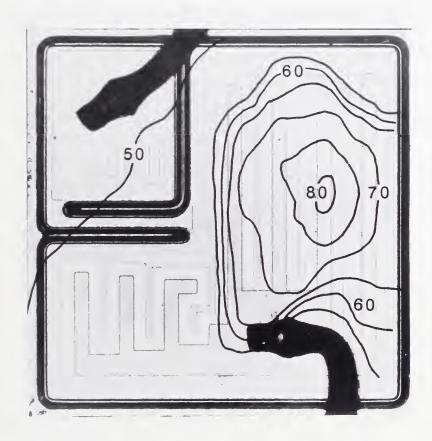

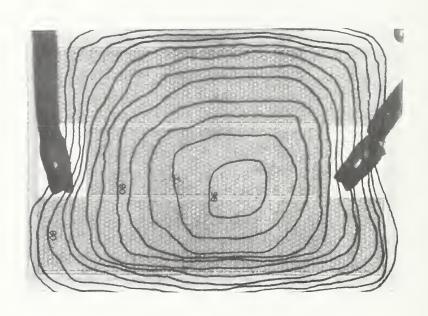

The infrared methods are the most useful methods for accurately determining the distribution of temperature on the device surface. Because the surface temperature is never uniform, a single temperature value cannot fully characterize the temperature of the device, and large-temperature nonuniformities can be mapped using the infrared techniques. An example of the value of this is shown in figure 4, in which the temperature distribution for a power Darlington chip, measured using an automated infrared microradiometer, is displayed. From this display, it is clear that one area of the chip (the hottest area) is dissipating most of the power. Much of the chip is apparently dissipating little or no power. Only from such a temperature map can one establish the nonuniformity of the temperature and the area of the chip that is dissipating most of the power. The impact that this has on chip reliability is demonstrated by the picture in figure 5 of the same

Figure 3. Measured thermal resistance as a function of collector current at a constant power of 20 W for a 35-W triple-diffused transistor.

Figure 4. Temperature distribution of a Darlington power transistor measured with an automated infrared microradiometer.

Figure 5. Photomicrograph of a Darlington transistor in previous figure after experiencing a high power pulse. Dark area leading from bond wire at bottom center of figure is melted emitter metallization.

chip after it experienced a brief high power pulse. The darkened area is melted aluminum, leading from the emitter bond wire to the spot on the chip that was hottest during the temperature scan.

The major problem with infrared methods is that they require that the device being studied be "decapped" and visible to the infrared. In addition, the methods are time-consuming, they are quantitatively practical only for steady-state measurements, they require extensive temperature control equipment for controlling the thermal environment of the device being studied, and they require expensive infrared measuring equipment. For these reasons, such measurements are often only made to diagnose problems, such as the one demonstrated by figures 4 and 5.

Temperature measurement methods that use TSEPs are the most often-used methods. They have the advantage that they can be performed on fully packaged devices, oftentimes may be done quickly and are easy to perform, can be quantitatively accurate for steady-state or transient conditions, can often be done with relatively inexpensive electrical equipment, and in certain special circumstances may be done with minimal heat sinking or thermal environment control. The typical "electrical" measurement of temperature is done in two phases, the calibration phase and the measurement phase. In the calibration phase, the value of the particular TSEP chosen is calibrated versus temperature. For instance, if the emitter-base voltage of a bipolar transistor is selected as the TSEP, the value of the emitter-base voltage is determined at various chip temperatures. This is accomplished by externally heating the device, such as in an oven or by a temperature-controlled hot plate or heat sink, and then measuring the emitter-base voltage with a constant current passing through the device. The constant current must be very small as it is assumed that the device is at the same temperature as the oven environment or hot plate which requires that no power (or at least minimum power) be dissipated in the device. In the measurement phase, the device is self-heated by dissipating at a much larger power than that at which the calibration was done. To measure the temperature, the device must be switched from the heating condition (high power) to the measurement condition (the same low current and power at which the calibration was performed) with a heating power duty factor of approximately unity. An example of the heating and measurement waveforms for measuring the temperature of a bipolar transistor is shown in figure 6.

In calculating the power transistor junction-to-reference-point thermal resistance and assuming the previously stated approximations, i.e., 1) the power dissipation during calibration is negligible and 2) the heating power duty factor is approximately unity, the following equation is used [12]:

$$R_{\theta JR} = \frac{T_J - T_R}{P(Avg)} = \frac{V_{MH} - V_{MC}}{P_H} \left( \frac{\Delta V_{MC}}{\Delta T_{MC}} \bigg|_{I_M} \right)^{-1} \tag{3}$$

where

$R_{\theta JR}$  = thermal resistance, junction to reference point (°C/W),

Figure 6. Heating and measurement waveforms as they appear at device terminals. This is a specific example for a bipolar transistor.

$T_J = \text{junction temperature (°C)},$

$T_R$  = reference point temperature (°C),

$I_M = \text{measuring/calibration current (mA)},$

P(Avg) = average heating power applied to transistor causing temperature difference  $T_J - T_R$  (W),

$P_H$  = magnitude of heating power applied to transistor (W),

$V_{MH}$  = value of TSEP corresponding to the temperature of the junction heated by  $P_H$  and measured at  $I_M$  (mV),

$V_{MC}$  = value of TSEP during calibration at  $I_M$  and specific value of  $T_{MC}$  (mV),

$T_{MC}$  = calibration temperature measured at reference point (°C), and

$\Delta V_{MC}/\Delta T_{MC} = \text{TSEP}$  temperature coefficient measured at  $I_M$  (mV/°C).

There are some subtle but potentially major difficulties with the switching requirements of the electrical methods. One is that the device is cooling during the actual measurement because the heating power has been removed. For an accurate measurement to be made, this cooling must be considered and taken into account. Second, the device cannot change electrical states instantaneously. It takes a finite time for the device to switch fully from the heating state to the measurement state. If a measurement is made before the electrical switching is completed, large errors can result in the measured temperature. Finally, as figure 4 demonstrates, the device has some distribution of temperature, but the electrical methods indicate a single device temperature that is some average of this temperature distribution. Methods have been developed to overcome some of the limitations of the electrical measurement procedures. They are discussed in later sections of this publication.

#### Control of the Thermal Environment

If one is to measure accurately the thermal characteristics of a device, the thermal environment of the device during measurement must be known and controlled. This environment will typically not be the environment experienced by the device in its application, but it must be known and controlled for one to relate the measured characteristics to the application characteristics.

Knowledge and control of the thermal environment usually means knowledge and control of the temperature at a specified point on the device or its package. To "know" the temperature at the reference point means that a thermocouple, thermistor, or thermometer of some other type be attached to or in some way determine the temperature at the point. It is usually not satisfactory to know only the temperature of the surrounding gas or fluid because in most instances the reference temperature and the fluid or gas temperature will be different.

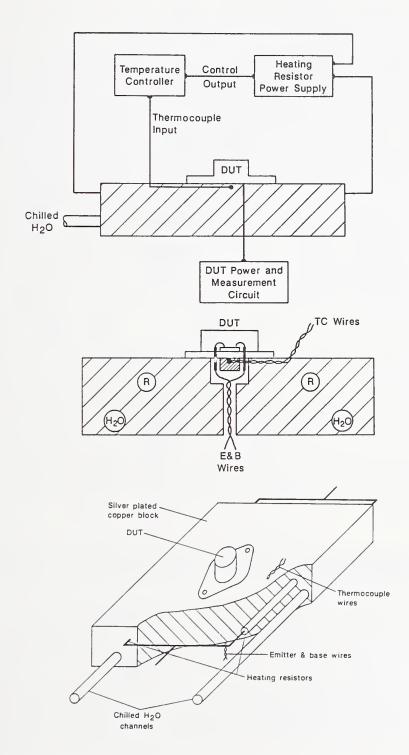

For steady-state, multiple-pulse, or single-pulse heating conditions greater than about

300 ms in length, it is usually not sufficient to use a heat sink that is not temperature controlled, such as merely a large copper block. The problem is that the uncontrolled heat sink begins to rise in temperature, heated by the device under test, making it impossible to maintain a controlled reference point temperature. Control and measurement of the reference point temperature is usually difficult and requires ancillary equipment such as temperature sense and control units and methods of heating and cooling the heat sink. A schematic of a temperature-controlled heat sink and temperature control system used at the National Institute of Standards and Technology for many years is shown in figure 7. The copper heat sink is continuously cooled by the chilled water and intermittently heated by the heating resistors as required. The temperature control unit senses the temperature with a thermocouple and commands the power supply to supply heating current to the resistors to maintain the preset temperature. With the system shown in the figure, the reference point temperature can be controlled to within about 0.1 °C.

For some important measurements, a heating pulse of less than 300 ms is desirable. Such a case is for die-attach evaluation [13-18]. In this instance, one wants to make the die-attach portion of the thermal resistance to be as large a portion as possible of the measured thermal resistance. This is accomplished with a short heating pulse of the appropriate length. More will be said about this later, but for this type of measurement, close control of the thermal environment is not critical because the thermal resistance between the device package and the environment does not enter into the measurement.

## Selection of Temperature-Sensitive Electrical Parameters

Although a variety of factors enter into the selection of a TSEP for measuring the temperature of a particular device, the two most important factors are the accuracy with which the TSEP can determine the device temperature and the convenience or ease of use of the particular parameter. The particular parameter chosen may also depend upon the reason for performing the thermal characterization. If the purpose is to qualify a device to some particular rating or limit, the most accurate parameter should be used. If the purpose is to screen devices quickly or as an outgoing or incoming inspection, then an easier, more convenient parameter may be chosen, provided good correlation between the actual temperature and the parameter being measured has been established.

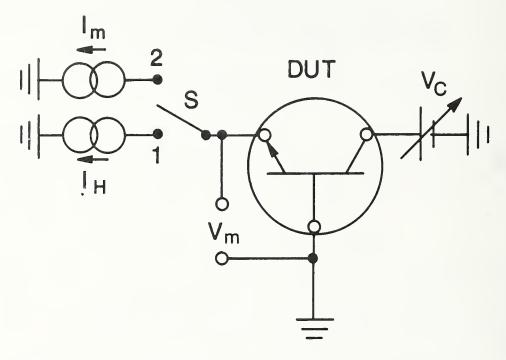

It has been well established that the most accurate and the easiest TSEP to use for bipolar devices is the emitter-base voltage measured at a small, constant current. In addition, it has been found that the preferred technique to use is the "emitter-only switching" method for which the collector voltage is not switched between the heating conditions and the measurement conditions [12,19-20]. A schematic of the measurement circuit is shown in figure 8 and the various waveforms at the terminals of the device under test are those shown in figure 6.

The situation for power MOSFETs is more complicated than for the bipolar transistor. It has been shown that the most accurate TSEP for the MOSFET is the threshold voltage, i.e., the source-gate voltage measured at a small drain current [21]. Although the procedure developed for using the source-gate voltage as the TSEP is nearly identical to that used

Figure 7. Schematic of the temperature control system (a) and temperature-controlled heat sink (b,c) used at the National Institute of Standards and Technology.

Figure 8. Schematic of measurement circuit for using standard method for measuring temperature of a bipolar transistor.

for the emitter-only switching method used for bipolar transistors, and is equally as easy, a different method has been standardized and is therefore most often used [22]. This second method uses the forward voltage of the intrinsic drain-body diode present in all power MOSFETs as measured using the drain-source voltage as the TSEP. Examples of a calibration curve for each of these TSEPs are shown in figure 9. Schematics of the measurement circuits for these two techniques are shown in figure 10 with a comparison of the extrapolated TSEP temperatures to that of infrared measurements of the peak chip surface temperature given in table 2. This method has been selected as the standard because it was in popular use for several years before the threshold voltage method was developed and also because the calibration of the diode forward voltage is somewhat simpler than that of the threshold voltage. This latter condition is related to the fact that the variation in  $dV_{ds}/dT$  for a group of "identical" diodes is usually less than the variation in  $dV_{th}/dT$  for MOSFETs. Thus, rather than generating a single calibration curve valid for all MOSFETs of a single type, as is done for diodes, the threshold voltage method could require calibration for each device. Fortunately, because power MOSFETs usually have a comparatively uniform chip temperature distribution, the standard method is usually satisfactory.

The situation for merged bipolar/MOSFET devices is not well defined. The only commercially relevant device in this category today is the Insulated Gate Bipolar Transistor (IGBT). One difficulty with this device is that there is no intrinsic diode available as there is for the power MOSFET. It is possible that the threshold voltage of this device will yield similarly accurate temperature measurements as for the power MOSFET and be equally as easy to use. The other possible candidate as a TSEP is the forward voltage drop, or saturation voltage, of the device measured at a low forward current. Little reported work has been done on comparing the various TSEPs for temperature measurements of the IGBT, although the threshold voltage has been proposed as the TSEP in a military standard.

# Measurement of Temperature-Sensitive Electrical Parameters

The method chosen to measure the TSEP is critical to determining the accuracy and repeatability with which the TSEP indicates the actual device temperature. Because the measurement procedure nearly always requires the device under test to be switched from a high-power, heating condition to a low-power, measuring condition, the presence, control, and identification of "nonthermal" switching transients are problems for all device types. Nonthermal switching transients are defined as electrical transients that mask the temperature variations of the TSEP that one is attempting to measure. Often, these nonthermal effects are inseparable from the desired thermal effects without some "post-data collection" processing. Ignoring nonthermal switching transients probably is second only to lack of reference temperature control in contributing to temperature measurement errors.

Typically, the TSEP has a variation with temperature of a few millivolts per degrees Celsius. Thus, for an accurate and reliable measurement of temperature, a few millivolts error in the TSEP translates into a few degrees Celsius error in temperature. For instance, the emitter-base voltage at a low emitter current typically has a temperature variation

Figure 9. Examples of calibration curves for each of the power MOSFET TSEPs.

Figure 10. Schematics of measurement circuits for each TSEP. Source-gate voltage (top); drain-source voltage (bottom).

TABLE 2

Comparison of Thermal Resistance

Measurement Techniques for a MOSFET

| Device | Operating<br>Conditions | Temperat     | ure Rise Al  | bove Case (°C) |

|--------|-------------------------|--------------|--------------|----------------|

| Number | $I_D(A)/V_{DS}(V)$      | IRM          | $V_{SG}$     | $V_{DS}$       |

|        | 0.5/60                  | 33.5         | 31.0         | 28.8           |

| 1      | 1.0/30                  | 33.5         | <b>3</b> 1.0 | 28.8           |

|        | 1.5/20                  | 33.5         | 31.0         | 27.8           |

|        | 0.5/60                  | 38.0         | <b>35.</b> 0 | 36.5           |

| 2      | 1.0/30                  | 38.0         | <b>3</b> 5.0 | 36.1           |

|        | 1.5/20                  | 38.0         | <b>35.</b> 0 | 36.1           |

| 3      | 1.0/60                  | 80.0         | 80.3         | 70.7           |

|        | 1.5/40                  | 80.0         | 80.3         | 70.4           |

|        | 0.5/60                  | <b>37.</b> 0 | 36.8         | 36.1           |

| 4      | 1.0/30                  | <b>37.</b> 0 | 36.8         | 36.1           |

|        | 1.5/20                  | 37.0         | 36.8         | 35.0           |

| 5      | 1.5/40                  | 73.0         | 69.0         | 62.0           |

| 6      | 1.0/20                  | 34.3         | 31.4         | 28.1           |

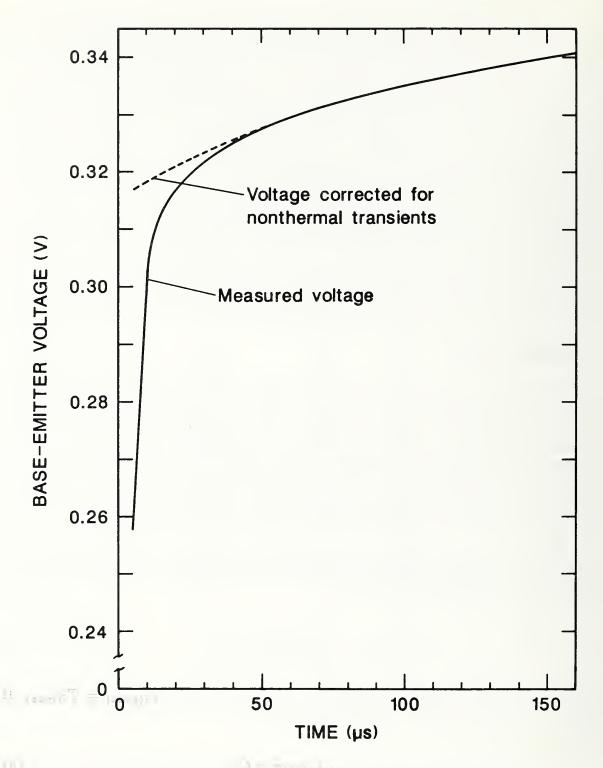

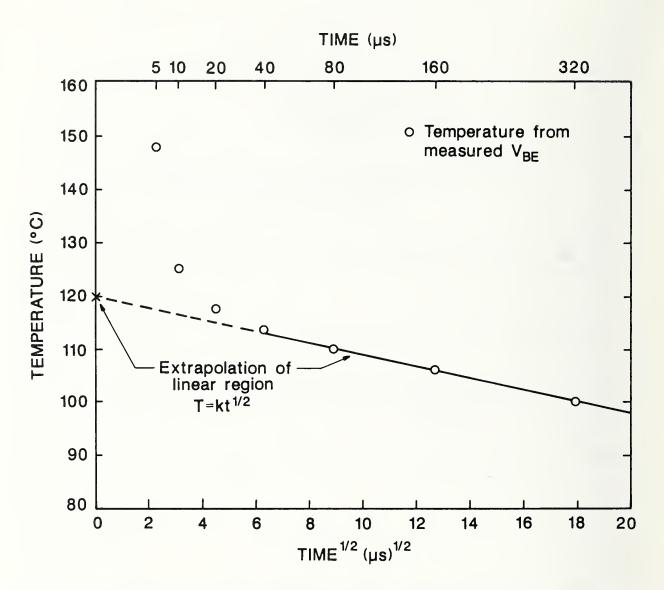

of about -2 mV/°C. In the usual switching application, if the emitter base voltage has settled to within a few tens of millivolts of its final value, the device has for all intents and purposes finished switching. It may take less than a microsecond for the voltage to settle to within a few tens of a millivolt of its final value, but it typically takes more than 10 µs for the voltage to settle to within a millivolt of the final value. It has even been shown that the metallic leads of a typical power device package contribute to these nonthermal switching transients [23]. An example of this is shown in figure 11. The net result of all this is that to measure the temperature accurately using a TSEP, one must wait until the nonthermal switching transients have subsided. This will nearly always require a delay of at least 20 µs after switching to the low-level measurement condition from the high-level heating condition. Usually, the delay is longer, sometimes being 100  $\mu s$  or longer. A method has been developed for detecting the presence of nonthermal switching transients and for extrapolating the temperature measured after a delay time to the temperature of the device at the moment that the device was switched [24]. The procedure used is based upon one-dimensional cooling theory and is summarized in table 3. An example of the measured temperature, with and without consideration of nonthermal switching transients, and the extrapolated temperature are shown in figure 12.

### Safe-Operating-Area Limits

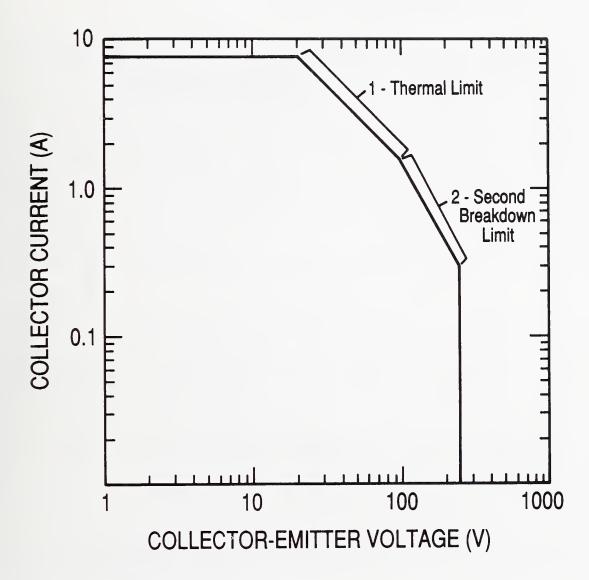

Device manufacturers publish safe-operating-area (SOA) limits for nearly all of their power transistors. The limits define an area on an  $I_C - V_{CE}$  plane within which safe operation is guaranteed and within which the peak junction temperature is guaranteed not to exceed the specified safe maximum temperature,  $T_{J(max)}$ . These limits are set for both dc and pulsed operation, but the limits of the SOA of concern here are the dc thermal limit and the dc second breakdown limit denoted by the line segments 1 and 2, respectively, in figure 13. The discussion is also limited to forward-bias SOA limits. A comparison of the techniques generally used for determining the pulsed thermal limits has been published [24].

DC Thermal Limit – The dc thermal limit of the SOA is in reality determined from the thermal resistance of the device. Because the thermal limit defines the limit along which  $T_{J(peak)} = T_{J(maz)}$ , one finds from eq (2)

$$R_{\theta JR(peak)} = \frac{T_{J(max)} - T_R}{(I_C \times V_{CE})_{LIMIT}} \tag{4}$$

where  $(I_C \times V_{CE})_{LIMIT}$  defines the locus of points along which  $T_{J(peak)} = T_{J(maz)}$ . If  $R_{\theta JR(peak)}$  is assumed constant, as are  $T_{J(maz)}$  and  $T_R$ ,

$$(I_C \times V_{CE})_{LIMIT} = C, (5)$$

where C is constant (i.e., constant power), or,

$$ln[I_C] = -ln[V_{CE}] + C'. (6)$$

Figure 11. Measured and corrected (for nonthermal switching transients) emitter-base voltage waveform during measurement of the temperature for a bipolar transistor.

#### TABLE 3

Procedure for Detecting Nonthermal Switching Transients and Extrapolating Temperature to Instant of Switching

- 1. Measure temperature in normal manner but as a function of time after switching. A series of measurements between 10  $\mu$ s and 250  $\mu$ s after switching is satisfactory.

- 2. Plot measured temperature, T, versus the square root of time after switching,  $\sqrt{t}$ .

- 3. Nonthermal switching transients have subsided at the time the plot of T versus  $\sqrt{t}$  becomes linear.

- 4. Draw a straight line through the linear portion of the T versus  $\sqrt{t}$  plot and extend the line to t=0. The intercept with the t=0 axis is the extrapolated temperature at the instant of switching.

An example of the results of this procedure is shown in figure 12.

Figure 12. Measured T versus  $\sqrt{t}$  and extrapolated temperature for a bipolar transistor. The time after switching for each measured temperature is noted on the top scale.

Figure 13. A representative example of a manufacturer's published safe-operating-area (SOA) limits for a power transistor.

Thus, a straight-line relation with a slope of -1 exists between  $ln[I_C]$  and  $ln[V_{CE}]$  if  $R_{\theta JR(peak)}$  is constant. This can be seen in figure 13, where line segment 1 has a slope of -1. The specified thermal limit of the SOA will usually run from the maximum safe value of collector current,  $I_{C(max)}$ , to some lower value of  $I_C$  at which point a limit of slope less than -1, the second breakdown limit, commences.

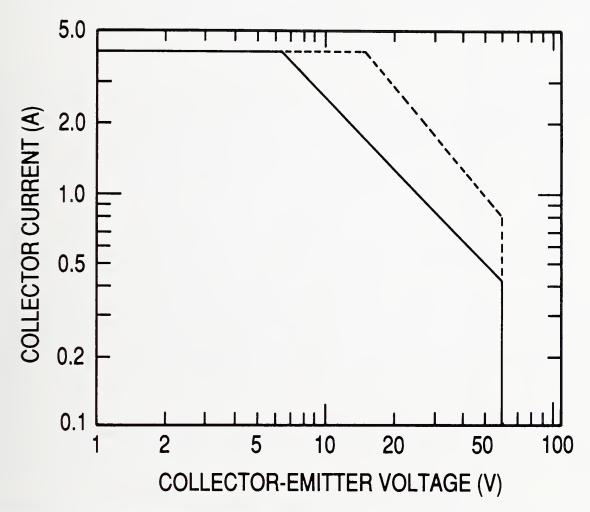

As has been shown previously,  $R_{\theta JR(peak)}$  cannot be considered a constant for all device operating conditions. However, in the high-current, low-voltage operating region (near the  $I_{C(max)}$  limit), the assumption of a constant  $R_{\theta JR(peak)}$  is usually reasonable. An indication of this can be seen in figure 14 where the manufacturer's published SOA (solid line) as well as the SOA determined from the actual peak junction temperature measured with an infrared microradiometer (dashed line) are shown for a device with no specified second breakdown limit. Within the specified thermal limit, this device can operate quite safely with  $T_{J(peak)}$  significantly below  $T_{J(max)}$ . In addition, the thermal limit as determined by the infrared microradiometer has a slope of approximately -1, which indicates a constant  $R_{\theta JR(peak)}$ . For this device then, the safe operating area is conservatively limited by the specified  $T_{J(max)}$ . It has also been observed that for most devices operating at or near  $I_{C(max)}$  (and thus limited by the -1 slope of the safe operating curve),  $T_{JR(peak)} \approx T_{JR(Avg)}$ , where  $T_{JR(Avg)}$  is measured using the  $V_{EB}$  emitter-only switching technique. This is because of the more uniform temperature distribution at high currents.

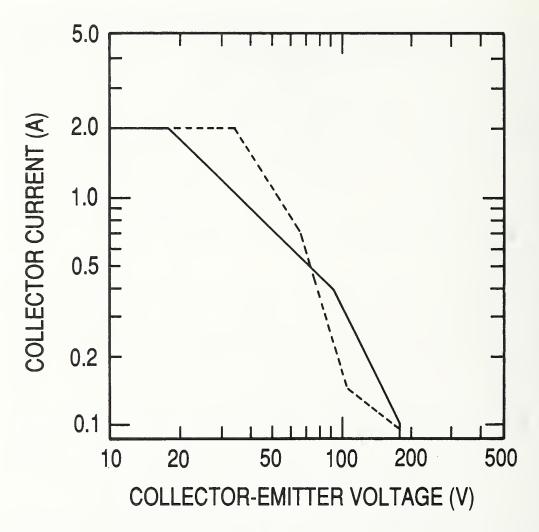

Second Breakdown Limit – The second breakdown limit of the SOA is usually determined by actually permitting a number of devices to enter second breakdown. The limit is usually set at values of  $I_C$  and  $V_{CE}$  somewhat less than those for which second breakdown occurs in the sample to add a margin of safety. Often, however, the thermal resistance of the device is not measured over this region because it is assumed that the thermal limit must continue with a slope of –1 and would thus be outside the second breakdown limit. As has been described, the low-current, high-voltage operating conditions, for which the published SOA is usually second-breakdown-limited,  $R_{\theta JR(peak)}$  is usually a strong function of operating conditions. This means that the published high-current, low-voltage thermal limit probably cannot be linearly extrapolated to the low-current, high-voltage operating region. In fact, the low-current, high-voltage conditions,  $R_{\theta JR(peak)}$  can be so large that the junction temperature exceeds the published safe maximum temperature well within the second-breakdown-limited safe-operating area. Thus, though the device may be protected from second breakdown in this region, it is not thermally protected.

An indication of the way variations in  $R_{\theta JR(peak)}$  can affect the actual SOA limits of a device that is severely second-breakdown-limited can be seen in figure 15. This figure shows the manufacturer's published SOA (solid line) as well as the experimentally determined SOA (dashed line) which was determined by using an infrared microradiometer to estimate the actual peak junction temperature. Within most of the specified thermal limit (specified slope of -1), this device can operate quite safely with  $T_{J(peak)}$  significantly below  $T_{J(max)}$  even though the true slope deviates from -1. For the low-current, high-voltage conditions, though, the actual thermal limit falls well within even the specified second breakdown limit, and thus this device should be thermally limited over almost all of its operating

Figure 14. The manufacturer-specified SOA limits (solid line) and the actual SOA limits determined by an infrared microradiometer (dashed line) for a power transistor which has no specified second breakdown limit.

Figure 15. The manufacturer-specified SOA limits (solid line) and the actual SOA limits determined by an infrared microradiometer (dashed line) for a device that is inadequately rated in the second breakdown region by the manufacturer.

range.

There are a number of electrical measurement techniques that can possibly be used to determine better the SOA limits for power transistors. These techniques can be used by manufacturers in determining the original specified limits or by users to determine if a particular device in a particular application is operating with a safe peak temperature and safe temperature distribution. These techniques are discussed below along with their possible applications to the determination of SOA limits.

# Relating the Chip Temperature to the Measured Temperature

The term "chip temperature" is ambiguous. The semiconductor chip does not have a single temperature, but has a distribution of temperature. An example of a relatively uniformly distributed surface temperature for a power MOSFET chip is shown in figure 16. An example of a nonuniform distribution for a power bipolar transistor is shown in figure 4. The surface temperature distributions of these two chips were measured with an infrared microradiometer. The electrically measured temperature for the uniform temperature MOSFET was 94 °C, only 4 °C below the actual peak temperature. The TSEP used for the MOSFET was the source-gate voltage at a low level current. The electrically measured temperature for the bipolar transistor of figure 4 was 64 °C, 16 °C below the peak temperature. For the bipolar transistor with a nonuniform temperature distribution, the electrically measured temperature is a poor representation of the actual peak temperature.

It is equally important to be able to determine when the temperature of a power transistor. It is equally important to be able to determine when the temperature distribution becomes nonuniform and thus when the standard electrically measured temperature is considerably below the peak temperature (electrical techniques typically average the temperature). In addition, the onset of temperature nonuniformity is usually a precursor to second breakdown and certainly enhances the possibility of premature device failure. One possible method of improving SOA limits would be to set the limit as determined either by the peak junction temperature or by the onset of temperature nonuniformity, whichever occurs first [25]. Because the onset of temperature nonuniformity will generally precede second breakdown, this SOA limit would generally fall within the usual second-breakdown limit.

Determination of Area of Power Generation and Peak Junction Temperature – It is possible to estimate the actual area of steady-state power dissipation for a power transistor [24] and thus determine the extent of current crowding in the device, because for at least the first 250  $\mu$ s of cooling, power transistors cool from steady-state according to one-dimensional heat flow theory. That is,

$$T(t) - T(0) = Kt^{1/2}, (7)$$

where

Figure 16. The temperature distribution of a power MOSFET measured with an automated infrared microradiometer.

$$K = \frac{2P}{\sqrt{\rho\pi kc} A_E},\tag{8}$$

and

T(t) = temperature at time t (°C),

T(0) = temperature at instant of power removal (°C),

t = time after removal of power (s),

P =power dissipation (W),

$\rho = \text{density (g/mm}^3),$

$k = \text{thermal conductivity (W/mm} \cdot ^{\circ}\text{C}),$

$c = \text{thermal capacity } (W \cdot s/g \cdot {}^{\circ}C), \text{ and }$

$A_E$  = area of power generation or effective active area (mm<sup>2</sup>).

A plot of temperature of the device as it is cooling versus  $t^{1/2}$  results in a straight line, and the area of power generation  $A_E$  can be found from the slope of that line K. This is demonstrated in figure 17, where the cooling rate of a power transistor is shown for two different operating conditions, but each for the same power level. The slope of the curve  $I_C = 0.2$  A gives an area of  $0.72 \text{ mm}^2$  and the slope of the curve for  $I_C = 0.5$  A gives  $A_E = 1.96 \text{ mm}^2$ . The total chip area is about 6.46 mm<sup>2</sup>. It is obvious that the junction temperature for the 0.2-A condition should be much hotter (same power, smaller area) than for the 0.5-A condition, and both the infrared and electrical measurements indicate this. It is important to note, though, that for the small-area case, the actual peak temperature (as indicated by an infrared microradiometer) is considerably higher than the electrical indication. The difference is not nearly so great for the large-area case, because, as has been mentioned, the electrical techniques for measuring temperature tend to average the junction temperature, and the more nonuniform the temperature, the more the electrically measured average temperature will deviate from the peak temperature.

Generally, it can be assumed that for chips of equal area, for the same power dissipation, the faster the rate of cooling during measurement, the more nonuniform is the chip temperature. Also, the more nonuniform the temperature, the less representative the electrically measured temperature is of the peak temperature.

It is possible to estimate better the peak temperature from the electrical measurement with some further data processing. It is necessary, though, to measure the cooling response of the device just as for extrapolating the temperature, as is shown in table 3. Because the semiconductor chip will cool one-dimensionally for the first 200 to 300  $\mu s$ , a plot of temperature versus the square root of time will be linear during this time. The slope of the linear curve is inversely proportional to the area being heated. If it is assumed also that

Figure 17. The electrically measured cooling response of a power transistor versus the square root of time for two different operating conditions for the same power (20 W). The infrared (IR) measured temperature is also noted for each operating condition. The ordinate is the junction temperature rise above the reference point (case) temperature.

the low-level measurement current takes on the same distribution within the chip during measurement that the heating current did during heating, then a simple relation can be developed between the calibration curve generated by externally heating the chip (with the measurement current uniformly distributed over the chip) and the measured TSEP during the actual measurement (with the measurement current nonuniformly distributed over the chip). The full procedure is described elsewhere [4].

An indication of the accuracy of this technique can be seen from figure 18 which shows the manufacturer-specified SOA, the SOA as determined using the modified electrical technique for determining the peak temperature, and the actual SOA determined using an infrared microradiometer for a 35-W triple-diffused transistor. Also shown is the SOA which would be determined using the standard electrical measurement technique. As has been discussed, for high current and low voltage, the specified SOA safely limits the junction temperature below  $T_{J(max)}$  for this device. However, as the voltage increases and the current decreases, the current begins to constrict and the specified SOA, although derated for second breakdown, is not derated sufficiently to account for the increased current constriction. Both the infrared-determined limit and the electrical-peak junction temperature limit show this.

Detection of Onset of Current Constrictions – There are a number of rather simple techniques that detect when the junction temperature (or equivalently the power density distribution) begins to become nonuniform.

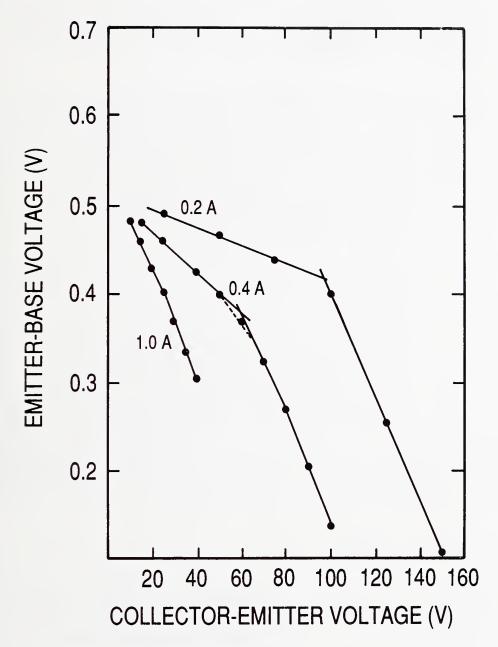

One possible method of detecting the onset of current nonuniformity is by monitoring  $V_{EB}$  at constant  $I_C$  as  $V_{CE}$  is increased [25]. The value of  $V_{EB}$  can be measured either near the end of a pulse (of 1-s duration, for instance) while the pulse is still on, or it can be measured after the pulse is removed from the device ( $\sim 10$  to  $20~\mu s$  after removal of power) with a small sampling current present. The latter is more sensitive to the onset of the temperature nonuniformity, and the measurement technique is nearly the same as making an  $R_{\theta JR}$  measurement using the emitter-only switching technique. A plot of  $V_{EB}$  versus  $V_{CE}$  for several values of  $I_C$  is shown in figure 19 for the same 35-W triple-diffused device shown previously. As the power is increased,  $V_{EB}$  initially falls linearly with  $V_{CE}$  because of a rather uniform increase in junction temperature. As the power density begins to be constricted, and the peak temperature begins to rise more rapidly,  $V_{EB}$  falls more rapidly. In each curve the break point from the initial linear region is the point where current crowding has begun to occur. This measurement is very easy to perform, and each datum point can be obtained with a single pulse of power applied to the device. An SOA curve based on the onset of current crowding can then be generated from these data.

# Reasons for Measuring Temperature

There are many reasons why one desires to know the operating temperature of a power device. Oftentimes, the specific reason for wanting to know the temperature dictates the type of measurement to be made.

If one wants to know accurately the actual operating temperature of a device in operation,

Figure 18. The manufacturer-specified SOA limits (solid line) and points along the measured SOA limits as determined by an infrared microradiometer, by the peak temperature electrical technique, and by the standard electrical technique. The number beside each standard electrical point is the percent of the total active area estimated to be dissipating power for each operating condition.

Figure 19. The measured  $V_{EB}$  at 20  $\mu$ s after the removal of a 1-s power pulse versus  $V_{CE}$  for a number of values of  $I_C$ . The onset of current crowding is noted by the initial break in the linear relation of  $V_{BE}$  versus  $V_{CE}$  as  $V_{CE}$  is increased.

then a careful measurement of the thermal resistance is required. This requires that dc measurements for pulse lengths approximating many seconds be made. Also, careful heat sinking and reference temperature measurement are required. In all, such a measurement is long and difficult. If one truly wants to know the dc temperature, there are really no shortcuts. Fortunately, such measurements can be made on a sampling basis on a few devices from a lot.

Oftentimes, one wants to "compare" devices to one another. Such is the case in performing thermal measurements for die-attach evaluation. Usually, devices of the same type differ in thermal resistance because of differences in die-attach quality. Well-bonded chips have a lower thermal resistance than poorly bonded chips. One can screen out poorly attached dice by comparing the thermal response of the devices. Since it is mainly the die attach that causes differences in the thermal resistance, it is advantageous to make the die attach as large a part of the measurement as possible. Heat flows from the chip to the die attach, to the heat spreader, to the package, to the heat sink. The dc thermal resistance measurement adds all of these factors to one another. The die-attach portion is a small part. If only the die-attach portion differs between devices, then one is looking for a small change in a big number if the dc thermal resistance is used. It would be ideal if one could measure only the "thermal resistance" of the die attach. Closer to practicality, but still close to ideal, it would be satisfactory to include only the thermal resistance of a few of the other heat transfer regions (chip, die attach, heat spreader, package, heat sink). This can be accomplished by heating the device with a short pulse (ranging from 10 to 100 ms for most device types), short enough that the heat energy only has time to flow through the chip and into the die-attach area. The pulse is stopped before significant heat enters into the heat spreader. In this way, the measured temperature is a function of the chip and the die attach and does not depend upon the other transfer elements. It must be emphasized, though, that all one is testing here is the die attach. Usually, the dc thermal characteristics follow the die-attach characteristics, but not always. Nevertheless, a pulsed measurement used to detect the right parameter, i.e., die-attach quality, is certainly better and easier than performing a dc test [13]. The advantages of this technique are summarized in table 4.

A die-attach test, or a theoretical calculation, does not replace the need for accurate characterization of the transient and dc thermal resistance of a device. The measurements do not have to be made on every device, but they must be made on enough devices to assure the manufacturer and user that well-bonded devices will have a thermal resistance less than some agreed-upon value. A true-life example of the need to know the dc thermal resistance is in order. A device user was experiencing a high failure rate in one particular bipolar transistor in a motor drive system. The particular device had two Darlington chips paralleled in a single TO-3 package. An obvious question was, "How well are the chips sharing the workload?" If one chip is poorly die bonded compared to the other, then it may end up hogging all the current due to the positive thermal feedback effects for which bipolar transistors are well known. Pulsed tests were made out to pulses 1 s in length, and no particular differences were noticed between devices. Also, the 1-s measurements indicated that the dc thermal resistance was within specifications when using theoretical thermal response curves. Careful dc thermal resistance measurements, though, revealed

# Advantages of Thermal Response Testing for Die Attachment

# The technique is:

- SENSITIVE It can be used to detect contiguous voids as small as 10 to 15% of the chip bonding area.

- CONVENIENT It can be performed on finished devices and requires minimal, if any, heat sinking.

- FAST It can be automated.

- ADAPTABLE It can be used for testing a wide variety of device types and structures.

that there was in fact a very wide variation in the thermal resistance of different devices. Subsequent measurements made with an infrared microradiometer revealed that in fact, oftentimes, only one of the chips was dissipating power while its parallel mate was along just for the ride. Qualitative infrared measurements showed that the pulsed measurements were accurate; the chips shared power equally for single pulses at least as long as 1 s. The problem was that because of the relative locations in the package of the two chips and the asymmetry of the heat spreader in the TO-3 package, the thermal resistance of one of the chips to the heat sink (the one that failed 80 percent of the time) was greater than that of the other chip. Thus, even if each chip shared evenly in the workload, one would be hotter (and thus eventually could not share equally because of the positive thermal feedback of bipolar transistors). The temperature rise during a single pulse was not enough to cause the chips not to share the pulse.

## Measurement of Integrated Power Devices

The measurement of integrated power structures presents special difficulties. The major problem is that a simple, well-defined and well-behaved TSEP often is not available at the device terminals. Even if a TSEP is easily available, it may not be sensing the temperature at the desired region of the chip.

For instance, consider perhaps the simplest integrated power circuit, the monolithic, bipolar Darlington transistor. A circuit schematic of a typical Darlington is shown in figure 20. The actual chip for this Darlington is shown in figures 4 and 5. The output transistor Q2 dissipates the large fraction of the power in this device and is expected to be the hottest area on the chip. The emitter-base voltage is typically used as a TSEP for bipolar transistors, but for the Darlington, the emitter-base voltage measured at the terminals of the device is the sum of the emitter-base voltage of the input transistor, Q1, and the output transistor, Q2. Under most circumstances, then, the temperature measured using the emitter-base terminal voltage of the Darlington is some average temperature of the input and output device. There are no readily available temperature-sensitive parameters that one can use that only senses the output transistor temperature. This example is perhaps the simplest example of the problems associated with measuring the temperature of integrated devices.

Although this measurement cannot be made directly, an indirect determination of the Darlington output transistor thermal resistance using the emitter-only switching technique and a simple equation has been developed [26]. The procedure employs two separate measurements, one of the average temperature of the input and output transistors and the other of the temperature of the input transistor only. The method relies upon the presence of the two resistors, R1 and R2, and upon the fact that for very small values of emitter-base current, only the input transistor is active. This is because the voltage drop across R2 for very small currents may be made less than a diode forward voltage drop. This keeps transistor Q2 off. The method is outlined in table 5.

The Darlington example is indicative that perhaps simple thermal resistance measurements may not suffice for complex integrated power circuits. Many such circuits do have isolation

Figure 20. Schematic of Darlington transistor.

Procedure for Measuring the Temperature of Darlington Transistors (see fig. 20 for Darlington details)

- 1. Using the emitter-base voltage of the Darlington as the TSEP, use the emitter-only switching method and a measurement current small enough to only turn on the input transistor (Q1) to measure the temperature of Q1. The measurement current is selected to be small enough that the potential drop across R2 is less than about 0.3 V. Call this temperature T(1).

- 2. Increase the measurement current such that both transistors Q1 and Q2 are turned on during measurement. The current should be large enough that the potential drop across R2 is greater than about 1.0 V. An average temperature of Q1 and Q2 is measured with this step. Call the temperature measured T(1+2).

- 3. The temperature T(2) of the output transistor Q2 is calculated as T(2) = 2T(1+2) T(1).

diodes, but the diode is usually not sensing the temperature of the power elements, the temperature of most interest.

Power Transistor Thermal Standardization Activities

Presently active in the improvement and standardization of thermal characterization techniques for power transistors are the Electronic Industries Association's JEDEC JC-25, JC-50.1, and JC-13.1 Committees on Transistors, GaAs Reliability & Quality Standards, and Government Liaison for Discrete Devices, respectively, and the Department of Defense through the Defense Electronics Supply Center (see table 6 for details). Technical expertise and a willingness to participate actively in the development of standards are always welcomed by the various groups involved in these efforts.

# II. INTEGRATED CIRCUITS [27]

#### Introduction

The thermal characterization of packaged integrated circuits generally takes one of three forms. They are computer simulations and both direct (infrared) and indirect (electrical) measurements of the integrated circuit chip surface/junction temperature [28]. Due to the inherent difficulties in analyzing and measuring the thermal properties of active integrated circuit chips, an approach using specifically designed thermal test chips for evaluating new packaging schemes is finding wide acceptance in the industry. The focus of this section is on the thermal characterization of single-chip ceramic packages, although there is some discussion pertaining to plastic packages and hybrids.

Thermal resistance has been used over the years as an aid to device manufacturers and users for calculating the junction temperature of operating devices. The concept of a unique value of thermal resistance is based upon an analogy between the electrical and thermal properties of materials, with temperature, power dissipation, and thermal resistance being analogous to voltage, current, and electrical resistance, respectively. The thermal resistance  $(R_{\theta JR})$  is defined as follows:

$$R_{\theta JR} = \frac{(T_J - T_R)}{P_{tJ}} \tag{9}$$

where

$R_{\theta JR}$  = thermal resistance between the junction and the reference point (usually on the device case or in the surrounding ambient) (°C/W),

$T_J, T_R =$  temperature of the junction and the reference point, respectively, (°C), and

$P_H$  = power dissipation in the device (W).

In applying the electrical analogy to the thermal problem and in using eq (9), it is implicitly assumed that uniform electrical power and temperature distributions exist across

# Power Transistor Thermal Test Method Standardization

- 1. "Thermal Resistance Measurements for Bipolar Transistors (Emitter-to-Base Forward Voltage, Emitter-Only Switching Method)," Method 3131.2, MIL-STD-750C Test Methods for Semiconductor Devices, Dept. of Defense, Washington, DC.

- 2. "Thermal Impedance Measurements for GaAs MESFETs (Constant Current Forward-Biased Gate Voltage Method)," Method 3104, MIL-STD-750C Test Methods for Semiconductor Devices, Dept. of Defense, Washington, DC.

- 3. "Thermal Impedance Measurements for Insulated Gate Bipolar Transistors (Gate-to-Emitter On-Voltage Method)," Method 3103, MIL-STD-750C Test Methods for Semiconductor Devices, Dept. of Defense, Washington, DC.

- 4. "Thermal Impedance Measurements for Vertical Power MOSFETs (Source-to-Drain Diode Voltage Method)," Method 3161, MIL-STD-750C Test Methods for Semiconductor Devices, Dept. of Defense, Washington, DC.

- 5. "Thermal Resistance Measurements of Conduction Cooled Power Transistors," EIA RS-313-B, Electronic Industries Association, Washington, DC.

- 6. "Low Frequency Power Transistors (Part 4 Thermal Characteristics)," JEDEC Standard No. 10, Electronic Industries Association, Washington, DC.

- 7. "Power MOSFET's (Chapter 4 Thermal Characteristics)," JEDEC Standard No. 4, Electronics Industry Association, Washington, DC.