# ENSURING AMERICAN LEADERSHIP IN MICROELECTRONICS

## **HEARING**

BEFORE THE

# COMMITTEE ON SCIENCE, SPACE, AND TECHNOLOGY

OF THE

### HOUSE OF REPRESENTATIVES

ONE HUNDRED SEVENTEENTH CONGRESS

FIRST SESSION

DECEMBER 2, 2021

Serial No. 117-40

Printed for the use of the Committee on Science, Space, and Technology

Available via the World Wide Web: http://science.house.gov

U.S. GOVERNMENT PUBLISHING OFFICE  ${\bf WASHINGTON} \ : 2023$

46-150PDF

#### COMMITTEE ON SCIENCE, SPACE, AND TECHNOLOGY

HON. EDDIE BERNICE JOHNSON, Texas, Chairwoman

ZOE LOFGREN, California

SUZANNE BONAMICI, Oregon

AMI BERA, California

HALEY STEVENS, Michigan,

Vice Chair

MIKIE SHERRILL, New Jersey

JAMAAL BOWMAN, New York

MELANIE A. STANSBURY, New Mexico

BRAD SHERMAN, California

ED PERLMUTTER, Colorado

JERRY MCNERNEY, California

PAUL TONKO, New York

BILL FOSTER, Illinois

DONALD NORCROSS, New Jersey

DON BEYER, Virginia

CHARLIE CRIST, Florida

SEAN CASTEN, Illinois

CONOR LAMB, Pennsylvania

DEBORAH ROSS, North Carolina

GWEN MOORE, Wisconsin

DAN KILDEE, Michigan

SUSAN WILD, Pennsylvania

LIZZIE FLETCHER, Texas

FRANK LUCAS, Oklahoma, Ranking Member

MO BROOKS, Alabama

BILL POSEY, Florida

RANDY WEBER, Texas

BRIAN BABIN, Texas

ANTHONY GONZALEZ, Ohio

MICHAEL WALTZ, Florida

JAMES R. BAIRD, Indiana

DANIEL WEBSTER, Florida

MIKE GARCIA, California

STEPHANIE I. BICE, Oklahoma

YOUNG KIM, California

RANDY FEENSTRA, Iowa

JAKE LATURNER, Kansas

CARLOS A. GIMENEZ, Florida

JAY OBERNOLTE, California

PETER MEIJER, Michigan

JAKE ELLZEY, TEXAS

MIKE CAREY, OHIO

### C O N T E N T S

#### December 2, 2021

|                                                                                                                                                              | Page     |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| Hearing Charter                                                                                                                                              | 2        |  |

| Opening Statements                                                                                                                                           |          |  |

| Statement by Representative Eddie Bernice Johnson, Chairwoman, Committee on Science, Space, and Technology, U.S. House of Representatives  Written Statement | 11<br>12 |  |

| Statement by Representative Frank Lucas, Ranking Member, Committee on Science, Space, and Technology, U.S. House of Representatives                          | 12<br>15 |  |

| Witnesses:                                                                                                                                                   |          |  |

| Dr. Ann Kelleher, Executive Vice President and General Manager of Technology Development, Intel Oral Statement                                               | 17       |  |

| Written Statement                                                                                                                                            | 19       |  |

| Mr. Manish Bhatia, Executive Vice President, Global Operations, Micron Technology Inc.                                                                       |          |  |

| Oral Statement                                                                                                                                               | 32       |  |

| Written Statement                                                                                                                                            | 34       |  |

| Oral Statement                                                                                                                                               | 39       |  |

| Written Statement                                                                                                                                            | 41       |  |

| Dr. Mung Chiang, Executive Vice President and Dean of Engineering College, Purdue University Oral Statement                                                  | 66       |  |

| Written Statement                                                                                                                                            | 68       |  |

| Discussion                                                                                                                                                   | 75       |  |

| Appendix I: Answers to Post-Hearing Questions                                                                                                                |          |  |

| Dr. Ann Kelleher, Executive Vice President and General Manager of Technology Development, Intel                                                              | 124      |  |

| Mr. Manish Bhatia, Executive Vice President, Global Operations, Micron Technology, Inc.                                                                      | 137      |  |

| Dr. Michael Witherell, Director, Lawrence Berkeley National Laboratory                                                                                       | 148      |  |

| Dr. Mung Chiang, Executive Vice President and Dean of Engineering College,<br>Purdue University                                                              | 151      |  |

| Appendix II: Additional Material for the Record                                                                                                              |          |  |

| Letters submitted by Representative Eddie Bernice Johnson, Chairwoman,<br>Committee on Science, Space, and Technology, U.S. House of Representa-<br>tives    |          |  |

| "Ensuring American Leadership in Microelectronics," Tim Powderly, Senior Director, Government Affairs, Apple                                                 | 164      |  |

| dustry," John Dallesasse, et al., American Semiconductor Academy                                                                                             | 166      |  |

| 1 1                                                                    |      |

|------------------------------------------------------------------------|------|

|                                                                        | Page |

| Document submitted by Representative Paul Tonko, Committee on Science, |      |

| Space, and Technology, U.S. House of Representatives                   |      |

| "Supporting the Future of US-Based Semiconductor Manufacturing: Inno-  |      |

| vation, Technology Development & Translation, And Workforce            |      |

| Enablement," F. Shadi Shahedipour-Sandvik, Robert Geer, Nathaniel      |      |

| Cady, Nicholas Querques, the State University of New York              | 204  |

## ENSURING AMERICAN LEADERSHIP IN MICROELECTRONICS

#### THURSDAY, DECEMBER 2, 2021

House of Representatives, Committee on Science, Space, and Technology,  $Washington,\,D.C.$

The Committee met, pursuant to notice, at 10:03 a.m., via Zoom, Hon. Eddie Bernice Johnson [Chairwoman of the Committee] presiding.

#### U.S. HOUSE OF REPRESENTATIVES COMMITTEE ON SCIENCE, SPACE, AND TECHNOLOGY HEARING CHARTER

Ensuring American Leadership in Microelectronics

Thursday, December 2, 2021 10:00 am – 12:00 pm Zoom

#### **PURPOSE**

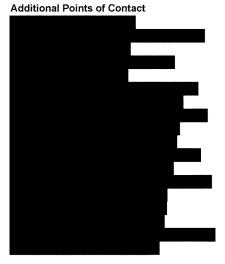

On Thursday, December 2, 2021, the Committee on Science, Space, and Technology will hold a hearing to examine the status of U.S. leadership in advanced semiconductor development and manufacturing; to discuss how new investments and partnership models can support continued U.S. leadership; and to explore the role of the federal government in supporting domestic semiconductor innovation and manufacturing throughout the supply chain.

#### WITNESSES

- Dr. Ann Kelleher, Executive Vice President and General Manager of Technology Development, Intel

- Mr. Manish Bhatia, Executive Vice President, Global Operations, Micron Technology, Inc

- Dr. Michael Witherell, Director, Lawrence Berkeley National Laboratory

- **Dr. Mung Chiang**, Executive Vice President and John A. Edwardson Dean, College of Engineering, Purdue University

#### OVERARCHING QUESTIONS

- What is the state of U.S. leadership in advanced microelectronics R&D and manufacturing in the United States?

- Why is it important for the United States to maintain leading capabilities in both R&D and manufacturing of advanced microelectronics? What are the consequences of a loss of leadership?

- What is the appropriate role of the Federal government in supporting microelectronics research, innovation, and domestic manufacturing? How can the Federal government most effectively partner with the private sector and the research community?

- To what extent does the CHIPS for America Act address what is needed to maintain U.S. leadership in microelectronics innovation? Are any updates to CHIPS or additional legislation necessary to ensure a coordinated, transparent and effective Federal partnership with the private sector, universities, and National Labs to advance U.S. microelectronics innovation and manufacturing?

#### MICROELECTRONICS OVERVIEW

Advanced microelectronics are a primary driver of economic growth and scientific advancement. Microelectronics is a term describing all aspects of the miniaturization of electronic circuits and components, from fundamental research to design to manufacturing. Semiconductors are a subset of microelectronics. Most modern semiconductors are integrated circuits, also called "chips", which are sets of miniaturized electronic circuits composed of active discrete devices (e.g., transistors), passive devices (e.g., capacitors), and their interconnections, all of which are layered on a thin wafer of semiconductor material (e.g., silicon). These chips enable nearly everything in our modern lives —from smartphones and cars to nuclear weaponry.

Semiconductors can be classified into three major product groups based on function:<sup>1</sup>

- <u>Microprocessors and Logic Devices</u> are the integrated circuits functioning on binary codes (0 and 1) that are used for the interchange and manipulation of data in computing.

- Memory Devices are used to store information. This segment includes dynamic randomaccess memory (DRAM), a common type of memory used to store the data or program code needed by a computer processor to function.

- <u>Discrete, Analog, and Other (DAO)</u> semiconductors transmit, receive, and transform

information dealing with continuous parameters, such as temperature. For example,

analog devices are used to translate analog signals, such as light, touch, and voice, into

digital signals. Discretes, such as transistors and diodes, perform a single electrical

function on each chip.

#### MICROELECTRONICS INNOVATION IN THE UNITED STATES

The United States has a long history of innovation in microelectronics. U.S. government investments in research helped lead to the invention of early computers and transistors in the 1940s, as well as the first integrated circuit in the 1950s. In the 1980s, the rapid rise of Japan's semiconductor industry led the federal government to establish a research consortium to support U.S. competitiveness in semiconductor technology, also known as SEMATECH. From 1988 through 1996, Congress provided approximately \$870 million to SEMATECH through the Defense Advanced Research Projects Agency (DARPA), which was generally matched by industry contributions. While the Government Accountability Office found that SEMATECH had a significant impact on U.S. semiconductor manufacturing and R&D performance, the SEMATECH board of directors ultimately declined additional federal funding in 1996 and the consortium was later absorbed into the New York Polytechnic Institute in 2015.

<sup>&</sup>lt;sup>1</sup> Antonio Varas et al., "Strengthening the Global Semiconductor Supply Chain in an Uncertain Era," <u>Semiconductor Industry Association</u>, April 2021.

<sup>&</sup>lt;sup>2</sup> Michaela Platzer et al., "Semiconductors: U.S. Industry, Global Competition, and Federal Policy," <u>Congressional Research Service</u>, October 26, 2020.

<sup>&</sup>lt;sup>4</sup> "Federal Research: Lessons Learned from SEMATECH," <u>U.S. General Accounting Office</u>, September 28, 1992.

The Federal Government continues to invest in semiconductor research across many different agencies and mission areas. The U.S. semiconductor industry has continued to lead the world in R&D spending, investing nearly one-fifth of its annual revenue in R&D each year. In 2020, the U.S. semiconductor industry investment in R&D totaled \$44.0 billion.

#### "Moore's Law"

The semiconductor industry has a rapid internal product development cycle. This was first described by Gordon Moore, then R&D Manager for Fairchild Semiconductor, in 1965.<sup>7</sup> Moore's law, as his observation later became known, states that the number of transistors that can be cost-effectively included on an integrated circuit will double every 18 months to two years, making chips smaller, faster, and cheaper. This observation held for decades, in part because of the industry's high level of research and investment spending. However, this two-dimensional scaling of the chip is reaching its physical limits as chip complexity has increased due to new applications such as artificial intelligence, 5G, and the internet of things. The industry can no longer rely solely on this process to make the necessary generational improvements that will enable future chip iterations, including breakthroughs in energy efficiency, new materials, are more. Long term grown will require fundamental breakthroughs in microelectronics technology.

#### THE GLOBAL SEMICONDUCTOR LANDSCAPE

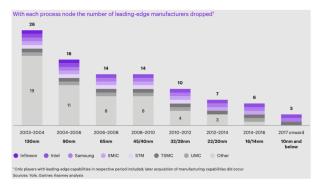

Semiconductor production includes three segments: (1) design, (2) manufacturing/fabrication, and (3) assembly, testing, and packaging (ATP). In some cases, these steps are all performed by a single company, called an integrated device manufacturer (IDM). Major U.S. headquartered IDMs include Texas Instruments, Intel, and Micron. Other semiconductor companies, called fabless firms, only do design in-house. Fabless firms purchase fabrication services from a semiconductor factory and ATP services from an outsourced semiconductor assemble and test company. Semiconductor factories, also referred to as fabs or foundries, are often characterized by the size of the wafer that chips are printed on and the size of the transistor gate length printed on each chip. Only a small number of fabs—none of which reside in the United States—produce the most state-of-the-art semiconductors. Additionally, the semiconductor production process requires several types of inputs, including materials, manufacturing equipment, software, and intellectual property, some of which is produced only outside of the United States.

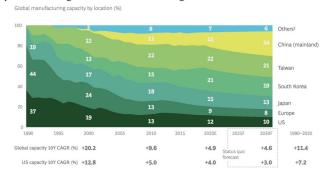

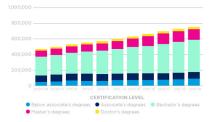

While the Unites States is the current global leader is semiconductor sales and R&D, the competitive landscape for semiconductor development is shifting. In 2020, the U.S.

<sup>&</sup>lt;sup>5</sup> "2021 State of the U.S. Semiconductor Industry," <u>Semiconductor Industry Association</u>, June 2021.

<sup>&</sup>lt;sup>6</sup> Ibid

<sup>&</sup>lt;sup>7</sup> Gordon E. Moore, "Cramming More Components Onto Integrated Circuits," *Electronics Magazine*, Vol. 28, No. 8, April 19, 1965, accessed through Georgia Tech.

<sup>8 &</sup>quot;The Decadal Plan for Semiconductors" Semiconductor Research Corporation, January 2021.

<sup>&</sup>lt;sup>9</sup> Platzer et al., "Semiconductors: U.S. Industry, Global Competition, and Federal Policy."

semiconductor industry accounted for 47 percent of global semiconductor sales. <sup>10</sup> Furthermore, the United States leads in many parts of the semiconductor market, including manufacturing equipment and semiconductor design. 11 However, over the last few decades, much of the U.S. manufacturing capacity has been offshored. The U.S. share of global semiconductor manufacturing decreased from 37 percent in 1990 to just 12 percent today. 12 Much of this capacity has moved to Taiwan, South Korea, and Japan, and China. 13 For example, Taiwan accounts for 47 percent of the global capacity to manufacture advanced logic semiconductors, such as those used in smart phones or data centers. 14

China, which accounts for roughly 25 percent of global consumption of semiconductors (roughly equal to that of the United States), is also heavily investing in domestic semiconductor capacity. 15 China is investing \$150 billion with the stated goal of gaining 40 percent of the world's new manufacturing capacity by 2030. 16 While the country remains two to three generations behind in advanced semiconductor manufacturing capacity, 17 China has demonstrated the ability to rapidly close technology gaps.

#### Supply Chains, Disruptions, and Shortages

Demand for semiconductor output has grown consistently over the last two decades, with the Semiconductor Industry Association (SIA) predicting a 19.7 percent increase in global sales in 2021 and a subsequent 8.8 percent increase in 2022.18

From design to final sale, a single chip can progress through more than 1,000 production steps and cross 70 international borders.<sup>19</sup> When businesses started to close due to the COVID-19 pandemic in 2020, there was an abrupt and cascading global shortage of semiconductors. This shortage was primarily caused by significant swings in demand throughout the pandemic. Chip manufactures first slowed production due to lockdowns and a reduction in demand from their customers, who canceled their chip orders assuming a lengthy economic downturn. However,

<sup>10 &</sup>quot;2021 State of the U.S. Semiconductor Industry."

<sup>&</sup>lt;sup>11</sup> Antonio Varas et al., "Government Incentives and U.S. Competitiveness in Semiconductor Manufacturing," Semiconductor Industry Association, September 2020. <sup>12</sup> Ibid.

<sup>&</sup>lt;sup>13</sup> South Korea specializes in all production steps, while Taiwan is dominant in most advanced manufacturing and ATP. Japan specializes in manufacturing equipment. European nations, especially the Netherlands, the United Kingdom, and Germany, specialize in manufacturing equipment, materials, and core IP. Currently, China is the leader in ATP and raw materials.

<sup>14</sup> Varas et al., "Government Incentives and U.S. Competitiveness in Semiconductor Manufacturing."

15 Varas et al., "Strengthening the Global Semiconductor Supply Chain in an Uncertain Era."

<sup>&</sup>lt;sup>16</sup> Stephen Ezell, "Moore's Law Under Attack: The Impact of China's Policies on Global Semiconductor Innovation," the Information Technology and Innovation Foundation, February 18, 20201.

17 Debbie Wu et al., "Why the World Is Short of Computer Chips, and Why It Matters," Washington Post, April 21,

<sup>18 &</sup>quot;Global Semiconductor Sales Increase 1.9% Month-to-Month in April; Annual Sales Projected to Increase 19.7% in 2021, 8.8% in 2022," Semiconductor Industry Association, press release, June 9, 2021.

Saif Khan, "The Semiconductor Supply Chain Assessing National Competitiveness," the Georgetown Center for Security and Emerging Technologies, January 2021.

chipmakers soon saw surging demand in other sectors as new activities become more commonplace, such as remote healthcare, work-at-home, and virtual learning. When economic forecasts proved wrong, the original customers re-ordered chips, creating a significant backlog.

Several other events spurred the shortage. Stockpiling by certain companies and industries before the pandemic—especially Chinese companies seeking to weather U.S. trade restrictions—further tightened supply. Natural disasters also impacted chip manufacturing. For example, a Renesas plant in Japan, which primarily serves car manufacturers, had its production significantly delayed due to a fire. <sup>20</sup> Finally, truck shortages and global shipping backups have significantly stalled inputs that go into the manufacturing of semiconductors and their delivery to the customer.

The shortage affected many downstream sectors, such as car manufacturing and consumer electronics. For example, a General Motors plant in Kansas City was closed from February to September due to a lack of chips.<sup>21</sup> Notably, many semiconductor firms are no longer manufacturing the types of legacy chips that are used in vehicles and home appliances, instead focusing capacity on cutting-edge designs. This trend has further exacerbated shortages. Some analysts believe that the most problematic chip shortages will begin to ease in the third or fourth quarter of 2021, but it could take through 2022 for shortages to end.<sup>22</sup>

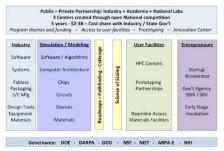

#### THE CHIPS FOR AMERICA ACT

To re-shore chip manufacturing and to advance U.S. competitiveness in microelectronics, in December 2020 Congress enacted the *Creating Helpful Incentives to Produce Semiconductors* for America Act, or the CHIPS for America Act.<sup>23</sup> The CHIPS for America Act establishes a grant program at the Department of Commerce that would incentivize new domestic semiconductor manufacturing facilities and workforce development. It also creates a multilateral semiconductors security fund to support development of measurably secure supply chains, as well as a Department of Commerce study to analyze the capabilities of the U.S. industrial base to support the national defense in the light of significant global supply chain interdependencies.

The law also supports several research and development related activities. First, it establishes an interagency working group, advised by an industrial advisory committee, to develop a national strategy for semiconductor research and development. The Act directs the Department of Commerce to support semiconductor R&D through multiple mechanisms, including a National Semiconductor Technology Center (NSTC) to conduct research and prototyping of advanced

<sup>&</sup>lt;sup>20</sup> "Japanese carmakers assess impact of fire at Renesas chip plant," Reuters, March 21, 2021.

<sup>&</sup>lt;sup>21</sup> Carlos Moreno, "Workers Return To GM's Fairfax Plant On Monday, Months After Mass Layoffs," <u>NPR</u>, September 20, 2021.

<sup>&</sup>lt;sup>22</sup> Samuel Moore, "How and When the Chip Shortage Will End, in 4 Charts," <u>IEEE</u>, June 21, 2021.

<sup>&</sup>lt;sup>23</sup> Creating Helpful Incentives to Produce Semiconductors for America Act (CHIPS for America Act), Title XCIV, The William M. (Mac) Thornberry National Defense Authorization Act for Fiscal Year 2021, H.R. 6395, 116<sup>th</sup> Congress.

chips, a Manufacturing USA Institute for domestic semiconductor manufacturing, and a center on advanced semiconductor packaging. The Act directs the National Institute of Standards and Technology (NIST) specifically to conduct metrology research to accelerate the development of next generation semiconductors. Finally, the Act requires the Department of Defense to establish a national network for microelectronics research and development to support prototyping new semiconductor technologies for commercialization—commonly referred to as the "microelectronics commons."

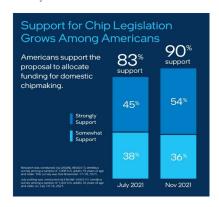

Funding for the CHIPS Act, a total of \$52 billion over five years, has been passed by the Senate as part of the *U.S. Innovation and Competition Act* (USICA). The House has passed several pieces of legislation within scope of USICA. House and Senate Leadership have called for a formal conference on the package of competitiveness bills.

The Department of Commerce has expressed its intent to delegate authority for the grant programs authorized in CHIPS to NIST. NIST has significant technical expertise to build on but will need additional expertise and administrative capabilities and staffing to implement the programs. The agency has actively engaged with the private sector and other stakeholders for months, in anticipation of the CHIPS funding being enacted.

## CONTINUING CHALLENGES TO U.S. LEADERSHIP IN MICROELECTRONICS RESEARCH AND MANUFACTURING

#### **Driving Transformational Advancements**

The coming end of Moore's Law, as previously stated, presents major technological challenges and opportunities for progress in microelectronics. Future progress and innovation will require an approach that advances relevant materials science; device technologies; processing and packaging technologies; manufacturing technologies; circuit, chip, and system architecture; and software system and algorithm development in a co-design fashion.

The Department of Energy (DOE) has a decades-long history of working directly with industry and academia to drive scientific advancements in the areas mentioned above. DOE's microelectronics research is underpinned by its National Laboratory complex, as illustrated by the Department's recent decision to provide \$54 million to support National Laboratory-based projects to advance research in microelectronics. <sup>24</sup> These activities are part of a longer term, crosscutting microelectronics initiative that, as articulated by a 2018 report from the DOE Office of Science, exemplifies a "fundamental rethinking" in what is needed to advance "the science behind the materials, synthesis and placement technologies, architectures, and algorithms." Key to the Department's justification for its ambitions in microelectronics are its scientific user

<sup>24 &</sup>quot;DOE Announces \$54 Million to Increase Energy Efficiency in Microelectronics Technologies," <u>U.S. Department of Energy</u>, August 25, 2021.

25 "Basic Research Needs for Microelectronics: Report of the Office of Science Workshop on Basic Research Needs

<sup>&</sup>lt;sup>25</sup> "Basic Research Needs for Microelectronics: Report of the Office of Science Workshop on Basic Research Needs for Microelectronics, October 23-25, 2018," <u>U.S. Department of Energy</u>.

facilities, which both rely on and help drive advancements in microelectronics. These facilities, which are utilized annually by thousands of academic and industry researchers, include particle detectors, microscopes, X-ray and neutron sources, data centers, networks, and high-performance computers.

#### Bridging the "Lab-to-Fab" Gap

There is a general concern that the United States has underinvested in maturing breakthrough ideas for semiconductor technology to the point of manufacturing them domestically. This "lab to fab" innovation gap, known generally as the "valley of death" for technological innovation, is the phase between developing a concept or a product and scaling it into a profitable innovation that the market adopts. This phase often leads to early-stage technologies being shelved indefinitely or prematurely abandoned. Importantly, funding is not the only challenge in bridging the valley of death. Companies need access to facilities, tools, and personnel suitable for demonstrating the ability to produce an innovation at commercial scale. Even well-funded startups struggle to secure time at fabs and foundries to test their products, as they compete with larger companies for access. <sup>27</sup>

There is an earlier valley of death from fundamental research to prototyping. Many different government agencies and other groups support early-stage semiconductor research, from the National Science Foundation to the Semiconductor Research Corporation. However, many of these funding sources stop short of supporting prototyping. Only a few U.S.-headquartered companies have the resources, infrastructure, and expertise to translate basic research into commercial production. Venture capital firms have also drastically reduced their funding to hardware companies in recent years in favor of software-driven companies with fast time-to-market and low capital expenditures.<sup>28</sup> The DOD led microelectronics commons was conceived to address this earlier gap.

#### **Maintaining Competitiveness in Advanced Packaging**

In addition to manufacturing, the United States has lost market share in advanced packaging. This process, called assembly, testing, and packaging (ATP), involves cutting a finished wafer into individual chips. Each chip is mounted on a frame with wires that connect the chip to external devices and enclosed in a protective casing. Traditionally, ATP was shipped overseas to countries with comparatively low wages because it is the most labor-intensive part of the manufacturing process. As a result, U.S. industry currently only has 2 percent of the global market share in ATP services.<sup>29</sup> R&D in advanced packaging in the United States has also lagged as relatively few research institutions focus on the topic as a priority.

<sup>&</sup>lt;sup>26</sup> "Nanomanufacturing--Emergence and Implications for U.S. Competitiveness, the Environment, and Human Health," <u>U.S. Government Accountability Office</u>, May 19, 2014.

<sup>&</sup>lt;sup>27</sup> "American Innovation, American Growth: A Vision for the National Semiconductor Technology Center (NSTC)."

<sup>&</sup>lt;sup>28</sup> Dr. Walden Rhines, "Predicting Semiconductor Business Trends After Moore's Law," <u>SemiWiki.com</u>, 2019.

Many observers now believe breakthroughs in packaging will be key to improving chip efficiency beyond Moore's law because the packaging provides an alternative avenue for innovation in density and size of products. Other countries are heavily investing to get an advantage in next generation packaging. For example, the Taiwan Semiconductor Manufacturing Company (TSMC) announced in June 2021 that it would partner with 20 Japanese companies to establish an R&D center dedicated to advanced packaging design.<sup>30</sup>

#### **Building a Workforce**

While federal investments to grow domestic semiconductor manufacturing capacity will likely increase the number of semiconductor-related jobs in the United States, <sup>31</sup> concerns remain about the U.S. capacity to fill those jobs. As of 2018, there were over 4,000 open technical positions in the United States among prominent semiconductor firms. <sup>32</sup> The pandemic has only worsened the industry's supply of high skilled workers. In comments to NIST on strengthening the semiconductor workforce, the Semiconductor Industry Association (SIA) listed the following workforce-related challenges: a lack of supply of U.S. workers with advanced education, a lack of academic programs supporting emerging technologies, high competition among tech industries for high skilled workers, low awareness of the semiconductor industry among graduate students in STEM, a lack of hands-on training to prepare graduates for work on the manufacturing floor, a lack of diversity in STEM, and retention issues due to cultural differences between young workers and the older workforce.<sup>33</sup>

While the CHIPS for America Act addresses some of these issues through its incentive program for workforce training and through its newly established R&D programs, targeted workforce programs may be necessary to establish a lasting microelectronics workforce.

#### **Accessing Material Inputs**

Increased production of semiconductors in the United States would require increased domestic production of materials (including critical materials), chemicals, and gases. Regarding critical materials, it is often a difficult and lengthy process to establish domestic critical mineral production. A June 2021 report from the White House found that a reasonable estimate for this process is "not less than ten years." Domestic production of other materials, chemicals, and gases used in semiconductor manufacturing is also somewhat limited. Both the U.S. Geological

<sup>30</sup> Scott Foster, "TSMC eyes 3D chip packaging edge in Japan," Asia Times, June 21, 2021.

<sup>31 &</sup>quot;The Positive Impact Of The Semiconductor Industry On The American Workforce And How Federal Industry Incentives Will Increase Domestic Jobs," <u>Semiconductor Industry Association</u>, webinar, May 2021.

32 "Challenges and Opportunities Facing Semiconductor Workforce," <u>Semiconductor Industry Association</u>, May 30, 2018.

<sup>33 &</sup>quot;Current and Future Workforce Needs to Support a Strong Domestic Semiconductor Industry," <u>Semiconductor Industry Association</u> comments to National Institute of Standards and Technology, August 15, 2018.

34 "Building Resilient Supply Chains, Revitalizing American Manufacturing, And Fostering Broad-Based Growth,"

<sup>34 &</sup>quot;Building Resilient Supply Chains, Revitalizing American Manufacturing, And Fostering Broad-Based Growth," the White House, 100-Day Reviews under Executive Order 14017, June 2021.

Survey and NIST maintain lists of materials and gases used in semiconductor production.<sup>35</sup> With the exception of a few of these materials, such as Helium and Silicon, most of these materials are not produced or refined in the United States. 36 A lack of domestic access to these materials has further exacerbated supply chain delays.

#### **Overcoming Environmental Challenges**

The semiconductor industry faces significant environmental challenges. It both contributes to and is affected by climate change. It takes a significant amount of energy to produce semiconductors. Companies need to take raw silicon then melt and purify it—a process that produces a significant amount of carbon. For example, TSMC, the current largest chip producer in the world, was responsible for 15 million tons of carbon in 2020.<sup>37</sup> The Semiconductor Research Corporation, a nonprofit organization that funds semiconductor R&D, has committed to funding research to produce sustainable, energy efficient chip architectures.<sup>38</sup> In addition, Intel has said 82 percent of its energy in 2020 came from green sources such as solar and geothermal.39

Climate change has also harmed semiconductor production around the globe, adding to supply chain delays. For example, in February 2020, a cold snap in Texas created power outages that severely impacted semiconductor manufacturing in the state, leading to a months-long backup in production. 40 Producing chips also requires a lot of water, and severe drought in Taiwan has added to production delays.41

<sup>35 &</sup>quot;Mineral Commodity Summaries 2020," <u>U.S. Geological Survey</u>, January 2020; "Index of Semiconductor Process

Gases," <u>National Institute of Standards and Technology</u>, accessed November 2021.

36 John VerWey, "No Permits, No Fabs: The Importance of Regulatory Reform for Semiconductor Manufacturing," Georgetown Center for Security and Emerging Technologies, October 2021.

37 Alex Crawford et al., "The Chip Industry Has a Problem With Its Giant Carbon Footprint," Bloomberg, April

<sup>2021</sup>

<sup>38 &</sup>quot;Energy Efficient Computing: from Devices to Architecture," <u>Semiconductor Research Corporation</u>, 2021.

<sup>&</sup>lt;sup>39</sup> Sam Shead, "The global chip industry has a colossal problem with carbon emissions," <u>CNBC</u>. November 3, 2021. <sup>40</sup> Wu et al., "Why the World Is Short of Computer Chips, and Why It Matters."

<sup>&</sup>lt;sup>41</sup> Emanuela Barbiroglio, "No Water No Microchips: What Is Happening In Taiwan?" *Forbes,* May 31, 2021.

Chairwoman JOHNSON. The hearing will come to order. Without objection, the Chair is authorized to declare recess at any time.

Before I deliver my opening remarks, I wanted to note today that the Committee is meeting virtually. I want to announce a couple of reminders to Members about the conduct of this hearing. First, Members should keep their video feed on as long as they are present in the meeting. Members are responsible for their own microphones. Please also keep your microphones muted until you are speaking. And finally, if Members have documents they wish to submit for the record, please email them to the Committee Clerk, whose email address was circulated prior to the hearing.

Welcome to today's hearing, and welcome to our distinguished panel of witnesses. I look forward to hearing your insights on how we can ensure the United States' leadership in microelectronics.

It wasn't news to the experts, but the last 2 years have brought into full public view the vulnerabilities in our microelectronics supply chains. Chips operate almost every piece of technology in our lives, from cell phones to cars. They are essential to our national security. Yet, the U.S. share of global semiconductor manufacturing decreased from 37 percent in 1990 to just 12 percent today. Hindsight allows us to see that our government and industry suffered a collective failure of imagination when we thought we could offshore our chips manufacturing capacity without consequences. Today, a single chip might go through 1,000 production steps in 70 countries before reaching its final product. It took a global pandemic to expose the weaknesses of that approach. But we should not be fooled that this is a once-in-a-100-year problem.

Fortunately, the semiconductor industry still leads the world in research and innovation. In 1954, the very first commercial silicon transistor was developed by Gordon Teal at Texas Instruments (TI) in Dallas, Texas. In 1958, Jack Kilby of TI invented the integrated circuit (IC). And ever since then, because of investments by both the U.S. Government and industry, we continue to lead in micro-

electronics innovation.

However, current technology is approaching certain physical limits. Long-term growth will require breakthroughs in everything from fundamental materials science to manufacturing processes. In the meantime, other countries are stepping up their investments. In particular, China is already outspending the United States to bolster its domestic semiconductor capacity. Moreover, they're investing in research and innovation like they never did before. They no longer want to just manufacture yesterday's chip. They want to lead in innovating tomorrow's chip. That poses both an economic and national security risk to us.

To help maintain U.S. competitiveness in microelectronics, Congress passed the CHIPS for America Act. The CHIPS Act would make substantial investments in the future of semiconductor R&D (research and development). The act also includes incentives to

bring semiconductor manufacturing back to our shores.

I support full funding for the *CHIPS Act*. However, a one-time infusion of funding will not be enough to maintain U.S. leadership in microelectronics innovation. Advancing U.S. leadership in microelectronics will require a long-term, whole-of-government strategy. While incentives to re-shore capacity now are important, the future

will be shaped by how we invest in innovation and the technical work force. That is what we know and do best in this Committee. The Science, Space, and Technology Committee is ready to work with the Administration, industry, and the research community to oversee the implementation of the CHIPS Act.

In addition, we will continue to explore opportunities to strengthen and expand our investments in microelectronics research, including at the Department of Energy (DOE). This hearing is the beginning of a long-term effort by our Committee.

I thank you to the expert witnesses that are here today, and I

look forward to the discussion.

[The prepared statement of Chairwoman Johnson follows:]

Good morning and welcome to today's hearing. And welcome to our distinguished panel of witnesses. I look forward to hearing your insights on how we can ensure United States leadership in microelectronics.

It wasn't news to the experts, but the last 2 years have brought into full public view the vulnerabilities in our microelectronics supply chains. Chips operate almost every piece of technology in our lives, from cell phones to cars. They are essential to our national security. Yet, the U.S. share of global semiconductor manufacturing decreased from 37 percent in 1990 to just 12 percent today. Hindsight allows us to see that our government and industry suffered a collective failure of imagination when we thought we could offshore our chips manufacturing capacity without consequence. Today, a single chip might go through 1,000 production steps in 70 countries before reaching its final product. It took a global pandemic to expose the weaknesses of that approach. But we should not be fooled that this is a once-in-a-hundred-year problem.

Fortunately, the U.S. semiconductor industry still leads the world in research and innovation. In 1954, the very first commercial silicon transistor was developed by Gordon Teal at Texas Instruments in Dallas TX. In 1958, Jack Kilby of TI invented the integrated circuit. And ever since then, because of investments by both the U.S. government and industry, we have continued to lead in microelectronics innovation. However, current technology is approaching certain physical limits. Long term growth will require breakthroughs in everything from fundamental materials science to manufacturing processes.

In the meantime, other countries are stepping up their investments. In particular, China is already outspending the United States to bolster its domestic semiconductor capacity. Moreover, they are investing in research and innovation like they never did before. They no longer want to just manufacture yesterday's chip. They want to lead in innovating tomorrow's chip. That poses both an economic and national security risk to us.

To help maintain U.S. competitiveness in microelectronics, Congress passed the CHIPS for America Act. The CHIPS Act would make substantial investments in the future of semiconductor R&D. The Act also includes incentives to bring semiconductor manufacturing back to our shores. I support full funding for the CHIPS Act. However, a one-time infusion of funding will not be enough to maintain U.S. leader-

ship in microelectronics innovation.

Advancing U.S. leadership in microelectronics will require a long-term, whole of government strategy. While incentives to re-shore capacity now are important, the future will be shaped by how we invest in innovation and the technical workforce. That is what we know and do best in this Committee. The Science, Space, and Technology Committee is ready to work with the administration, industry, and the research community to oversee the implementation of the CHIPs Act. In addition, we will continue to explore opportunities to strengthen and expand our investments in microelectronics research, including at the Department of Energy. This hearing is the beginning of a long-term effort by our Committee.

Thank you again to the expert witnesses before us today. I look forward to the

With that, I now recognize Ranking Member Lucas for his opening statement.

Chairwoman Johnson. The Chair now recognizes Mr. Lucas for his opening statement.

Mr. Lucas. Thank you, Chairwoman Johnson, for holding this morning's hearing.

Every American who has tried to buy a car, tractor, or even a refrigerator lately, knows that we're facing severe supply chain shortages. In many cases, these shortages are being driven by global disruption to the supply chain for semiconductors or chips, as many of us refer to them.

Microelectronics, the devices made from semiconductor materials, are critical to how we live and work. They power phones, make our cars safer, our homes smarter, and help us store and protect virtual information. It is also vital to us. They are not only essential

to our economic security but our national security as well.

The Chinese Communist Party (CCP) has made it clear that it wants to dominate the globe in key technology areas, and part of their technology strategy is to increase China's share of the semiconductor market through both investment and acquisition. U.S. technology companies obtain as much as 90 percent of their semiconductor chips from Taiwan, a huge risk given the geopolitical sit-

uation in the region.

Microelectronics are necessary for the technologies of the future. Harnessing new applications such as artificial intelligence, 5G, and quantum sciences, will require fundamental breakthroughs in microelectronics technology. While the factors that led to today's chip shortage are worthy of their own examination, our focus today is forward-looking: How do we secure America's leadership in advanced chip design? How do we regain our leadership in semiconductor manufacturing? We must answer these questions to ensure we never face a chip shortage or disruption in the United States again.

Congress took the first steps to address this issue last year by passing the CHIPS for America Act as a part of the Fiscal Year 2021 National Defense Authorization Act. The CHIPS Act, which, when introduced, was referred solely to the Science Committee for jurisdiction, authorized programs to advance U.S. research and development, promote industry, government partnerships, and incentivize domestic fabrication of chips.

Today's hearing should provide critical guidance as Congress and the Administration consider how to implement and fund the CHIPS Act. I have no doubt this will be a major legislative and

oversight priority for our Committee for years to come.

To lead in advanced microelectronics, the United States will need to make strategic investments along the entire innovation pipeline, from fundamental research and education, to design, to manufacturing. The Federal Government has a long tradition of investing in fundamental research for microelectronics, including through academic research institutions and Federal laboratories that are supported by the National Science Foundation (NSF), the Department of Energy, and the National Institute for Standards and Technology (NIST).

Dr. Witherell will help tell us how DOE and its laboratories have worked with industry and academia to drive scientific advancements in areas such as materials science, energy efficiency, and novel devices. Access to materials, including critical minerals, chemicals, and gases will be the key to increasing domestic technology production. Unfortunately, the United States has limited quantities of many of these critical materials, so research into alternative and manufactured materials could be the answer to domestically producing advanced semiconductors.

Another challenge, which the *CHIPS Act* takes steps to address, is advanced packaging. Experts believe that breakthroughs in packaging will be key to improving chip efficiency beyond the regular doubling of computing capabilities predicted by Moore's Law. I look forward to hearing from our witnesses today about what will make a national advanced packaging manufacturing program successful.

Developing a strong work force in the United States to support the microelectronics industry is another challenge we need to solve. In the next 5 years, companies estimate that we'll need at least 42,000 semiconductor engineers nationwide. That demand is even higher for the full spectrum of workers needed, from skilled technicians and operators with associate degrees to those with advanced degrees. I hope our witnesses will provide some recommendations on how we can build this work force.

As Congress looks to strengthen U.S. chip manufacturing and advance our competitiveness in microelectronics, we must look to lessons from the past. We've been here before. In the 1980's, the Federal Government took strong actions to combat Japan's dominance in microelectronics. They included establishing a research consortium to support U.S. competitiveness in semiconductor technology, also known as SEMATECH. This government-industry partnership lasted until 1994. It helped the United States regain the lead for a time, but competing industry interests, waning government support, and other factors led to a decline that has put us where we are today.

During this time, IMEC was also established and is still in operation today. IMEC has created an international ecosystem for more than 600 world-leading industry partners and a global academic network focused on developing and testing cutting-edge semiconductor innovations. I know several of our witnesses have worked with both consortiums, and I look forward to hearing what lessons can be taken from each and used to inform the establishment of a National Semiconductor Technology Center (NSTC) and the De-

partment of Defense's microelectronics commons.

In closing, I'd like to note that yesterday marked 2 weeks since the Democratic leaders of the House and Senate announced that there would be a conference on the Senate-passed *U.S. Innovation and Competition Act, (USICA)* and the innovation bills that our Committee carefully crafted and passed on a bipartisan basis. Unfortunately, we're still waiting on the details of that conference. Chairwoman Johnson and I are ready to go. We've been ready to go for months. It's time for leadership to move forward on a bipartisan conference of all of the Committees of jurisdiction.

The Senate bill will include significant funding for the *CHIPS Act*. And while I think there are still details to be worked out on exactly how that funding should look, time is in short supply to address our future domestic chip needs. We need to act now because

I can tell you that our competitors aren't waiting.

No matter what the final vehicle is for funding the *CHIPS Act*, I look forward to working with my colleagues to get it done as soon as possible.

Thank you, Chairwoman Johnson, and I yield back the balance of my time.

[The prepared statement of Mr. Lucas follows:]

Thank you, Chairwoman Johnson, for holding this morning's hearing.

Every American who has tried to buy a car, tractor, or even a refrigerator lately, knows that we are facing severe supply chain shortages. In many cases, these shortages are being driven by global disruption to the supply chain for semiconductors

Microelectronics, the devices made from semiconductor materials, are critical to how we live and work. They power our phones, make our cars safer, our homes smarter, and help us store and protect vital information. They are not only essential

to our economic security but our national security as well.

The Chinese Communist Party (CCP) has made it clear that it wants to dominate the globe in key technology areas, and part of their strategy is to increase China's share of the semiconductor market through both investment and acquisition. U.S. technology companies obtain as much as 90 percent of their semiconductor chips

from Taiwan, a huge risk given the geopolitical situation in the region.

Microelectronics are necessary for the technologies of the future. Harnessing new applications such as artificial intelligence, 5G, and quantum sciences, will require

fundamental breakthroughs in microelectronics technology.

While the factors that led to today's chip shortage are worthy of their own examination, our focus today is forward-looking—how do we secure America's leadership in advanced chip design and how do we regain our leadership in semiconductor manufacturing? We must answer these questions to ensure we never face a chip shortage or disruption in the United States again.

Congress took the first steps to address this issue last year by passing the CHIPS for America Act as part of the FY21 National Defense Authorization Act. The CHIPS Act—which when introduced was referred solely to the Science Committee for jurisdiction—authorized programs to advance U.S. research and development, promote industry and government partnerships, and incentivize domestic fabrication of

Today's hearing should provide critical guidance as Congress and the Administration consider how to implement and fund the CHIPS Act. I have no doubt this will be a major legislative and oversight priority for our Committee for years to come.

To lead in advanced microelectronics, the United States will need to make strategic investments along the entire innovation pipeline—from fundamental research and education, to design, to manufacturing. The federal government has a long tradition of investing in fundamental research for microelectronics, including through academic research institutions and federal laboratories that are supported by the National Science Foundation (NSF), Department of Energy (DOE), and the National Institute for Standards and Technology (NIST).

Dr. Witherell will tell us how DOE and its laboratories have worked with industry

and academia to drive scientific advancements in areas such as materials science, energy efficiency, and novel devices. Access to materials, including critical minerals, chemicals, and gasses will be a key to increasing domestic technology production.

Unfortunately, the U.S. has limited quantities of many of these critical materials.

So research into alternative and manufactured materials could be the answer to do-

mestically producing advanced semiconductors. Another challenge, which the  $C\!HIPS$  Act takes steps to address, is advanced packaging. Experts believe that breakthroughs in packaging will be key to improving chip efficiency beyond the regular doubling of computing capabilities predicted by Moore's law. I look forward to hearing from our witnesses today about what will

make a national advanced packaging manufacturing program successful.

Developing a strong workforce in the United States to support the microelectronics industry is another challenge we need to solve. In the next five years, companies estimate that we will need at least 42,000 semiconductor engineers nationwide. That demand is even higher for the full spectrum of workers needed—from skilled technicians and operators with associate degrees to those with advanced degrees. I hope our witnesses will provide some recommendations on how we can build this workforce.

As Congress looks to strengthen U.S. chip manufacturing and advance our competitiveness in microelectronics, we must look to lessons from the past. We've been here before. In the 1980s, the federal government took strong actions to combat Japan's dominance in microelectronics. This included establishing a research consortium to support U.S competitiveness in semiconductor technology, also known as SEMATECH. This government-industry partnership lasted until 1994. It helped the U.S. regain the lead for a time, but competing industry interests, waning government support, and other factors led to a decline that put us where we are today.

Chairwoman JOHNSON. Thank you very much.

If there are Members who wish to submit additional opening statements, your statements will be added to the record at this point.

At this time I'd like to introduce our witnesses. Our first witness

will be introduced by Ms. Bonamici.

Ms. Bonamici. Thank you so much, Chairwoman Johnson. It is my pleasure to introduce Dr. Ann Kelleher, Executive Vice President and General Manager of Technology Development at Intel Corporation, which has several hubs or campuses in the district I represent, and employs more than 20,000 Oregonians. Dr. Kelleher is responsible for the research, development, and deployment of next-generation silicon logic, packaging, and test technologies that power the future of Intel's innovation.

Previously, Dr. Kelleher was the General Manager of Manufacturing and Operations where she oversaw Intel's worldwide manufacturing operations, as well as corporate quality assurance and corporate services. Dr. Kelleher joined Intel in 1996 as a Process Engineer and has tremendous expertise to offer as a witness in this hearing. I want to thank her for being here with us this morning

and look forward to her testimony.

Thank you, Madam Chair, and I yield back.

Chairwoman JOHNSON. Thank you very much. Our next witness is Mr. Manish Bhatia. He is the Executive Vice President of Global Operations at Micron Technology. In this role, he is responsible for driving the vision and direction for Micron's end-to-end operations. Prior to joining Micron in 2017, he served as Executive Vice President of Silicon Operations at Western Digital Corporation. He also served as Executive Vice President of Worldwide Operations at SanDisk Corporation when it was acquired by Western Digital.

Our third witness is Dr. Michael Witherell. He is the Director of Lawrence Berkeley National Laboratory (LBNL), a position he has held since January of 2016. Prior to his position at Berkeley, he served as the Vice Chancellor of Research at the University of California, Santa Barbara from 2005 to 2016 and was the Director of Fermi National Accelerator Laboratory from 1999 to 2005. He is a member of the National Academy of Sciences and a Fellow of the American Physical Society and American Association for the Advancement of Science.

Our final witness—somebody——

STAFF. Dr. Baird.

Chairwoman JOHNSON. Dr. Baird will introduce. Dr. Baird,

you're recognized.

Mr. BAIRD. Thank you, Madam Chair. And it's indeed my pleasure to introduce to you an individual from Indiana's Fourth Congressional District and Purdue University. Dr. Mung Chiang currently serves as the Executive Vice President of Purdue University for Strategic Initiatives, the John A. Edwardson Dean College of Engineering, and the Roscoe H. George Distinguished Professor in the Elmore Family School of Electrical and Computer Engineering. Dr. Chiang's research on communication networks received a 2013

Alan T. Waterman Award, the highest honor to scientists and engineers under the age of 40 in the United States. And he has been

the recipient of several other awards and distinctions.

Most recently, Dr. Chiang founded the Center for Tech Diplomacy at Purdue, which intends to bring engineering expertise to policymakers in a way that demonstrates the inextricable links between technology, technology advancements, and national interests.

So, Dr. Chiang, we are very happy to have you here with us today, and we really look forward to your testimony. Thank you.

I yield back.

Chairwoman JOHNSON. Thank you very much.

As our witnesses should know, you will each have 5 minutes for your spoken testimony. Your written testimony will be included in the record for the hearing. When you have completed your spoken testimony, we will begin with questions. Each Member will have 5 minutes to question the panel.

We now will start with Dr. Kelleher.

#### TESTIMONY OF DR. ANN KELLEHER, EXECUTIVE VICE PRESIDENT AND GENERAL MANAGER OF TECHNOLOGY DEVELOPMENT, INTEL

Dr. Kelleher. Chairwoman Johnson, Ranking Member Lucas, and Members of the Committee, thank you for inviting me to testify today. I lead Technology Development at Intel where we research and develop process and packaging technologies for Intel's products. We also ramp this technology into high-volume manufacturing.

Over the past 10 years, Intel has invested more than \$75 billion in process and packaging R&D and U.S. manufacturing capital. Over the next 10 years, Intel anticipates spending approximately \$150 billion. This will cover our recently announced expansions in Arizona, New Mexico, and a U.S. greenfield site, as well as our future technology R&D.

Intel's investments demonstrate our enduring commitment to the United States technology leadership where we conduct all of our process technology R&D and the majority of our manufacturing.

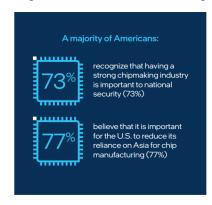

Semiconductors are fundamental to U.S. technology leadership, our economy, and our national security, and we're the fourth-largest U.S. export sector in 2020. Recent supply chain disruptions due to COVID-19 and widespread chip shortages illustrate the risk to our economy and the danger of losing our ability to make leading-edge chips in the United States.

Āmerica has lost significant share of semiconductor production to Asia over the last 30 years. For decades, countries in Asia have provided substantial incentives driving a 30 percent cost disadvantage for chipmaking in the United States and a corresponding decrease in the U.S. global share of manufacturing, and that dropped

from 37 percent to 12 percent.

At the same time, designing and manufacturing leading-edge chips has also become increasingly more expensive. A recent paper from Boston Consulting Group highlighted the fact that investments required to develop the next advance in chipmaking has grown 40-fold over the last 20 years. Due to this dramatic increase, fewer manufacturers globally are able to make the investment re-

quired to develop leading-edge semiconductor technologies. In 2000, more than 25 companies built leading-edge chips, but today only three leading-edge manufacturers of logic technology remain, and

Intel is the only one left in the United States.

Three essential ingredients are necessary for a strong U.S. semi-conductor industry: manufacturing process technology, including IP (intellectual property) and know-how based in the United States; U.S. fab capacity to support the growing demand in the United States and worldwide; and advanced packaging capability and capacity. But these essential elements are being challenged by the 30 percent cost disadvantage and the lack of public funding for R&D.

Forty years ago, Federal investment in semiconductor R&D was more than double that of private investment, but today, U.S. private investment is nearly 20 times that of public funding. Federal investments is urgently needed to level the playing field and re-

verse the erosion of U.S. semiconductor industry.

Congress must enact funding of the new semiconductor manufacturing and R&D programs created in the *CHIPS for America Act* as soon as possible. The *CHIPS Act* has the right framework to create a strong U.S. semiconductor industry, and I'm confident that, if funded in a robust and sustained manner, these programs will significantly contribute to American technology leadership. Once funded, the Federal Government will need to effectively implement the *CHIPS Act* most significant new R&D program, the National Semiconductor Technology Center, or NSTC, and the National Advanced Packaging Manufacturing Program.

For the NSTC, Intel recommends priority R&D—prioritizing R&D on future breakthrough challenges that align with industry goals, leveraging existing industry infrastructure to save time and reduce cost. NSTC should be led by a neutral nonprofit that can

reconcile conflicting needs in the industry.

For the packaging program, Intel recommends establishing a physical location for the participants to work together to develop leading-edge cost-effective packaging technologies in the United States. The program should encompass packaging integration efforts across the semiconductor ecosystem.

The Committee has an important oversight role regarding the *CHIPS Act* program, and Intel looks forward to working with you to provide our perspective on how to effectively implement these programs. Thank you for holding this stakeholder hearing, and I look forward to answering your questions.

[The prepared statement of Dr. Kelleher follows:]

#### House Committee on Science, Space, and Technology

#### "Ensuring American Leadership in Microelectronics"

#### Testimony of Dr. Ann Kelleher

#### **Executive Vice President & General Manager, Technology Development, Intel Corporation**

#### December 2, 2021

Chairwoman Johnson, Ranking Member Lucas, and members of the Committee, thank you for inviting me to testify about the status of advanced semiconductor development and manufacturing in the United States, and to share my perspective about new federal investment and public-partnerships to support U.S. leadership in semiconductor innovation and manufacturing throughout the supply chain.

I am the Executive Vice President and General Manager of Technology Development at Intel Corporation, which is the group at Intel dedicated to advancing Moore's Law by creating new transistor architectures, wafer, and packaging processes that we turn into products for the personal computers and cloud infrastructure we are using to safely conduct this hearing, as well as for emerging technologies like 5G networks, artificial intelligence (AI), Internet of Things (IoT), and quantum computing.

Semiconductors are fundamental to U.S. technology leadership, our economy, and national security. They represent the fourth largest U.S. export sector, and the pandemic has only accelerated the adoption of digital infrastructure powered by semiconductors. Recent supply chain disruptions due to COVID-19 and widespread chip shortages illustrate the risks to our economy and the danger of losing our ability to make advanced chips in the United States.

Yet America has lost significant share of semiconductor production to Asia over the last 30 years. For decades, countries in Asia have provided substantial incentives to build domestic semiconductor champions, driving a 30 percent cost disadvantage for chipmaking in the U.S. and a corresponding decrease in U.S. share of global chip manufacturing. Since 1990, that share has dropped from 37 percent to 12 percent, and it is projected to erode further to 9 percent by 2030.

Federal investment is urgently needed to reverse this erosion by leveling the playing field for America's semiconductor industry. Almost one year ago, Congress took a critical step by authorizing new semiconductor manufacturing and R&D programs through the CHIPS for America Act. In June, the Senate approved \$52 billion in appropriations for the CHIPS Act through the bipartisan U.S. Innovation and Competition Act. Now, Congress must finish the job by enacting CHIPS funding as soon as possible. Intel is doing its part to invest in American leadership by conducting the majority of our R&D and manufacturing in the United States, and we look forward to partnering with the federal government through the CHIPS Act programs to enhance domestic semiconductor R&D and manufacturing.

As the only U.S. semiconductor company with the depth and breadth of intelligent silicon, platform, software, architecture, design, manufacturing, and scale, as well as innovation and leading-edge manufacturing capabilities here in the U.S., Intel is uniquely positioned to help the U.S. regain leadership.

1

#### **Executive Summary**

A November 2021 paper from the Boston Consulting Group (BCG) identified the three essential ingredients for a strong U.S. semiconductor industry: i) manufacturing process technology, including intellectual property (IP) and know-how based in the United States; (ii) U.S. fab capacity to support growing demand in the U.S. and worldwide, and (iii) advanced packaging capability and capacity. BCG also identified the two most significant gaps currently facing the United States in establishing those three ingredients: (i) a 30 percent or more cost disadvantage with East Asia that U.S. chipmakers face; and (ii) public funding for R&D, which lags both Taiwan and Korea where the most advanced semiconductors are currently manufactured. Forty years ago, federal investment in semiconductor R&D was more than double that of private investment, but today, U.S. private investment is nearly twenty times that of public funding.

The U.S. government will need to effectively leverage funding from the CHIPS Act that will be allocated to new and existing R&D programs to ensure we achieve and maintain American technology leadership. To do so, the government should take an inventory of existing federal R&D programs and partnerships with private industry to identify the critical technology gaps, and with the help of the Industrial Advisory Committee established pursuant to the CHIPS Act, determine how best to fill those gaps by using existing infrastructure in combination with new resources. These efforts should be part of developing a national semiconductor strategy and technology roadmap. The two most significant new R&D programs under the CHIPS Act are the National Semiconductor Technology Center (NSTC) and the National Advanced Packaging Manufacturing Program (NAPMP).

- NSTC. Intel recommends the NSTC prioritize R&D on future breakthrough challenges that align

with industry goals, and leverage existing industry infrastructure to save time and cost. NSTC

should be led by a neutral non-profit that can reconcile conflicting views, such as around IP

policy.

- NAPMP. High-performance chips rely heavily on advanced packaging technology, and that

reliance coupled with the current worldwide capacity constraints, has highlighted the need for

self-sufficient domestic packaging infrastructure. The NAPMP should establish a Package

Research Center (or Centers) that allow for packaging integration combining all the different

parts together to develop and demonstrate a complete solution that improves chip performance

and reduces its size.

The CHIPS Act has the right provisions to create a strong U.S. semiconductor industry, and we have confidence that if funded in a robust and sustained manner, these programs will significantly increase supply chain resiliency and contribute to American technology leadership.

#### Background

Intel Corporation is the world's largest semiconductor manufacturer, <sup>1</sup> employing over 110,000 people globally and approximately 53,000 in the United States. Intel is headquartered in Santa Clara, California and has innovation hubs in Oregon, Arizona, California, New Mexico, and Texas. Intel builds most of its product designs within its own leading-edge manufacturing and advanced packaging network, and offers foundry services for fabless chip design companies. Intel invested around \$33 billion in capital expenditures and \$27 billion in R&D from 2019-2021, the majority of which is conducted here in the United States. <sup>2</sup> Intel ranks sixth among publicly-traded U.S. companies in its individual R&D investment, and directly contributed almost \$26 billion to U.S. Gross Domestic Product (GDP) in 2019, with a total GDP impact to the U.S. economy of \$102 billion.<sup>3</sup>

Intel is making unprecedented new investments in U.S. semiconductor manufacturing capacity. Earlier this year, we announced plans to invest \$20 billion in the construction of two new fabrication facilities in Arizona, <sup>4</sup> and to invest \$3.5 billion in our New Mexico facility for the manufacturing of advanced semiconductor packaging technologies. <sup>5</sup> We also have announced our intention to select a new U.S. greenfield site worth up to \$100 billion in investment over the next decade. These plans demonstrate Intel's ongoing commitment to leadership investments in R&D and capital expenditures in the United States, investments that enhance U.S. technological leadership and ultimately U.S. national and economic security.

Each job at Intel is estimated to support up to 13 other jobs elsewhere, meaning Intel directly or indirectly supports more than 700,000 full-time and part-time jobs in the United States. Our workforce is highly educated with approximately 90 percent of people working in STEM related professions. We employ many disciplines of technical experts including engineers, chemists, physicists, and mathematicians. In the United States Intel regularly hirse graduates with associate degrees, baccalaureate, master's and PhD's. In recent years on average Intel has hired over 150 students graduating from PhD programs, a significant proportion of the graduates in targeted fields across the country.

Intel is one of only three semiconductor manufacturers in the world making advanced semiconductors and the only one with its research and development anchored in the United States. The semiconductor products that Intel manufactures provide the foundations for technologies ranging from personal computing, cloud computing, artificial intelligence (AI), Internet of Things (IoT), 5G, autonomous vehicles, quantum computing, to high-performance-compute solutions, that advance humanity's understanding of, and response to, society's most pressing challenges.

<sup>&</sup>lt;sup>1</sup> See IBISWorld Industry Report 33441a, "Semiconductor and Circuit Manufacturing in the US," June 2020.

<sup>&</sup>lt;sup>2</sup> See <a href="https://www.intel.com/content/www/us/en/newsroom/news/us-economic-impact-study.html#gs.0juavq.">https://www.intel.com/content/www/us/en/newsroom/news/us-economic-impact-study.html#gs.0juavq.</a>

<sup>\*\*</sup> See https://www.intel.com/content/www/us/en/newsroom/news/idm-manufacturing-innovation-product-leadership.html#gs.zog0za.

<sup>&</sup>lt;sup>5</sup> See <a href="https://www.intel.com/content/www/us/en/newsroom/news/new-mexico-manufacturing.html#gs.0i5sdw">https://www.intel.com/content/www/us/en/newsroom/news/new-mexico-manufacturing.html#gs.0i5sdw</a>.

<sup>&</sup>lt;sup>6</sup> See https://www.intel.com/content/www/us/en/newsroom/news/us-economic-impact-study.html#gs.0juavq.

#### **Technology Development at Intel**

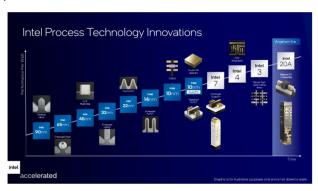

I lead Intel's Technology Development organization, which creates the baseline technology underpinning Intel's products and the manufacturing technology required to bring innovations into the physical world. This team's work resulted in an average of over 1,000 US patents filled per year over the last several years. I will provide a brief overview of the major teams and our process technology roadman

Components Research invents, develops, and demonstrates viable revolutionary and game-changing process and packaging technology options for enabling Moore's Law extension and Intel product differentiation. They then transfer those innovations and enabling technologies to other Technology Development organizations for their use in manufacturing development. This team also champions and directs over 200 university research projects annually.

Logic Technology Development is widely recognized as one of the preeminent silicon process engineering organizations in the world, consisting of approximately 8,000 employees based primarily in Hillsboro, Oregon. It produces the 'heart' of Intel products, the transistor, that is used to build a microprocessor. To maintain a predictable Moore's Law driven cadence of silicon products, at any given time, approximately four to five logic process technologies are in various stages of the development cycle, from Pathfinding to Deployment. In addition, based on strategic direction or specific product needs, two to three specialty process flows, such as advanced memory or analog/RF processes, are typically in one of the development stages.

Our **Design Enablement Group** enables both internal and external design teams to deliver winning products on Intel's cutting-edge technologies. They are responsible for delivering best-in-class Process Design Kits, which are Computer-Aided Design representations of the silicon technology to enable designs. This team also works closely with Logic Technology Development to optimize the transistor development, routing and tools, flow and methods to deliver best-in-class power, performance, and area for Intel's products. Lastly, they deliver foundational IP and test-chips and test vehicles which are a critical part of the technology development for yield and IP learning.

The **Assembly Test and Technology Development Group** is the world leader in advanced packaging technologies with a strong portfolio of 2.5D and 3D advanced packaging offerings. This team has substrate and assembly factories to develop leading edge packaging technologies. They create industry-leading known good die sort and test capability, and they offer package design services and silicon package co-design enablement and offer world-class board assembly.

#### Intel's Process Technology Roadmap

Earlier this year, I helped unveil one of the most detailed process technology roadmaps that Intel has ever provided, showcasing a new node naming system and breakthrough technologies that will power new products through 2025 and beyond, including:

- RibbonFET, our first new transistor architecture in more than a decade

- PowerVia, an industry-first new backside power delivery method

High NA EUV, our plans to adapt next-generation High Numerical Aperture extreme ultraviolet lithography

Intel's technology roadmap relies on new levels of innovation, including not only deep transistor-level enhancements, but also innovations all the way up the stack to the interconnect and standard cell level. The company has moved to an accelerated pace of innovation to enable an annual cadence of process improvements.

#### **Manufacturing at Intel**

While Intel conducts the majority of manufacturing in the United States, our global manufacturing scope and scale enable us to provide our customers with a broad range of leading-edge products. Integrated manufacturing has been foundational to our success, enabling product optimization, improved economics, and supply resilience. As semiconductor manufacturing becomes more complex, Intel is one of the few remaining firms in the world, and the only one in the United States, that can do both leading-edge design and manufacturing in-house.

Intel has nine global manufacturing sites—five for silicon wafer fabrication and four for the assembly and testing of our products. We operate in a network of manufacturing facilities integrated as one factory to provide the most flexible supply capacity. Our new process technologies are transferred identically from our central development fab in Oregon to each manufacturing facility. After transfer, the network of factories and the development fab collaborate to continue driving operational improvements. This enables fast ramp of the operation, fast learning, and better quality control.

#### Fab and Assembly/Test Sites

#### State of U.S. Semiconductor R&D and Manufacturing